# A Hardware Implementation of a Coherent SOQPSK-TG Demodulator for FEC Applications

by

Gino Pedro Enrique Rea Zanabria

Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science.

Thesis Committee:

Dr. Erik Perrins: Chairperson

Dr. Andrew Gill

Dr. Shannon Blunt

Date Defended

### The Thesis Committee for Gino P.E. Rea Zanabria certifies that this is the approved version of the following thesis:

### A Hardware Implementation of a Coherent SOQPSK-TG Demodulator for FEC Applications

Committee:

Chairperson

Date Approved

### Acknowledgements

First of all, I would like to thank my family for always supporting and encouraging me throughout this incredible journey. They have been there when I most needed them, and I know that without their love and guidance, none of this would have been possible. I would also like to thank Dr. Erik Perrins, my academic advisor, for giving me the opportunity to be part of his research team. His experience and knowledge in the field of wireless communications have been a source of inspiration throughout these years, and without a doubt, he will be a role model to follow in my professional life. Next, I would like to thank Dr. Andrew Gill and Dr. Shannon Blunt for taking the time to serve on my committee. I have a great respect for their work and, I am honored by having them on my committee. And last but not least, I would like to thank all the friends I made at KU for making this journey more fun, less stressful, and surely one I will never forget.

### Abstract

This thesis presents a hardware design of a coherent demodulator for *shaped* offset quadrature phase shift keying, telemetry group version (SOQPSK-TG) for use in forward error correction (FEC) applications. Implementation details for data sequence detection, symbol timing synchronization, carrier phase synchronization, and block recovery are described. This decision-directed demodulator is based on maximum likelihood principles, and is efficiently implemented by the soft output Viterbi algorithm (SOVA). The design is intended for use in a field-programmable gate array (FPGA). Simulation results of the demodulator's performance in the additive white Gaussian noise channel are compared with a Matlab reference model that is known to be correct. In addition, hardware-specific parameters are presented. Finally, suggestions for future work and improvements are discussed.

# Contents

| A            | ccept          | cance Page                                       | ii  |

|--------------|----------------|--------------------------------------------------|-----|

| A            | ckno           | wledgements                                      | iii |

| $\mathbf{A}$ | bstra          | let                                              | iv  |

| 1            | Intr           | roduction                                        | 1   |

|              | 1.1            | Background                                       | 1   |

|              | 1.2            | Objectives                                       | 2   |

|              | 1.3            | Organization                                     | 3   |

| <b>2</b>     | Des            | cription of SOQPSK                               | 4   |

|              | 2.1            | CPM Signal Model                                 | 4   |

|              | 2.2            | Frequency Pulse Truncation for SOQPSK-TG         | 7   |

|              | 2.3            | SOQPSK Precoders                                 | 8   |

|              |                | 2.3.1 Standard Precoder                          | 8   |

|              |                | 2.3.2 Recursive Precoder                         | 9   |

|              | 2.4            | Trellis Representation                           | 10  |

| 3            | Coc            | led SOQPSK Iterative Decoders                    | 12  |

|              | 3.1            | Serially Concatenated Convolutional Code Decoder | 12  |

|              | 3.2            | Low Density Parity Check Decoder                 | 14  |

| 4            | $\mathbf{Seq}$ | uence Detection for SOQPSK                       | 16  |

|              | 4.1            | Maximum Likelihood Sequence Detection            | 17  |

|              | 4.2            | SOVA Implementation                              | 19  |

| <b>5</b> | $\mathbf{Syn}$ | abol Timing Synchronization         | <b>24</b> |  |  |  |  |  |  |  |  |

|----------|----------------|-------------------------------------|-----------|--|--|--|--|--|--|--|--|

|          | 5.1            | Timing Error Detector               | 26        |  |  |  |  |  |  |  |  |

|          | 5.2            | Loop Filter                         | 27        |  |  |  |  |  |  |  |  |

|          | 5.3            | Interpolation                       | 28        |  |  |  |  |  |  |  |  |

|          | 5.4            | Interpolation Control               | 29        |  |  |  |  |  |  |  |  |

| 6        | Car            | rier Phase Synchronization          | 32        |  |  |  |  |  |  |  |  |

|          | 6.1            | Phase Error Detector                | 33        |  |  |  |  |  |  |  |  |

|          | 6.2            | Loop Filter                         | 35        |  |  |  |  |  |  |  |  |

|          | 6.3            | Voltage-Controlled Oscillator       |           |  |  |  |  |  |  |  |  |

|          | 6.4            | Phase Ambiguity Resolution          | 36        |  |  |  |  |  |  |  |  |

| 7        | Har            | dware Implementation                | 37        |  |  |  |  |  |  |  |  |

|          | 7.1            | Design Overview                     | 37        |  |  |  |  |  |  |  |  |

|          |                | 7.1.1 Inputs and Outputs            | 37        |  |  |  |  |  |  |  |  |

|          |                | 7.1.2 Sampling and Downconversion   | 40        |  |  |  |  |  |  |  |  |

|          |                | 7.1.3 Demodulator Structure         | 42        |  |  |  |  |  |  |  |  |

|          | 7.2            | Interpolator                        | 45        |  |  |  |  |  |  |  |  |

|          | 7.3            | Timing Estimator                    | 47        |  |  |  |  |  |  |  |  |

|          |                | 7.3.1 Timing Loop Filter            | 47        |  |  |  |  |  |  |  |  |

|          |                | 7.3.2 Modulo-1 Decrementing Counter | 48        |  |  |  |  |  |  |  |  |

|          | 7.4            | Phase Corrector                     |           |  |  |  |  |  |  |  |  |

|          | 7.5            | Phase Estimator                     | 54        |  |  |  |  |  |  |  |  |

|          |                | 7.5.1 Phase Loop Filter             | 54        |  |  |  |  |  |  |  |  |

|          |                | 7.5.2 Voltage Controlled Oscillator | 55        |  |  |  |  |  |  |  |  |

|          | 7.6            | MFs Bank                            | 57        |  |  |  |  |  |  |  |  |

|          | 7.7            | SOVA                                | 62        |  |  |  |  |  |  |  |  |

|          |                | 7.7.1 Branch Increment Calculator   | 65        |  |  |  |  |  |  |  |  |

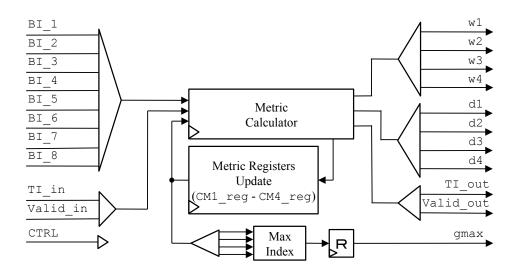

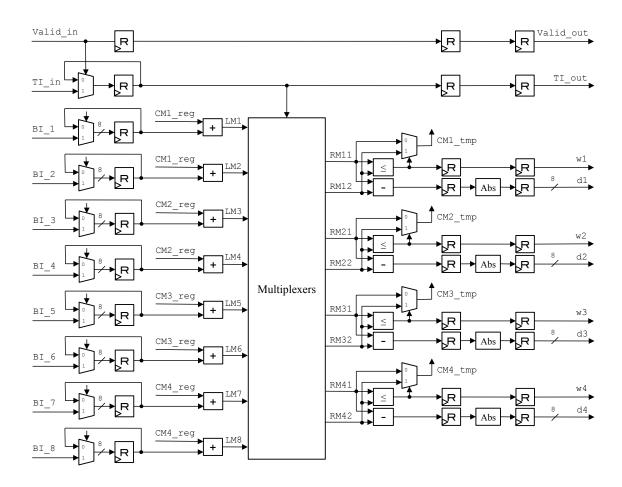

|          |                | 7.7.2 Metric Manager                | 67        |  |  |  |  |  |  |  |  |

|          |                | 7.7.3 Hard-Decision Traceback Unit  | 71        |  |  |  |  |  |  |  |  |

|          |                | 7.7.4 Reliability Traceback Unit    | 74        |  |  |  |  |  |  |  |  |

|          |                | 7.7.5 Output Calculator             | 77        |  |  |  |  |  |  |  |  |

|          | 7.8            | TED                                 | 79        |  |  |  |  |  |  |  |  |

|          | 7.9            | PED                                 | 85        |  |  |  |  |  |  |  |  |

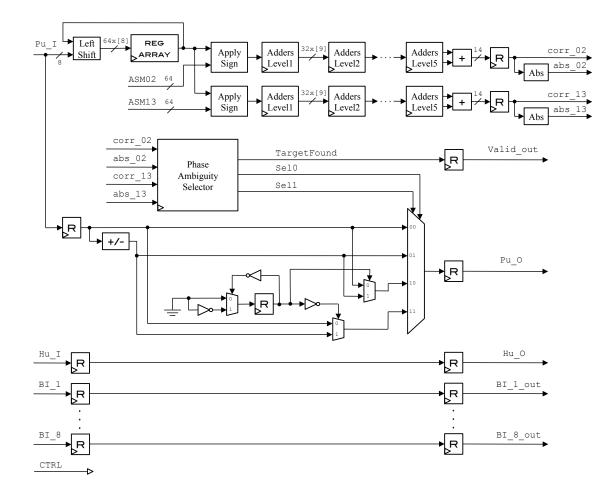

|   | 7.10  | Soft-Decision Correlator  | 91  |

|---|-------|---------------------------|-----|

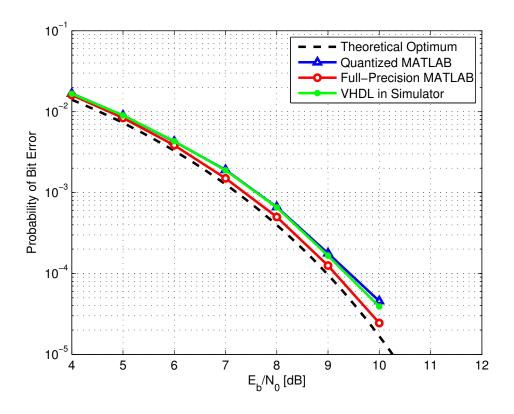

| 8 | Per   | formance Results          | 95  |

|   | 8.1   | BER Performance           | 95  |

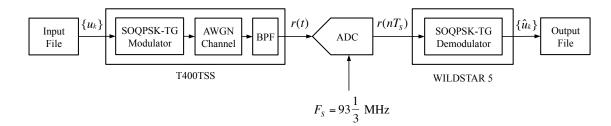

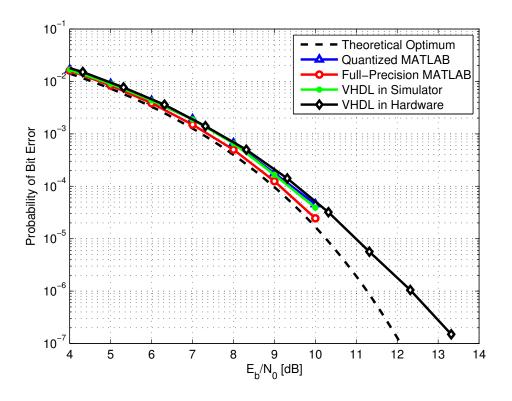

|   | 8.2   | Hardware Performance      | 100 |

| 9 | Cor   | nclusion                  | 101 |

|   | 9.1   | Interpretation of Results | 101 |

|   | 9.2   | Future Work               | 102 |

| R | efere | nces                      | 103 |

# List of Figures

| 2.1 | Length-8 $T$ frequency pulse and corresponding phase pulse for SOQPSK   | -  |

|-----|-------------------------------------------------------------------------|----|

|     | TG                                                                      | 6  |

| 2.2 | Signal model for uncoded SOQPSK                                         | 8  |

| 2.3 | Four-state time-varying trellis. The labels above each branch are for   |    |

|     | the standard precoder in $(2.8)$ , while the labels below each branch   |    |

|     | are for the recursive precoder in $(2.10)$ . The branch labels indicate |    |

|     | the input-bit/output-symbol pair $u_k/lpha_k$                           | 10 |

| 2.4 | Mapping between the trellis state variable pairs $S_k$ and the CPM      |    |

|     | phase states $\theta_k$                                                 | 11 |

| 3.1 | Block diagram of a serially concatenated convolutional code decoder.    | 13 |

| 3.2 | Block diagram of a concatenated low density parity check decoder.       | 14 |

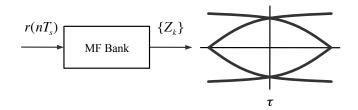

| 4.1 | Discrete-time approach to MLSD for SOQPSK                               | 18 |

| 4.2 | Block diagram of the soft output Viterbi algorithm                      | 19 |

| 4.3 | Illustration of the metric update process                               | 21 |

| 5.1 | Eye diagram showing the optimum sampling instant for the MF             |    |

|     | outputs.                                                                | 24 |

| 5.2 | A discrete-time approach to symbol timing synchronization for SO-       |    |

|     | QPSK                                                                    | 25 |

| 5.3 | A block diagram of the simple gain loop filter $F(s)$                   | 27 |

| 5.4 | Illustration of the interpolation operation to achieve optimum sam-     |    |

|     | pling instants. Available samples before interpolation are repre-       |    |

|     | sented with a triangle, while available samples after interpolation     |    |

|     | are represented with a circle                                           | 28 |

| 5.5  | A block diagram of the timing synchronizer with the modulo-1            |    |

|------|-------------------------------------------------------------------------|----|

|      | decrementing counter used for interpolation control                     | 30 |

| 5.6  | Illustration of the modulo-1 decrementing counter underflowing ev-      |    |

|      | ery N samples. In this example, N assumes the value of 4. $\ldots$      | 31 |

| 6.1  | A discrete-time approach to phase synchronization for SOQPSK            | 33 |

| 6.2  | A block diagram of the simple gain loop filter $F(s)$                   | 35 |

| 6.3  | A block diagram representation of the voltage-controlled oscillator     |    |

|      | (VCO)                                                                   | 35 |

| 6.4  | Block diagram representation of phase ambiguity resolution for SO-      |    |

|      | QPSK                                                                    | 36 |

| 7.1  | A black box view of the full version of the SOQPSK-TG demodulator.      | 38 |

| 7.2  | A black box view of the simple version of the SOQPSK-TG demod-          |    |

|      | ulator                                                                  | 39 |

| 7.3  | Block diagram representation of signal sampling and $\rm I/Q$ downcon-  |    |

|      | version.                                                                | 40 |

| 7.4  | Internal structure of the demodulator.                                  | 42 |

| 7.5  | Internal structure of the demodulator core                              | 43 |

| 7.6  | Hardware representation of the interpolator                             | 46 |

| 7.7  | Block diagram of the timing estimator                                   | 47 |

| 7.8  | Hardware representation of the timing loop filter                       | 48 |

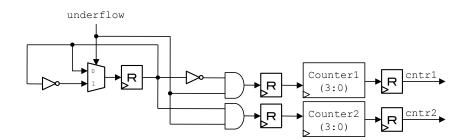

| 7.9  | Hardware representation of the mod-1 decrementing counter               | 50 |

| 7.10 | Hardware representation of the phase corrector                          | 52 |

| 7.11 | Hardware representation of the complex multiplier                       | 53 |

| 7.12 | Block diagram of the phase estimator.                                   | 54 |

| 7.13 | Hardware representation of the phase loop filter                        | 55 |

| 7.14 | Hardware representation of the voltage-controlled oscillator. $\ . \ .$ | 56 |

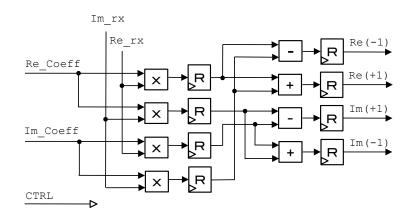

| 7.15 | Hardware representation of the matched-filters bank                     | 58 |

| 7.16 | Hardware representation of the MFs LUT control system                   | 59 |

| 7.17 | Hardware representation of the MFs complex multiplier. $\ldots$ .       | 60 |

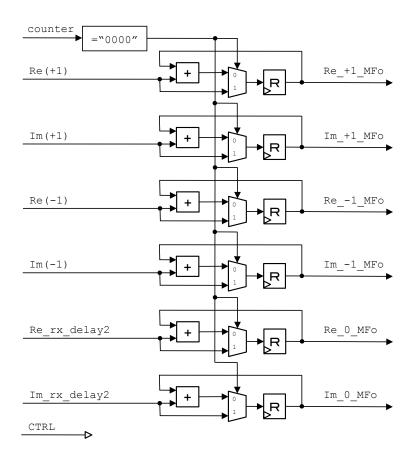

| 7.18 | Hardware representation of the MFs accumulator                          | 61 |

| 7.19 | Hardware representation of the MFs output control system                | 61 |

| 7.20 | Hardware representation of the SOVA decoder                             | 63 |

| 7.21 | Hardware representation of the branch increment calculator              | 66 |

| 7.22 | Hardware representation of the metric manager                                | 68 |

|------|------------------------------------------------------------------------------|----|

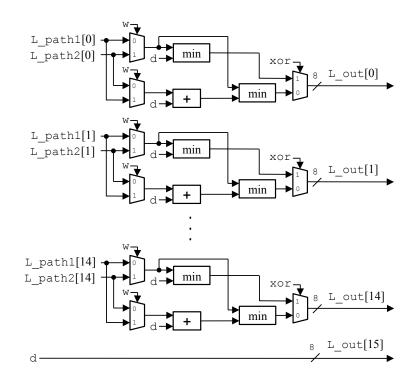

| 7.23 | Hardware representation of the metric calculator. $\ldots$ $\ldots$ $\ldots$ | 69 |

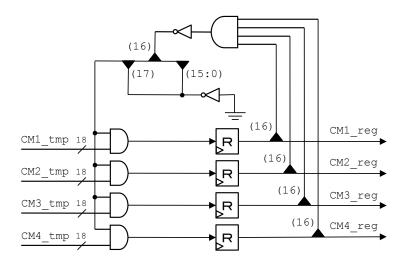

| 7.24 | Hardware representation of the metric registers update unit. $\ . \ .$       | 71 |

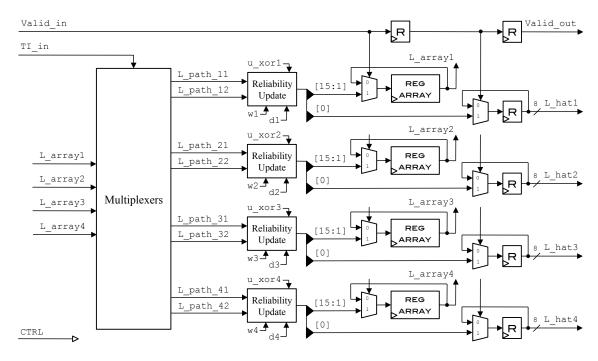

| 7.25 | Hardware representation of the hard-decision traceback unit                  | 72 |

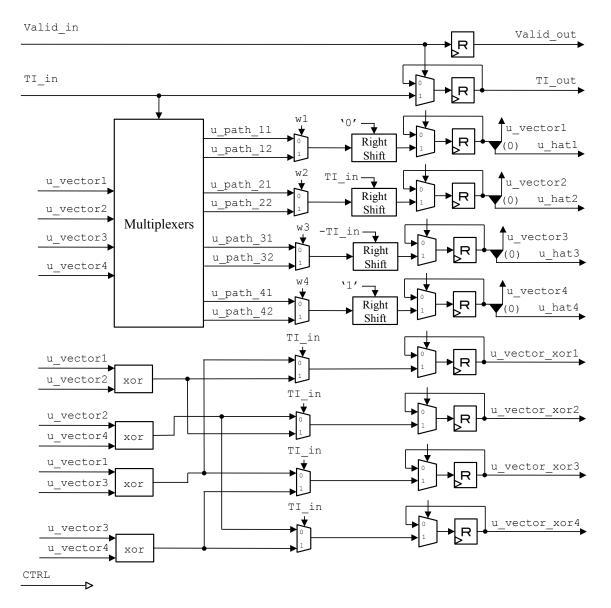

| 7.26 | Hardware representation of the reliability traceback unit                    | 75 |

| 7.27 | Hardware representation of the reliability update unit. $\ldots$ .           | 77 |

| 7.28 | Hardware representation of the output calculator                             | 78 |

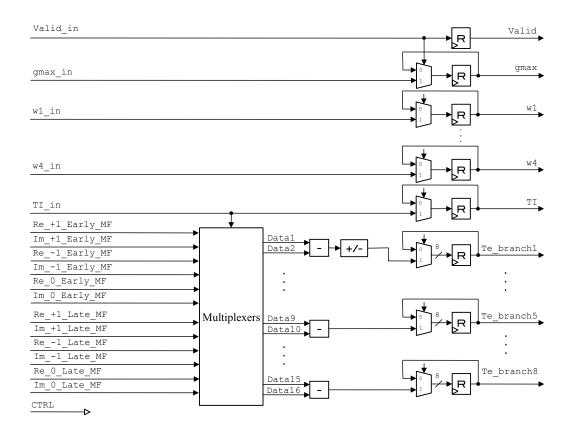

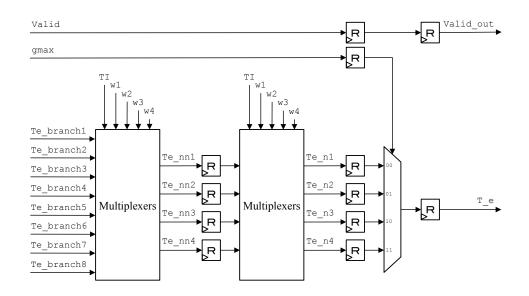

| 7.29 | Block diagram of the timing error detector                                   | 80 |

| 7.30 | Hardware representation of the TED input selector                            | 81 |

| 7.31 | Hardware representation of the TED error calculator                          | 83 |

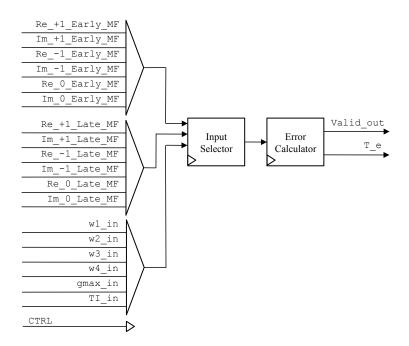

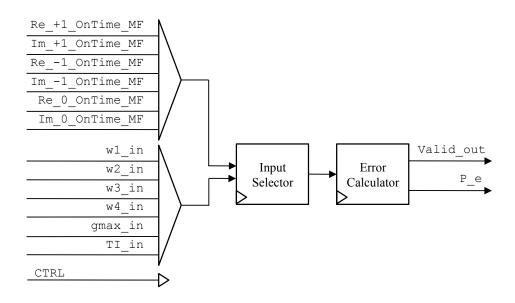

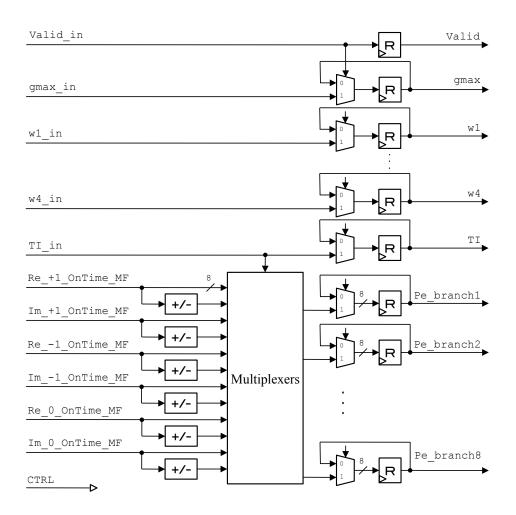

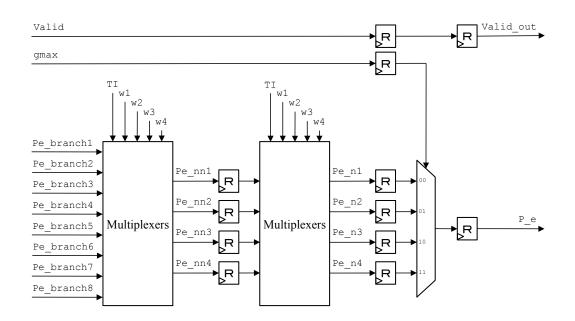

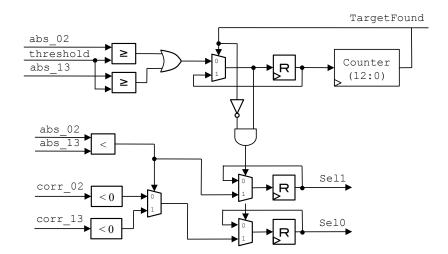

| 7.32 | Block diagram of the phase error detector                                    | 86 |

| 7.33 | Hardware representation of the PED input selector                            | 87 |

| 7.34 | Hardware representation of the PED error calculator                          | 88 |

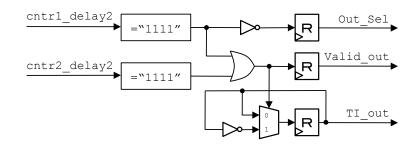

| 7.35 | Hardware representation of the soft-decision correlator                      | 92 |

| 7.36 | Hardware representation of the phase ambiguity selector                      | 93 |

| 8.1  | BER performance of VHDL model in ModelSim                                    | 96 |

| 8.2  | Block diagram representation of the hardware test setting                    | 97 |

| 8.3  | BER performance of VHDL model in hardware                                    | 98 |

# List of Tables

| 4.1  | Branch data lookup table for the standard precoder                           | 20  |

|------|------------------------------------------------------------------------------|-----|

| 4.2  | Branch data lookup table for the recursive precoder                          | 20  |

| 7.1  | I/Q downconversion mixers                                                    | 41  |

| 7.2  | Mapping of branch increments according to TI                                 | 67  |

| 7.3  | Mapping of branch metric candidates according to TI                          | 70  |

| 7.4  | Mapping of merging path-decision vectors according to TI                     | 73  |

| 7.5  | Mapping of merging reliability arrays according to TI                        | 76  |

| 7.6  | Mapping of subtraction operands according to TI                              | 82  |

| 7.7  | Mapping of first traceback operation according to TI and w1-w4.              | 84  |

| 7.8  | Mapping of second traceback operation according to $\tt TI$ and $\tt wl-w4.$ | 84  |

| 7.9  | Mapping of phase-error estimates according to TI                             | 88  |

| 7.10 | Mapping of first traceback operation according to TI and w1-w4.              | 90  |

| 7.11 | Mapping of second traceback operation according to $\tt TI$ and $\tt w1-w4.$ | 90  |

| 8.1  | Average BER performance loss.                                                | 99  |

| 8.2  | Hardware performance results of the VHDL model                               | 100 |

### Chapter 1

# Introduction

### 1.1 Background

In aeronautical telemetry, vital information about an aeronautical vehicle is remotely measured and sent to a distant location for analysis. The operations that aeronautical telemetry perform are numerous and complex, and some of them include new aircraft testing, systems monitoring, missile tracking and positioning, and area surveillance. The success of an aeronautical telemetry mission is highly dependent on the robustness of the communication link between the aeronautical vehicle and the ground station. Due to the inherent cost of each flight test, the receiver must be able to recover the transmitted information from the noisy received signal, and avoid costly retransmissions.

In an effort to upgrade its current communication methods, the aeronautical telemetry community has taken part in a migration to *forward error correction* (FEC) codes in the recent years. By introducing meaningful redundancy into the stream of data, FEC codes allow the receiver to detect and correct errors, up to some limit, without the need and, more importantly, the cost of data retransmis-

sions. The adoption of FEC codes in aeronautical telemetry is a clear advantage. However, migration to this technology also represents a challenge because existing receivers must be enhanced to be FEC-compatible.

The High-Rate High-Speed Forward Error Correction Architectures for Aeronautical Telemetry (HFEC) project, carried out at The Information and Telecommunication Technology Center (ITTC) at The University of Kansas, is currently investigating modern FEC codes with high-performance iterative decoders. The goal of this research is to develop hardware FEC decoders that are efficient in their use of hardware resources and implementation effort. The project focusses on two FEC codes as design examples. These are low density parity check (LDPC) codes and serially concatenated convolutional codes (SCCC). Both LDPC and SCCC decoders require a demodulator that can provide soft-output, as well as recover the symbol timing and carrier phase from the noisy received signal. The internal components and efficient hardware implementation of this demodulator is the focus of this thesis.

#### 1.2 Objectives

In this thesis, we present a hardware implementation of a fully-synchronized demodulator for *shaped offset quadrature phase shift keying, telemetry group* version (SOQPSK-TG) for use in FEC applications. This demodulator is attractive for its reduced complexity and strong performance, and is efficiently implemented by the *soft output Viterbi algorithm* (SOVA). The main contributions of this work are in the implementation details of data sequence detection, symbol timing synchronization, carrier phase synchronization, and block recovery. This implementation has been written in the widely-used hardware description language known

as VHDL, and is intended for use in a *field-programmable gate array* (FPGA).

### 1.3 Organization

This thesis is organized into 9 chapters. The information contained in these chapters is listed below (chapters containing the novel contributions of this thesis are marked with a \*):

- Chapter 2 gives a description of the signal model for SOQPSK and the most common precoders that are used for this modulation.

- Chapter 3 introduces the two iterative decoders considered as design examples in the HFEC project: SCCC and LDPC.

- Chapter 4 describes a reduced-complexity approach for the detection of SO-QPSK via the soft-output Viterbi algorithm.

- Chapter 5 explains how symbol timing synchronization is achieved.

- Chapter 6 explains how carrier phase synchronization is achieved.

- \*Chapter 7 gives a highly-detailed look at a hardware design of the fullysynchronized SOQPSK-TG demodulator. This chapter contains the majority of the work of this thesis, and therefore is longer.

- \*Chapter 8 reveals the results of the hardware implementation of the SOQPSK-TG demodulator in VHDL.

- \*Chapter 9 gives conclusions and suggestions for future improvements.

# Chapter 2

# **Description of SOQPSK**

This chapter describes the signal model for SOQPSK and the most common precoders that are used for this modulation.

### 2.1 CPM Signal Model

The SOQPSK signal is defined as a CPM [1] with the complex baseband representation

$$s(t; \boldsymbol{\alpha}) \triangleq \sqrt{\frac{E}{T}} e^{j\phi(t; \boldsymbol{\alpha})}$$

(2.1)

where E is the symbol energy, and T is the symbol time. The phase is a pulse train of the form

$$\phi(t; \boldsymbol{\alpha}) \triangleq 2\pi h \sum_{i=-\infty}^{k} \alpha_i q(t - iT), \quad kT \le t < (k+1)T$$

(2.2)

where h = 1/2 is the modulation index, and  $\alpha_i \in \{-1, 0, 1\}$  is a transmitted symbol. We use this notation to be consistent with previous work with SOQPSK; nonetheless, it is in conflict with traditional CPM notation. In strict CPM terms, we really have h = 1/4 and  $\alpha_i \in \{-2, 0, 2\}$  when the data alphabet is ternary (M = 3). The phase pulse q(t) is defined as

$$q(t) \triangleq \begin{cases} 0, & t < 0\\ \int_0^t f(\sigma) \, d\sigma, & 0 \le t < LT\\ 1/2, & t \ge LT \end{cases}$$

(2.3)

where f(t) is the frequency pulse, which has a duration of L symbol times and an area of 1/2. When the frequency pulse lasts one symbol time (L = 1), it is said to be *full-response*; however, when it lasts more than one symbol time (L > 1), it is said to be *partial-response*. Due to the constraints on f(t) and q(t), the phase in (2.2) may be expressed as

$$\phi(t; \boldsymbol{\alpha}) = \underbrace{2\pi h \sum_{i=k-L+1}^{k} \alpha_i q(t-iT)}_{\theta(t; \boldsymbol{c}_k; \alpha_k)} + \underbrace{\pi h \sum_{i=0}^{k-L} \alpha_i}_{\theta_k}$$

(2.4)

with support on the interval  $kT \leq t < (k + 1)T$ . The first term  $\theta(t; \mathbf{c}_k; \alpha_k)$ is the correlative phase and is a function of the correlative state vector  $\mathbf{c}_k \triangleq [\alpha_{k-L+1}, ..., \alpha_{k-2}, \alpha_{k-1}]$  and the current symbol  $\alpha_k$ . The correlative phase contains the *L* most recent symbols being modulated by the phase pulse. The second term  $\theta_k$  is the phase state and is a function of the remaining symbols. Due to the fact that *h* is a rational number, the phase state can only assume p = 4 distinct values when taken modulo- $2\pi$ , which are  $\theta_k \in \{0, \pi/2, \pi, 3\pi/2\}$ . When this result is applied in (2.1), it gives  $e^{j\theta_k} \in \{\pm 1, \pm j\}$ .

There are multiple versions of SOQPSK, which differ by their respective frequency pulses. In this work, we focus on the version recently adopted in aeronau-

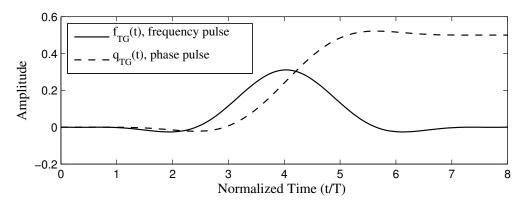

Figure 2.1. Length-8*T* frequency pulse and corresponding phase pulse for SOQPSK-TG.

tical telemetry, known as "SOQPSK-TG" [2]. It uses a partial-response frequency pulse with L = 8, which is given by

$$f_{\rm TG}(t) \triangleq A \frac{\cos\left(\frac{\pi\rho Bt}{2T}\right)}{1 - 4\left(\frac{\rho Bt}{2T}\right)^2} \times \frac{\sin\left(\frac{\pi Bt}{2T}\right)}{\frac{\pi Bt}{2T}} \times w(t)$$

(2.5)

where the window is

$$w(t) \triangleq \begin{cases} 1, & 0 \le \left|\frac{t}{2T}\right| < T_1 \\ \frac{1}{2} + \frac{1}{2}\cos\left(\frac{\pi}{T_2}\left(\frac{t}{2T} - T_1\right)\right), & T_1 \le \left|\frac{t}{2T}\right| \le T_1 + T_2 \\ 0, & T_1 + T_2 < \left|\frac{t}{2T}\right| \end{cases}$$

(2.6)

The constant A is chosen to give the pulse an area of 1/2 and  $T_1 = 1.5$ ,  $T_2 = 0.5$ ,  $\rho = 0.7$ , and B = 1.25. The partial-response frequency pulse shown in Fig. 2.1 results in a more compact spectrum (compared to other frequency pulses) and was selected to meet the bandwidth constraints of the aeronautical telemetry community [2].

### 2.2 Frequency Pulse Truncation for SOQPSK-TG

The structure of the CPM phase in (2.4) is conveniently described by a phase trellis comprised of  $pM^{L-1}$  states. For SOQPSK-TG, this amounts to  $pM^{L-1} =$ 512 states. An optimal detector for this version of SOQPSK would consequently require a 512-state trellis, which is impractical and highly complex. Due to this reason, we pursue a near-optimum approximation for SOQPSK-TG, known as *pulse truncation* (PT) [3,4]. This approximation results in a simple detector that is based on a four-state trellis with a loss in performance of only 0.2 dB [5].

The PT approximation for SOQPSK-TG is based on the fact that the frequency pulse  $f_{TG}(t)$  shown in Fig. 2.1 is near-zero for a significant portion of its duration. Using this argument, the frequency pulse can be truncated to only include its smooth time-varying section. In other words, the truncation is centered such that half is applied to the beginning of the pulse and half to the end. After translating these conditions to the phase pulse we obtain the modified phase pulse

$$q_{\rm PT}(t) = \begin{cases} 0, & t < 0\\ q(t + (L-1)T/2), & 0 \le t \le T\\ 1/2, & t > T \end{cases}$$

(2.7)

It is important to notice that since  $q_{PT}(t)$  has variations only in the time interval [0, T], it behaves like a full-response pulse (L = 1). This implies that the correlative state vector  $\mathbf{c}_k$  in (2.4) is empty; and thus, it will be omitted from the notation used in future chapters. We base the detector presented in this work on this truncated phase pulse.

### 2.3 SOQPSK Precoders

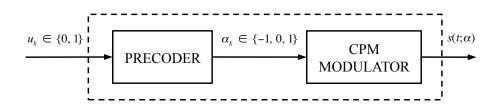

SOQPSK is different from ordinary CPM in that it uses a precoding operation to convert the binary sequence  $\{u_k\}$  into a ternary sequence  $\{\alpha_k\}$ . The signal model for uncoded SOQPSK is shown in Fig. 2.2. In this section, we describe two of the most commonly used precoders for SOQPSK.

Figure 2.2. Signal model for uncoded SOQPSK.

#### 2.3.1 Standard Precoder

The standard precoder converts the binary input bits  $\{u_k\}$  into ternary data  $\{\alpha_k\}$  according to the mapping [6]

$$\alpha_k(\boldsymbol{u}) \triangleq (-1)^{k+1} (2u_{k-1} - 1)(u_k - u_{k-2})$$

(2.8)

where  $u_k \in \{0, 1\}$  and  $\alpha_k \in \{-1, 0, +1\}$ . The role of the precoder is to orient the phase of the CPM signal in (2.4), such that it behaves like the phase of an OQPSK signal that is driven by the bit sequence  $\boldsymbol{u}$ . For convenience, in what follows we refer to  $\alpha_k(\boldsymbol{u})$  as  $\alpha_k$ , but we stress that  $\boldsymbol{u}$  is the underlying bit sequence. The precoder imposes three important constraints on the ternary data [6]:

- 1. In any given bit interval,  $\alpha_k$  is drawn from one of two binary alphabets, {0,+1} or {0,-1}.

- 2. When  $\alpha_k = 0$ , the binary alphabet for  $\alpha_{k+1}$  switches from the one used for  $\alpha_k$ , but when  $\alpha_k \neq 0$  the binary alphabet for  $\alpha_{k+1}$  does not change.

- 3. A value of  $\alpha_k = +1$  cannot be followed by  $\alpha_{k+1} = -1$ , and vice versa.

These constraints imply that not every possible ternary symbol pattern is a valid SOQPSK data pattern. For example, the ternary data sequences  $\ldots$ , 0, -1, +1, 0,  $\ldots$  and  $\ldots$ , -1, 0, -1,  $\ldots$  violate the SOQPSK constraints.

#### 2.3.2 Recursive Precoder

Another frequently used precoder that satisfies these constraints can be obtained by differentially encoding the input bits  $u_k$  at the transmitter. The differential (recursive) nature of this precoder is essential when SOQPSK is used as the inner code in a serially concatenated system [7]. The differentially encoded bits are

$$d_k = u_k \oplus d_{k-2} \tag{2.9}$$

where  $\oplus$  is the XOR operator for binary data in the set  $\{0, 1\}$ . The precoder in this case is

$$\alpha_k(\boldsymbol{u}) = (-1)^k \, u_k \, d'_{k-1} \, d'_{k-2} \tag{2.10}$$

where  $d' \in \{-1, +1\}$  is the antipodal counterpart of  $d_k$  and is given by  $d'_k = 2d_k - 1$ .

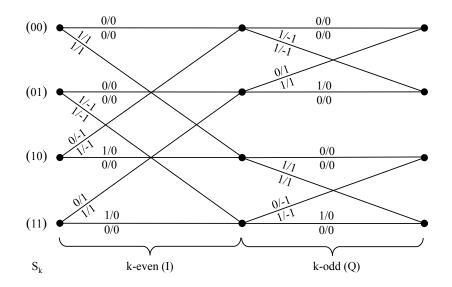

Figure 2.3. Four-state time-varying trellis. The labels above each branch are for the standard precoder in (2.8), while the labels below each branch are for the recursive precoder in (2.10). The branch labels indicate the input-bit/output-symbol pair  $u_k/\alpha_k$ .

#### 2.4 Trellis Representation

The precoder/CPM modulator pair shown in Fig. 2.2 can be thought of as having a *state* at any time throughout the encoding process. Using  $u_{k-1}$ ,  $u_{k-2}$ , and k-even/k-odd from the standard precoder (2.8) as state variables, it has been shown that eight states are required to describe the precoder/CPM system [8]. We may reduce the number of states from eight to four if we construct a *timevarying* trellis, with different sections for k-even and k-odd. This four-state timevarying trellis is shown in Fig. 2.3. The labels above each branch show the inputbit/output-symbol pair  $u_k/\alpha_k$  for the given branch using the standard precoder. The state variable pairs  $S_k \in \{00, 01, 10, 11\}$  shown on the left side of the trellis are ordered  $(u_{k-2}, u_{k-1})$  for k-even and  $(u_{k-1}, u_{k-2})$  for k-odd. When k is even, the input bit  $u_k$  replaces the leftmost bit in the pair, and when k is odd, it replaces the rightmost bit. It is important to note that for any given time interval k, each branch is identified with a unique value of the branch vector  $[u_k, S_k]$  [5].

Similarly, the recursive precoder (2.10) is also described by the four-state time-varying trellis in Fig. 2.3. The labels below each branch show the inputbit/output-symbol pair  $u_k/\alpha_k$  for the recursive precoder. In this case, the state variables are  $d_{k-1}$  and  $d_{k-2}$ , instead of  $u_{k-1}$  and  $u_{k-2}$ . The state variable pairs  $S_k$  are ordered and updated in the same way as before. Although each precoder imposes a different input-bit/output-symbol mapping, the output-symbols are identical in either case.

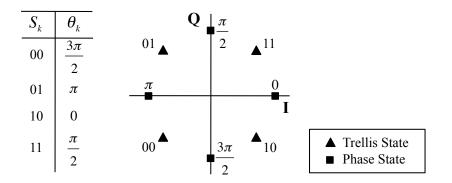

**Figure 2.4.** Mapping between the trellis state variable pairs  $S_k$  and the CPM phase states  $\theta_k$ .

A key relationship between the SOQPSK precoders and the CPM modulator is that the state variable pairs  $S_k$  and the CPM phase state  $\theta_k$  are interchangeable as state variables [9]. This one-to-one mapping is shown in Fig. 2.4 and is essential to the reduced-complexity characteristic of the detector proposed herein.

### Chapter 3

# **Coded SOQPSK Iterative Decoders**

SOQPSK serves as the inner code in the two concatenated coded modulation schemes investigated by the HFEC project. In order to present a framework for the demodulator described in this work, this chapter describes the two iterative decoders considered as design examples.

#### 3.1 Serially Concatenated Convolutional Code Decoder

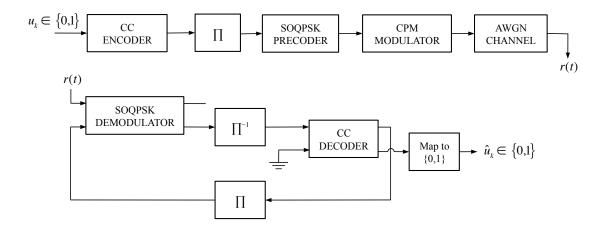

The SCCC modulation scheme under consideration is shown in Fig. 3.1. The encoder/transmitter portion of the system consists of a convolutional code (CC) encoder, an S-random interleaver (labeled as " $\Pi$ " in the block diagram), the recursive SOQPSK precoder from (2.10), and a CPM modulator. Therefore, the CC serves as the outer code, and SOQPSK serves as the inner code in a serially concatenated coding scheme. The recursive formulation of the precoder is necessary to yield large coding gains from the concatenation of the outer CC and the interleaver [5].

**Figure 3.1.** Block diagram of a serially concatenated convolutional code decoder.

In the receiver portion of the system, an iterative decoding approach is used. Instead of making one pass over the concatenated decoder, the iterative method performs several. Soft decisions about the inner code are produced from the SOQPSK demodulator, de-interleaved and fed into the CC decoder. Then, soft decisions about the outer code are produced from the CC decoder, re-interleaved and used as prior information in the SOQPSK demodulator. Since there is never any prior information about the outer code, that input in the CC decoder is assumed to be zero (shown with a "ground" symbol). The decoding operation repeats itself for a set number of iterations, after which, a final binary output is generated.

While Fig. 3.1 only shows one version of the SOQPSK demodulator, in reality this iterative decoding scheme requires two versions. For the first iteration, a fullversion of the demodulator is required to recover the symbol timing and carrier phase of the received signal, and at the same time, to estimate the transmitted bit sequence. Ordered matched filter outputs from within the demodulator are stored to be used as information inputs to the demodulator for the second and

Figure 3.2. Block diagram of a concatenated low density parity check decoder.

following iterations through the decoder. We refer to this ordered matched filter outputs as branch increments in the following chapters. The branch increments are already time-synchronized and phase-corrected; therefore, in order to process these inputs only a simple-version of the demodulator is required.

This iterative decoding method provides a significant increase in performance over a single iteration. In addition, the use of a soft-decision implementation for the SOQPSK demodulator and the CC decoder provides a 1-2 dB gain in BER performance over a hard-decision implementation [10]. Both, the demodulator and the decoder are efficiently implemented by the soft-output Viterbi algorithm. The use of interleavers ( $\Pi$ ) helps the system manage bursts of errors, which the Viterbi algorithm is very sensitive to.

#### 3.2 Low Density Parity Check Decoder

The concatenated LDPC modulation scheme under consideration is shown in Fig. 3.2. The encoder/transmitter portion of the system consists of an LDPC encoder, the standard SOQPSK precoder from (2.8), and a CPM modulator. In this case, LDPC serves as the outer code, and SOQPSK serves as the inner code.

In the receiver portion of the system, soft decisions about the inner code are produced by the SOQPSK demodulator and provided as inputs to the LDCP decoder. Unlike the SCCC model, the concatenated LDPC scheme only performs one pass over the decoder; therefore, it only requires the full version of the demodulator. The iterative nature of this concatenated decoder comes from the fact that the LDPC decoder performs a fixed number of attempts on the input stream to try to decode the transmitted information. The LDPC algorithm has the advantage of knowing with certainty if the decoding operation was successful, unlike other decoding methods. Therefore, after a set number of iterations, the LDPC decoder outputs a binary sequence if successful, or a decoding failure message, otherwise.

### Chapter 4

# Sequence Detection for SOQPSK

Consider a signaling waveform sent through additive white Gaussian noise, the AWGN channel. The received signal model is

$$r(t) = \sqrt{\frac{E}{T}} e^{j\phi(t-\tau;\boldsymbol{\alpha})} e^{j\phi_0} + w(t)$$

(4.1)

where w(t) is a zero-mean complex-valued AWGN process with one-sided power spectral density  $N_0$ . This representation shows that the data symbols  $\boldsymbol{\alpha}$ , the symbol timing  $\tau$ , and the carrier phase  $\phi_0$ , are unknown to the receiver and must be handled appropriately. A method to recover  $\tau$  and  $\phi_0$ , based on maximum likelihood (ML) principles, is developed in Chapters 5 and 6. In this chapter, we describe a maximum likelihood sequence detection (MLSD) approach used to decode the data symbols  $\boldsymbol{\alpha}$ . This approach is efficiently implemented via the softoutput Viterbi algorithm (SOVA). In what follows, we refer to the estimated and hypothesized values of a generic quantity a as  $\hat{a}$  and  $\tilde{a}$  respectively. Also,  $\hat{a}$  and  $\tilde{a}$ can assume the same value of a itself.

#### 4.1 Maximum Likelihood Sequence Detection

CPM signals are optimally demodulated by applying MLSD [1, Ch. 7]. Since SOQPSK is a form of CPM, MLSD can be applied to recover the symbol sequence  $\alpha$  (and consequently, the underlying bit sequence u).

In order to develop this approach, the detector first assumes that the symbol timing  $\tau$  and the carrier phase  $\phi_0$  are known [11]. Using the CPM model for SOQPSK in (2.4), it was shown in [5] that the likelihood function for (4.1), given a hypothetical bit sequence  $\tilde{\boldsymbol{u}}$  over the interval  $0 \leq t \leq T$  is

$$\Lambda(\boldsymbol{r}|\tilde{\boldsymbol{u}}) = \exp\left\{\frac{1}{N_0}\sqrt{\frac{E}{T}}\operatorname{Re}\left\{e^{-j\phi_0}\boldsymbol{Z}_k(\tilde{\alpha}_k,\tau)e^{-j\tilde{\theta}_k}\right\}\right\}$$

(4.2)

where  $\mathbf{Z}_k(\cdot)$  are the matched filter (MF) outputs. The variables  $\tilde{\alpha}_k$  and  $\hat{\theta}_k$  correspond to hypothetical values obtained from  $\tilde{\boldsymbol{u}}$ . The MF outputs  $\mathbf{Z}_k(\tilde{\alpha}_k, \tau)$  are sampled at the instant  $\tau + (k+1)T$  to produce

$$\boldsymbol{Z}_{k}(\tilde{\alpha}_{k},\tau) \triangleq \int_{\tau+kT}^{\tau+(k+1)T} r(t)e^{-j2\pi\hbar\tilde{\alpha}_{k}q_{\mathrm{PT}}(t-\tau-kT)} dt$$

(4.3)

In order to implement (4.2), the output of three complex-valued MFs is needed. Since the SOVA must consider all possible path histories, a MF output for each possible value of the ternary  $\tilde{\alpha}_k$  must be computed. The complex-valued MF outputs for  $\tilde{\alpha}_k = \pm 1$  can be constructed from the same four real-valued components due to the identities  $\sin(-x) = -\sin(x)$  and  $\cos(-x) = \cos(x)$ . The MF output for  $\tilde{\alpha}_k = 0$  has a value of unity for length-T, which is simply an integrate-anddump operation that requires no multiplications. Therefore, only four real-valued filtering operations are required in total to implement (4.2).

Figure 4.1. Discrete-time approach to MLSD for SOQPSK.

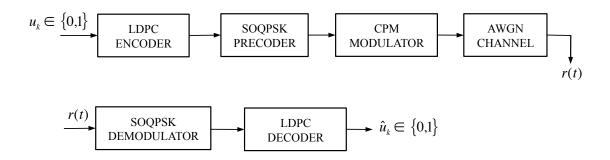

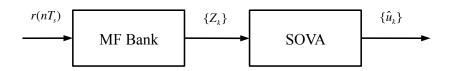

A discrete-time implementation of the sequence detection process is shown in block diagram form in Fig. 4.1. An ADC samples the received signal r(t) at a rate  $F_s = \frac{1}{T_s}$  to produce  $r(nT_s)$ . Then, the samples are fed to the MF bank, whose output forms the values in the set  $\{\mathbf{Z}_k\}$ . The MF outputs are then used to update the branch metrics within the SOVA. The SOVA finds the data symbols sequence  $\tilde{\boldsymbol{u}}$  that maximizes (4.2) and outputs the estimated bit sequence  $\hat{\boldsymbol{u}}$ .

In standard notation, the inputs to the SOVA are real-valued probabilities associated with the hypothetical bit sequence  $\tilde{u}$ , instead of MF outputs. These probabilities are referred to as *branch increments* and are given by

$$\boldsymbol{B}_{k}(\tau,\phi_{0},[\tilde{u}_{k},\tilde{S}_{k}]) \triangleq \operatorname{Re}\left[e^{-j\phi_{0}}\boldsymbol{Z}_{k}(\tilde{\alpha}_{k},\tau)e^{-j\tilde{\theta}_{k}}\right]$$

(4.4)

where  $\tilde{u}_k$  and  $\tilde{S}_k$  are hypothetical values of the branch bit and the state variable, respectively. Each branch increment is identified with a unique value of the branch vector  $[\tilde{u}_k, \tilde{S}_k]$ . This allows every branch increment to have a one-to-one correspondence with a hypothetical ternary symbol  $\tilde{\alpha}_k$  and a hypothetical CPM phase state  $\tilde{\theta}_k$ , as shown in Figs. 2.3 and 2.4. As a side remark, it is important to note that multiplying by the factor  $e^{-j\tilde{\theta}_k} \in \{\pm 1, \pm j\}$  in (4.4) does not require any multiplication resources in the hardware implementation.

| P(c; I)          |      | P(c; O)          |

|------------------|------|------------------|

| P( <b>u</b> ; I) | SOVA | P( <b>u</b> ; O) |

Figure 4.2. Block diagram of the soft output Viterbi algorithm.

#### 4.2 SOVA Implementation

The SOVA module under consideration is shown in Fig. 4.2. The module accepts the sequences of a priori probability distributions  $P(\boldsymbol{c}; I)$  and  $P(\boldsymbol{u}; I)$  at the input, and outputs the sequences of probability distributions  $P(\boldsymbol{c}; O)$  and  $P(\boldsymbol{u}; O)$ . Here,  $\boldsymbol{c}$  corresponds to the sequence of coded information, and  $\boldsymbol{u}$  corresponds to the sequence of uncoded, underlying information. In this work, we are interested in the two inputs and the  $\boldsymbol{u}$  output. The description of the SOVA outlined in this section is based on [12].

To organize the information contained in the trellis shown in Fig. 2.3, and to aid in explaining the operations in the SOVA, we define the following tables. Table 4.1 contains the information for the standard precoder (2.8), while table 4.2 contains the information for the recursive precoder (2.10). The branch index  $e \in \{0, 1, 2, 3, ..., 7\}$  is a unique value that identifies each branch in the trellis. This index is ordered from top to bottom, with the branch associated with  $u_k = 0$ labeled first than the branch associated with  $u_k = 1$  at every trellis state. Also, each branch has an associated starting state SS(e) and an ending state ES(e), which depends on whether k is even or odd. In addition, the branch data BD(e)and branch symbol BS(e) which correspond to the input-bit/output-symbol pair  $u_k/\alpha_k$  are also indicated.

| e | SS(e) | ES(e) |     | BD(e) |     | BS(e)    |     |

|---|-------|-------|-----|-------|-----|----------|-----|

|   | $S_k$ |       |     | $u_k$ |     | $lpha_k$ |     |

|   |       | even  | odd | even  | odd | even     | odd |

| 0 | 00    | 00    | 00  | 0     | 0   | 0        | 0   |

| 1 | 00    | 10    | 01  | 1     | 1   | 1        | -1  |

| 2 | 01    | 01    | 00  | 0     | 0   | 0        | 1   |

| 3 | 01    | 11    | 01  | 1     | 1   | -1       | 0   |

| 4 | 10    | 00    | 10  | 0     | 0   | -1       | 0   |

| 5 | 10    | 10    | 11  | 1     | 1   | 0        | 1   |

| 6 | 11    | 01    | 10  | 0     | 0   | 1        | 1   |

| 7 | 11    | 11    | 11  | 1     | 1   | 0        | 0   |

Table 4.1.

Branch data lookup table for the standard precoder.

Table 4.2. Branch data lookup table for the recursive precoder.

| e | SS(e) | ES(e) |     | BD(e) |     | BS(e)      |     |

|---|-------|-------|-----|-------|-----|------------|-----|

|   | $S_k$ |       |     | $u_k$ |     | $\alpha_k$ |     |

|   |       | even  | odd | even  | odd | even       | odd |

| 0 | 00    | 00    | 00  | 0     | 0   | 0          | 0   |

| 1 | 00    | 10    | 01  | 1     | 1   | 1          | -1  |

| 2 | 01    | 01    | 01  | 0     | 0   | 0          | 0   |

| 3 | 01    | 11    | 00  | 1     | 1   | -1         | 1   |

| 4 | 10    | 10    | 10  | 0     | 0   | 0          | 0   |

| 5 | 10    | 00    | 11  | 1     | 1   | -1         | 1   |

| 6 | 11    | 11    | 11  | 0     | 0   | 0          | 0   |

| 7 | 11    | 01    | 10  | 1     | 1   | 1          | -1  |

Assume that the SOVA uses K as a time index increasing from 0 to N - 1, where N is the length of the received sequence. At each decoding step,  $P(\mathbf{c}; I)$ receives eight real-valued inputs (one for each branch in the trellis) corresponding to the branch increments  $\mathbf{B}_k(\tau, \phi_0, [\tilde{u}_k, \tilde{S}_k])$  in (4.4). For simplicity, in this section we refer to each branch increment as  $B_k(e)$ , where  $e \in \{0, 1, 2, 3, ..., 7\}$  is a branch index.

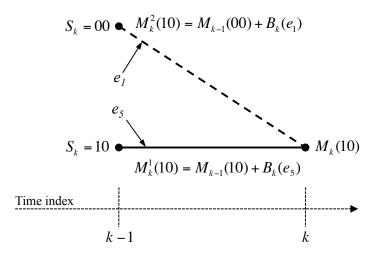

Figure 4.3. Illustration of the metric update process.

With each transition in the binary trellis, two branches enter each trellis state. These are referred to as competing branches, and the SOVA must determine which one is the winning branch. For this purpose, we define the branch metric candidate

$$M_k^{(i)}(ES(e)) = M_{k-1}(SS(e)) + B_k(e)$$

(4.5)

where  $i \in \{1, 2\}$  is an index to indicate the two competing branches. The value i = 1 is typically assigned to the winning candidate, while i = 2 is assigned to the losing candidate. The SOVA evaluates the two branch metric candidates terminating at each trellis state  $S_k$ , and updates the cumulative metrics according to the following comparison

$$M_k(S_k) = \max \{ M_k^{(1)}(S_k), \ M_k^{(2)}(S_k) \}$$

(4.6)

Fig. 4.3 shows an illustration of the metric update process. In this example, branch  $e_1$  is considered to be the losing branch, and is marked with a dashed line

to indicate that it will be ignored by the decoder in subsequent operations.

In addition to updating the cumulative metrics, the SOVA must determine the bit  $\hat{u}_k$  associated with the winning branch at each trellis state  $S_k$ . This is possible by using the one-to-one mapping between branches and the branch vector  $[u_k, S_k]$ . The decoded bits  $\hat{u}_k$  are stored in path decision vectors  $\hat{u}(S_k)$ , which contain the  $(\delta + 1)$  most recent decisions  $\{\hat{u}_{k-\delta}, ..., \hat{u}_k\}$  at each trellis state  $S_k$ . The parameter  $\delta$  represents the size of the decoding window. It has been shown in, i.e [13], that there is a high probability that the paths at the current stage of the trellis converge to a single surviving path after  $\delta$  time steps in the decoding process. The use of a decoding window allows the decoder to start generating an output after some number of stages, without the need to traverse the entire received signal.

Next, the SOVA must compute the set of reliabilities  $\hat{\boldsymbol{L}}(S_k) = {\hat{L}_{k-\delta}, ..., \hat{L}_k}$ associated with the decoded bits in the path decision vectors  $\hat{\boldsymbol{u}}(S_k)$  merging at state  $S_k$ . To this end, we define

$$\Delta_k(S_k) = |M_k^{(1)}(S_k) - M_k^{(2)}(S_k)|$$

(4.7)

and set  $\hat{L}_k = \Delta_k(S_k)$  since  $\Delta_k(S_k)$  represents the reliability difference between the two most likely code-sequences terminating in state  $S_k = ES(e)$  at time step k. Next, the remaining values  $\hat{L}_j$ ,  $j = k - \delta$ , ..., k - 1 of the surviving  $\hat{L}(S_k)$  at state  $S_k$  have to be updated. The reliabilities update process uses the same notion of competing paths converging at the same trellis state. We refer to these two paths as path-1 and path-2, and without loss of generality assume that path-1 is the surviving path. Therefore, we have the set of reliabilities  $\hat{L}^{(1)}(S_k) = \{\hat{L}_{k-\delta}^{(1)}, ..., \hat{L}_{k-1}^{(1)}\}$ for path-1, and  $\hat{L}^{(2)}(S_k) = \{\hat{L}_{k-\delta}^{(2)}, ..., \hat{L}_{k-1}^{(2)}\}$  for path-2. Similarly, we have the two path decision vectors  $\hat{u}^{(1)}(S_k) = \{\hat{u}_{k-\delta}^{(1)}, ..., \hat{u}_{k-1}^{(1)}\}$  and  $\hat{u}^{(2)}(S_k) = \{\hat{u}_{k-\delta}^{(2)}, ..., \hat{u}_{k-1}^{(2)}\}$  corresponding to path-1 and path-2, respectively. First, we consider the case when  $\hat{u}_j^{(1)} \neq \hat{u}_j^{(2)}$ , for some  $j \in \{k - \delta, ..., k - 1\}$ , and we update as

$$\hat{L}_j(S_k) = \min \{\Delta_k(S_k), \hat{L}_j^{(1)}\}$$

(4.8)

Next, we consider the case when  $\hat{u}_j^{(1)} = \hat{u}_j^{(2)}$ , for some  $j \in \{k - \delta, ..., k - 1\}$ , and we update as

$$\hat{L}_j(S_k) = \min \left\{ \Delta_k(S_k) + \hat{L}_j^{(2)}, \, \hat{L}_j^{(1)} \right\}$$

(4.9)

The decoding window of the SOVA applies to the reliabilities in the same way it does to the bits. However, before the reliabilities are sent to the output, they are assigned the sign corresponding to its associated path decision value (positive for  $\hat{u}_k = 1$  and negative for  $\hat{u}_k = 0$ . Next, the input value  $P(\boldsymbol{u}; I)$  associated with decision  $\hat{u}_k$  must be subtracted from the newly-computed signed reliabilities. This is due to the fact that the input  $P(\boldsymbol{u}; I)$  is extrinsic information about the code, and hence, it must be removed for the next decoding iteration. The  $P(\boldsymbol{u}; I)$  input is only valid for the SCCC iterative decoder shown in Fig. 3.1, and is non-zero for all the decoding iterations after the first one.

### Chapter 5

# Symbol Timing Synchronization

Symbol timing synchronization ensures that sampling of the MF outputs is executed at the correct instant. The optimum sampling instant corresponds to the center of the eye diagram, as shown in Fig. 5.1. In general, a clock signal is not transmitted for the purpose of timing synchronization because bandwidth is a limited resource. Therefore, it must be recovered from the noisy received waveforms that carry the data [14, Ch. 8]. In this chapter, we develop a method based on ML principles to recover the symbol timing  $\tau$ .

Figure 5.1. Eye diagram showing the optimum sampling instant for the MF outputs.

Since this design is intended for use in digital hardware, the MF bank shown in Fig. 5.1 is implemented as a discrete-time filter. Therefore, an *analog-to-digital* converter (ADC) preceding the MFs is required. The ADC produces  $T_s$ -spaced

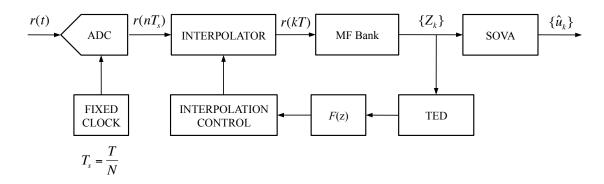

Figure 5.2. A discrete-time approach to symbol timing synchronization for SOQPSK.

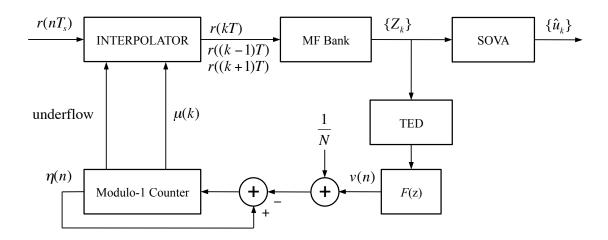

samples of the received signal (4.1) at a rate N = 16 samples/symbol. Due to the fact that the ADC runs on a fixed clock, the sample rate  $1/T_s$  is asynchronous with the symbol rate 1/T. This timing offset causes the MF bank to produce outputs  $\{Z_k\}$  that are not in the optimum sampling instant. The role of the timing synchronizer is to compute samples in the desired time instants using the available samples in  $r(nT_s)$ , so that the MF outputs are aligned with the center of the eye diagram. This operation is performed by a linear interpolator. A block diagram description of the timing synchronizer is shown in Fig. 5.2. The *timing error detector* (TED) produces a timing error signal based on the MF outputs. This error signal informs the loop filter F(z) about the timing difference, and is used to produce an adjusting signal. The interpolator control block runs a modulo-1 decrementing counter, which is updated using this adjusting signal. When the decrementing counter underflows, it indicates the beginning of a symbol boundary, and provides the fractional interval that the interpolator uses to compute the desired samples.

## 5.1 Timing Error Detector

The derivation of the TED presented here is based on [11]. In order to recover the symbol timing  $\tau$ , the ML detector temporarily assumes that the data symbols sequence  $\alpha$  and the carrier phase  $\phi_0$  are known. Using the same definitions from Chapter 4, it was shown in [15] that the likelihood function for (4.1), given a hypothetical timing value  $\tilde{\tau}$  over the interval  $0 \leq t \leq T$  is

$$\Lambda(\boldsymbol{r}|\tilde{\tau}) = \exp\left\{\frac{1}{N_0}\sqrt{\frac{E}{T}}\operatorname{Re}\left\{e^{-j\phi_0}\boldsymbol{Z}_k(\alpha_k,\tilde{\tau})e^{-j\theta_k}\right\}\right\}.$$

(5.1)

The ML estimate  $\tilde{\tau}$  is the value of  $\tau$  that maximizes the logarithm of (5.1), the log-likelihood function. In order to find  $\tilde{\tau}$ , we need to take the partial derivative of the log-likelihood function. Thus, we obtain

$$\frac{\partial}{\partial \tilde{\tau}} \log(\Lambda(\boldsymbol{r}|\tilde{\tau})) = \operatorname{Re}\left\{e^{-j\phi_0} \boldsymbol{Y}_k(\alpha_k, \tilde{\tau}) e^{-j\theta_k}\right\}$$

(5.2)

where  $\boldsymbol{Y}_k(\cdot)$  is the partial derivative of the MF outputs  $\boldsymbol{Z}_k(\cdot)$  with respect to  $\tilde{\tau}$ . The ML estimate  $\tilde{\tau}$  is the value of  $\tau$  that forces (5.2) to zero.

The value  $\tilde{\tau}$  is computed in an iterative and adaptive way. Initially, it was assumed that  $\boldsymbol{\alpha}$  and  $\phi_0$  are known, which is not the case. Therefore, two close approximations are used to substitute these values. The true data sequence  $\boldsymbol{\alpha}$  is replaced with the estimated decisions  $\hat{\boldsymbol{\alpha}}$  within the SOVA, and the true carrier phase  $\phi_0$  is replaced with the most recent phase estimate  $\hat{\phi}_0$  from the phase synchronizer described in Chapter 6. These approximations become more reliable the further we trace back along the trellis. Considering all these factors, the following timing error signal is obtained as in [15]

$$e_{\tau}[k-D] \triangleq \operatorname{Re}\left\{e^{-j\hat{\phi}_{0}[k-D]}\boldsymbol{Y}_{k-D}(\hat{\alpha}_{k-D},\hat{\tau}[k-D])e^{-j\hat{\theta}_{k-D}}\right\}$$

(5.3)

where D represents the delay in computing the error, and  $\hat{\alpha}_{k-D}$  and  $\hat{\theta}_{k-D}$  are taken from the path history of the best survivor in the SOVA. It is observed in [15] that D = 1 produces satisfactory results.

In order to compute the derivative  $\mathbf{Y}_k(\cdot)$ , a discrete-time differentiator would be required. However, it was shown in, e.g. [15], that this value can be approximated with the difference between a late and an early MF output sample. In the implementation of this TED, we use this proposed simplification to calculate  $\mathbf{Y}_k(\cdot)$ .

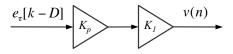

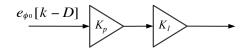

### 5.2 Loop Filter

The purpose of the loop filter is to provide an adjusting value to the interpolation control block based on the TED timing error signal. The transfer function for the loop filter in consideration is F(s) = k. This is a simple gain and produces a first-order PLL. A block diagram of the loop filter is shown in Fig. 5.3, where  $K_p = 1$  and  $K_1 = -0.0026$ .

**Figure 5.3.** A block diagram of the simple gain loop filter F(s).

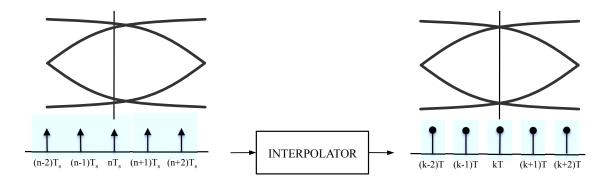

Figure 5.4. Illustration of the interpolation operation to achieve optimum sampling instants. Available samples before interpolation are represented with a triangle, while available samples after interpolation are represented with a circle.

### 5.3 Interpolation

The continuous-time received signal r(t) in (4.1) is sampled by the ADC at a rate  $1/T_s$ . This produces  $T_s$ -spaced samples, represented with a triangle in Fig. 5.4. Because the sample clock is independent of the data clock used by the transmitter, the sampling instants are not synchronized to the symbol periods. This is illustrated in Fig. 5.4 by showing samples not aligned with the maximum aperture of the eye-diagram. The interpolator uses these available samples to compute desired samples of r(t) at the optimum sampling instances. A desired sample at t = kT is called the k-th interpolant. When the k-th interpolant is between samples  $r(nT_s)$  and  $r((n + 1)T_s)$ , the sample index n is called the k-th basepoint index and is denoted m(k). The time instant kT is some fraction of a sample greater than  $m(k)T_s$ . This fraction is called the k-th fractional interval and is denoted by  $\mu(k)$  [14, Ch. 8]. The equation for interpolation may be expressed as

$$r(kT) = r(nT_s) + \mu(k)[r((n+1)T_s) - r(nT_s)]$$

(5.4)

for a desired sample at t = kT. This sample corresponds to the on-time interpolated sequence that will produce the aligned MF outputs  $\{Z_k\}$ . It was mentioned earlier that an early and a late MF outputs are also required to approximate the derivative  $Y_k(\cdot)$ . The early interpolated samples are computed by

$$r((k-1)T) = r((n-1)T_s) + \mu(k)[r(nT_s) - r((n-1)T_s)]$$

(5.5)

and the late interpolated samples are found by

$$r((k+1)T) = r((n+1)T_s) + \mu(k)[r((n+2)T_s) - r((n+1)T_s)]$$

(5.6)

### 5.4 Interpolation Control

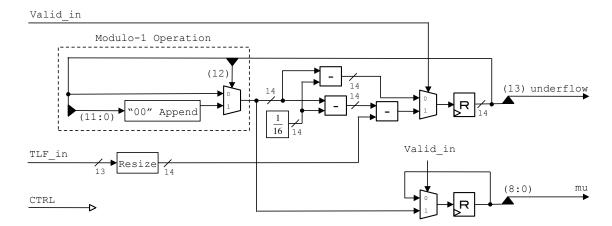

The purpose of the interpolation control block is to provide the interpolator with the k-th basepoint index m(k) and the k-th fractional interval  $\mu(k)$ . For the case of this detector, we base the interpolation control on a modulo-1 decrementing counter. This counter is designed to underflow every N = 16 samples on average, where the underflows are aligned with the sample times of the desired interpolant. A block diagram of this approach is shown in Fig. 5.5.

The discrete-time samples generated by the ADC are clocked into the interpolator with the same clock used to update the counter. With every clock period, the counter decrements by 1/N on average. The loop filter output v(n) adjusts the amount by which the counter decrements. In general, the counter value satisfies

Figure 5.5. A block diagram of the timing synchronizer with the modulo-1 decrementing counter used for interpolation control.

the recursion

$$\eta(n+1) = (\eta(n) - 1/N - v(n)) \mod 1$$

(5.7)

When the decrementing counter underflows, the index n is the basepoint index m(k), as illustrated in Fig. 5.6, and the value of the counter becomes

$$\eta(m(k) + 1) = 1 + \eta(m(k)) - 1/N - v(n)$$

(5.8)

We notice that when the counter underflows, the values  $\eta(m(k))$  and  $1 - \eta(m(k) + 1)$  form similar triangles, which leads to the relationship

$$\frac{\mu(m(k))}{\eta(m(k))} = \frac{1 - \mu(m(k))}{1 - \eta(m(k) + 1)}$$

(5.9)

Solving for  $\mu(k)$ , we obtain

$$\mu(m(k)) = \frac{\eta(m(k))}{\frac{1}{N} + v(n)}$$

(5.10)

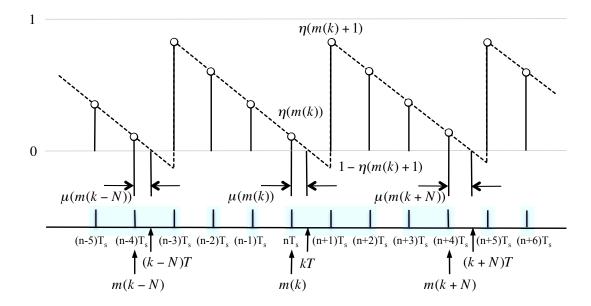

Figure 5.6. Illustration of the modulo-1 decrementing counter underflowing every N samples. In this example, N assumes the value of 4.

When in lock, v(n) is zero on average. Incorporating this consideration into (5.10) produces the final expression for the fractional interval

$$\mu(m(k)) = N\eta(m(k)) \tag{5.11}$$

# Chapter 6

# **Carrier Phase Synchronization**

Carrier phase synchronization is the process of forcing the local oscillators in the detector to oscillate in both phase and frequency with the carrier oscillator used at the transmitter. A carrier phase error causes a rotation in the signal space projections. If the rotation is large enough, the signal space projections for each possible symbol lie in the wrong decision region. Consequently, decision errors occur even with perfect symbol timing synchronization and in the absence of additive noise [14, Ch. 7].

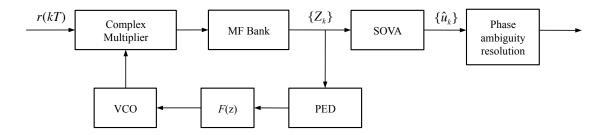

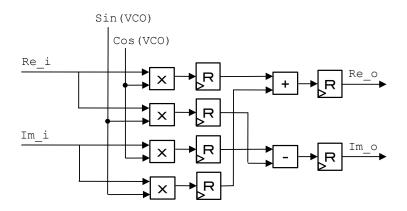

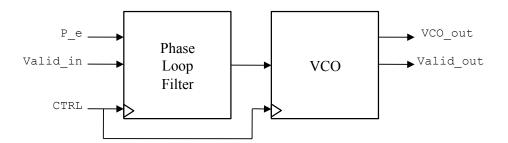

The role of the phase synchronizer is to track any residual phase error remaining in the phase after the phase shifts due to the data are removed by a PLL. A block diagram representation of the phase synchronizer is shown in Fig. 6.1. Here, we assume that the discrete-time sequence r(kT) contains the time-synchronized interpolated samples of the discrete-time signal  $r(nT_s)$ . The complex multiplier rotates these samples in phase by the amount of the most recent carrier phase estimate  $\tilde{\phi}_0$ . Then, the time and phase-synchronized samples are fed to the MF bank, whose output is used within the SOVA, the TED and the *phase error detector* (PED). The PED produces a phase error signal based on the MF outputs.

**Figure 6.1.** A discrete-time approach to phase synchronization for SOQPSK.

This error signal is the input to the loop filter F(z) which drives the discrete-time voltage-controlled oscillator (VCO). The VCO outputs an angle that represents the next carrier phase estimate  $\tilde{\phi}_0$ . At the output of the SOVA, the detector must resolve any phase ambiguity associated with the four possible phase shifts that the PLL can lock on to due to the data. This is discussed at the end of the chapter.

## 6.1 Phase Error Detector

The implementation of the PED is similar to that of the TED. In order to recover the carrier phase  $\phi_0$ , the ML detector temporarily assumes that the symbol timing  $\tau$  and the data symbols sequence  $\boldsymbol{\alpha}$  are known. Using the same definitions from Chapter 4, the likelihood function for (4.1) given a hypothetical phase value  $\tilde{\phi}_0$  over the interval  $0 \leq t \leq T$  is

$$\Lambda(\boldsymbol{r}|\tilde{\phi}_0) = \exp\left\{\frac{1}{N_0}\sqrt{\frac{E}{T}}\operatorname{Re}\left\{e^{-j\tilde{\phi}_0}\boldsymbol{Z}_k(\alpha_k,\tau)e^{-j\theta_k}\right\}\right\}.$$

(6.1)

The ML estimate  $\tilde{\phi}_0$  is the value of  $\phi_0$  that maximizes the logarithm of (6.1), the log-likelihood function. In order to find  $\tilde{\phi}_0$ , we first need to take the partial derivative of the log-likelihood function. Thus, we obtain

$$\frac{\partial}{\partial \tilde{\phi}_0} \log(\Lambda(\boldsymbol{r}|\tilde{\phi}_0)) = \operatorname{Im} \left\{ -j e^{-j \tilde{\phi}_0} \boldsymbol{Z}_k(\alpha_k, \tau) e^{-j\theta_k} \right\}$$

(6.2)

where the ML estimate  $\tilde{\phi}_0$  is the value of  $\phi_0$  that forces (6.2) to zero.

Contrary to timing synchronization, in this case, the imaginary part of the MF outputs is forced to zero. This is because of the multiplication of the -j term, which results from the derivative of  $e^{-j\tilde{\phi}_0}$ , with the real and imaginary arguments of  $\mathbf{Z}_k(\cdot)$ .

Similarly to timing synchronization, the value  $\tilde{\phi}_0$  is computed in an iterative and adaptive way. Initially, it was assumed that  $\boldsymbol{\alpha}$  and  $\tau$  are known, which is not the case. Therefore, two close approximations are used to substitute these values. The true data sequence  $\boldsymbol{\alpha}$  is replaced with the estimated decisions  $\hat{\boldsymbol{\alpha}}$  within the SOVA, and the true symbol timing  $\tau$  is replaced with the most recent symbol timing estimate  $\hat{\tau}$  from the timing synchronizer described in Chapter 5. These approximations become more reliable the further we trace back along the trellis. Considering all these factors, the following phase error signal is obtained

$$e_{\phi_0}[k-D] \triangleq \operatorname{Im}\left\{-je^{-j\hat{\phi}_0[k-D]}\boldsymbol{Z}_{k-D}(\hat{\alpha}_{k-D},\hat{\tau}[k-D])e^{-j\hat{\theta}_{k-D}}\right\}$$

(6.3)

where the delay in computing the error is assumed to be D = 1 to be consistent with Chapter 5.

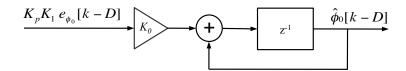

### 6.2 Loop Filter

The transfer function for the loop filter in consideration is F(s) = k. This is a simple gain and produces a first-order PLL. A block diagram of the loop filter is shown in Fig. 6.2, where  $K_p = 1$  and  $K_1 = 0.0026$ .

**Figure 6.2.** A block diagram of the simple gain loop filter F(s).

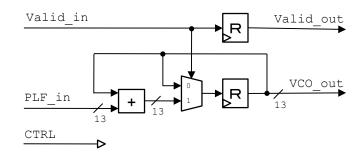

## 6.3 Voltage-Controlled Oscillator

The transfer function of the VCO in consideration is  $F(s) = K_0/s$ , where  $K_0 = 1$  is the VCO gain. This is a discrete-time accumulator that stores the running sum of its input. The sum that is stored within the VCO corresponds to the instantaneous phase of the phase error signal produced by the PED. The output of the VCO is the angle corresponding to the next phase error estimate  $\hat{\phi}_0[k-D]$ . A block diagram representation of the VCO is shown in Fig. 6.3.

**Figure 6.3.** A block diagram representation of the voltage-controlled oscillator (VCO).

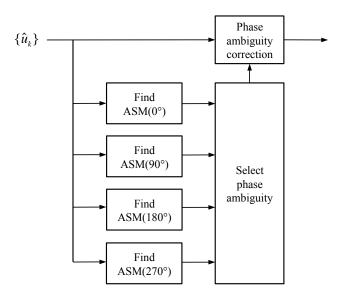

# 6.4 Phase Ambiguity Resolution

Similarly to QPSK modulation, SOQPSK exhibits a 90° phase ambiguity. Consequently, the PLL in the phase synchronizer can lock in four different ways with the carrier. It can lock in phase with the carrier, 90° out of phase with the carrier, 180° out of phase with the carrier, or 270° out of phase with the carrier [14, Ch. 6]. If the phase ambiguity is not resolved, decision errors will occur because the symbols constellation will be rotated.

One way of resolving phase ambiguity is by inserting a unique pattern of known symbols (or "attached synch marker" - ASM) in front of the binary sequence  $\{u_k\}$ . In the receiver, after the carrier phase has been locked, the detector searches for the four possible ASM rotations using a correlation operation, and corrects the phase ambiguity by inverting the appropriate bits according to the detected ASM rotation. A block diagram representation of the phase ambiguity resolution process is shown in Fig. 6.4.

Figure 6.4. Block diagram representation of phase ambiguity resolution for SOQPSK.

# Chapter 7

# Hardware Implementation

This chapter outlines a detailed hardware implementation of the coherent SOQPSK-TG demodulator described in Chapters 4, 5 and 6. An overview of the proposed design is provided first, followed by a comprehensive description of each hardware component.

## 7.1 Design Overview

#### 7.1.1 Inputs and Outputs

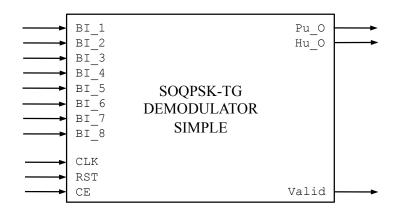

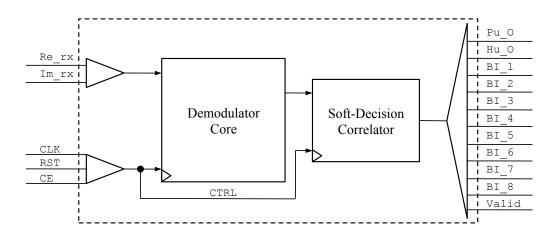

The description of the design begins with a look at the inputs and outputs to the demodulator. As mentioned in Chapter 3, the iterative decoding schemes targeted by the HFEC project require the implementation of two versions of the demodulator. The full version, which can handle timing and phase synchronization, as well as sequence estimation, is the focus of this chapter. On the other hand, the simple version, which only performs sequence estimation, is not described here as it can be easily deducted from the design of the full version. An illustration of the inputs and outputs of the full demodulator is shown in Fig. 7.1.

|               | Re_rx<br>Im_rx<br>CLK<br>RST | SOQPSK-TG<br>DEMODULATOR<br>FULL | Pu_O<br>Hu_O<br>BI_1<br>BI_2<br>BI_3<br>BI_4<br>BI_5<br>BI_6<br>BI_7<br>BI_8 |  |

|---------------|------------------------------|----------------------------------|------------------------------------------------------------------------------|--|

| $\rightarrow$ | CE                           |                                  | Valid                                                                        |  |

**Figure 7.1.** A black box view of the full version of the SOQPSK-TG demodulator.

The inputs to the full version of the demodulator are:

- The information inputs: Re\_rx, Im\_rx. These are the real and imaginary components of the received signal. They are obtained through the processes of sampling and downconversion explained below, and are quantized using eight bits with four bits being fractional.

- *The clock signal*: CLK. This signal provides a common time reference to all the components in the design, and it is detected on its rising edge.

- *The reset signal*: RST. This signal sets all registers to zero when it is activated, unless noted otherwise in the description. It is asynchronous and active-high.

- *The clock-enable signal*: CE. This signal controls the flow of information from external components as it only enables the writing operation of all registers when it is activated.

In the hardware descriptions presented below, the group of control signals: CLK, RST and CE, is collectively referred to as CTRL.

**Figure 7.2.** A black box view of the simple version of the SOQPSK-TG demodulator.

The outputs of the full version of the demodulator are:

- The information outputs: Pu\_O, Hu\_O. These are the soft-decisions (reliabilities) and hard-decisions (bits) about the inner code in the concatenated coding schemes described in Chapter 3. The reliabilities are fed to a second decoder in order to estimate the transmitted bit sequence. The hard-decisions are only used for testing purposes.

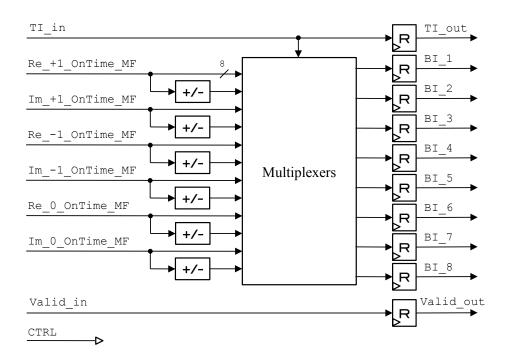

- The branch increment outputs: BI\_1, ..., BI\_8. These are the re-ordered time-synchronized and phase-corrected branch increments that are computed at the output of the matched-filters. They serve as information inputs to the simple version of the demodulator in the second and subsequent iterations of the SCCC decoding scheme. An illustration of the inputs and outputs of the simple demodulator is shown in Fig. 7.2.

- *The output valid signal*: Valid. This signal indicates the output of the demodulator is valid when it is set to one.

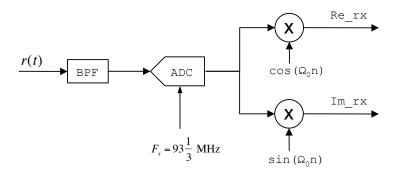

#### 7.1.2 Sampling and Downconversion

The processes of sampling and downconversion are key to understanding the way we extract the information inputs from the received signal r(t). This is a continuous-time band-pass signal centered at the intermediate frequency  $f_0 = 70$  MHz. Along with the desired information, noise is also embedded in the signal, so a band-pass filter is first applied to avoid any aliasing effects of noise outside of the bandwidth region. The sample rate is selected in a way that has advantages in the subsequent I/Q downconversion operation. In a process known as band-pass subsampling, the sample rate is selected so as to force the intermediate frequency to alias to the quarter-sample-rate frequency [14, Ch. 8]. There are multiple sample frequencies that achieve this effect, but for the purposes of this design, a sample rate of  $F_s = 93\frac{1}{3}$  Msamples/s was selected. This sample rate allows for a maximum usable bandwidth of 46.6667 MHz, which is well above the system's requirement.

Figure 7.3. Block diagram representation of signal sampling and I/Q downconversion.

As it was mentioned above, the selected sample rate of  $F_s = 93\frac{1}{3}$  Msamples/s, has the effect of aliasing the intermediate frequency spectrum of r(t) down to the quarter-sample-rate frequency  $f'_0 = \frac{1}{4}F_s$ . When this is the case, we obtain

$$\Omega_0 = \frac{2\pi f_0'}{F_s} = \frac{\pi}{2} \tag{7.1}$$

so that the I/Q downconversion mixers:  $\cos(\Omega_0 n)$  and  $\sin(\Omega_0 n)$ , assume only three trivial values:

Table 7.1.I/Q downconversion mixers.

| n              | 0 | 1 | 2  | 3  | 4 | 5 |  |

|----------------|---|---|----|----|---|---|--|

| $\cos(n\pi/2)$ | 1 | 0 | -1 | 0  | 1 | 0 |  |

| $\sin(n\pi/2)$ | 0 | 1 | 0  | -1 | 0 | 1 |  |

The fact that the I/Q downconversion mixers only assume the 0,  $\pm 1$  values, represents a considerable simplification in the hardware implementation. This is, instead of requiring real multiplications to implement the two frequency translations in Fig. 7.3, they only require simple sign-alterations. The result of the mixing operation is that r(t) is frequency shifted down to baseband.

In this way, the first ADC sample becomes the real input with zero being the imaginary input. Then, the second ADC sample becomes the imaginary input with zero being the real input. After this, the negative of the third ADC sample becomes the real input with zero being the imaginary input. And finally, the negative of the fourth ADC sample becomes the imaginary input with zero being the real input. This pattern is repeated for the remainder of the ADC samples. Any additional phase rotation introduced in the received signal as a product of the downconversion process is measured and corrected by the phase synchronizer.

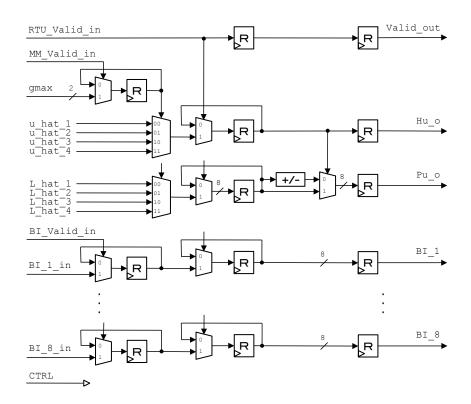

Figure 7.4. Internal structure of the demodulator.

#### 7.1.3 Demodulator Structure

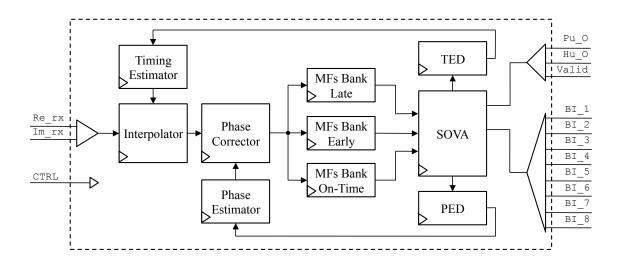

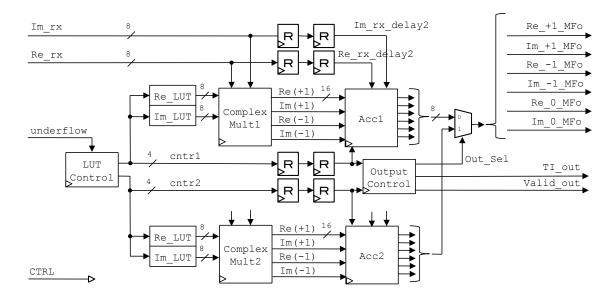

A first-level view of the demodulator structure reveals two major components, as illustrated in Fig. 7.4. These are the *demodulator core* and the *soft-decision correlator*. As the name suggests, the demodulator core is the most extensive and important component in the design. It encompasses all the modules responsible for timing and phase synchronization, as well as, sequence estimation. A detailed view of the demodulator core is given below. The soft-decision correlator serves two essential purposes. The first one is finding the beginning of a frame in the decoded data stream, and the second one is resolving any phase ambiguity in the output data. It does so by performing a correlation of the soft-decisions generated by the demodulator core and a known sequence of bits attached at the beginning of each frame. A detailed hardware description of this module is given in Section 7.10.

A second-level view of the demodulator reveals the internal structure of the demodulator core, as illustrated in Fig. 7.5. Notice how the CTRL signal is not shown directly connected to every module; instead, it is represented with a triangle

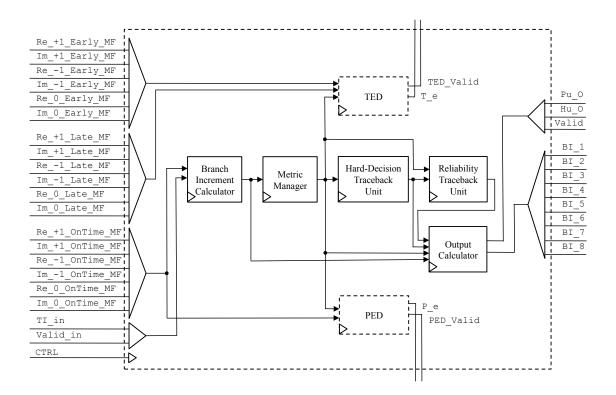

Figure 7.5. Internal structure of the demodulator core.

on their lower left corner. This is done with the purpose to make hardware diagrams easier to read. The internal structure of the demodulator core has been broken down into individual pieces, each one responsible for a separate task. The components that comprise the timing synchronizer are the timing error detector (TED), the timing estimator, and the interpolator. On the other hand, the ones that comprise the phase synchronizer are the phase error detector (PED), the phase estimator, and the phase corrector. And finally, the ones that make up the sequence detector are the matched-filters (MFs) bank, and the soft-output Viterbi algorithm (SOVA).

The information inputs are first processed by the interpolator, which generates a sequence of samples that are aligned with the optimum sampling instances. Also, it produces two additional sequences which represent samples at the early and late sampling moments. The timing estimator, which is comprised by the timing loop filter and the modulo-1 decrementing counter, uses the latest timing error signal from the TED to generate two pieces of information. The first one is the fractional interval mu, which indicates the optimum sampling instances to the interpolator. And the second one is the underflow strobe, which signals a new symbol boundary.

The three time-synchronized sequences produced by the interpolator are then processed by the phase corrector, which removes any phase error according to the phase estimator. The phase estimator, which is comprised by the phase loop filter and the VCO, uses the latest phase error signal from the PED to generate an instantaneous phase estimate. The phase corrector rotates the phase of its input by this amount to produce phase-synchronized samples.

The resulting time and phase-synchronized sequences are each passed through their corresponding MFs bank, which are triggered by the underflow strobe. This guarantees that all samples corresponding to one symbol are filtered together. Each MFs bank generates three complex-valued outputs, one for each possible transmitted symbol. They also produce a signal that alternates between zero and one with each new output, that is used as a trellis indicator. The outputs of the on-time MFs bank are converted into branch increments within the SOVA, and are then used to compute branch metrics, delta values and winning branch indexes. The outputs of the other MFs banks and the winning branch indexes are used within the TED and the PED to produce the next timing and phase error signals, respectively. The SOVA computes the bits and reliabilities associated with the maximum likelihood path, and outputs them after a decoding window of 16 time steps. The branch increments are delayed throughout the decoding process to be aligned with their corresponding hard-decisions and soft-decisions at the output.

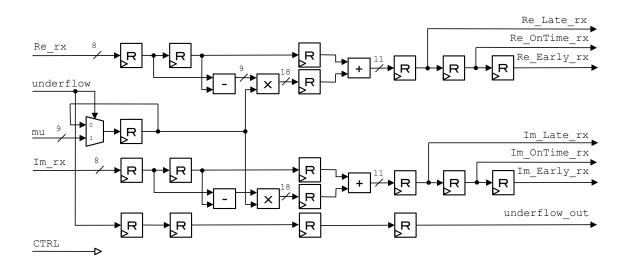

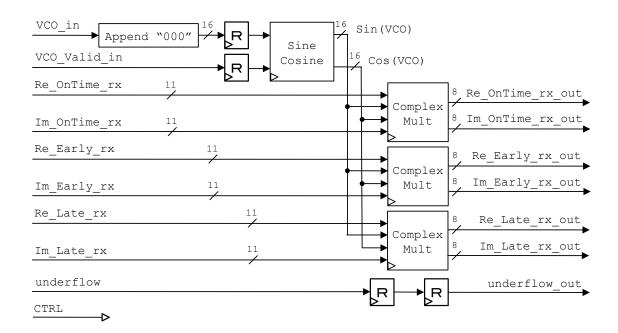

# 7.2 Interpolator

The interpolator is the point of entry of the information inputs to the demodulator. It produces a sequence of samples that are aligned with the optimum sampling instances, as well as two sequences of samples that correspond to the early and late sampling moments. The inputs to the interpolator are:

- Re\_rx, Im\_rx

- underflow

- mu

- CTRL.

And the outputs of the interpolator are:

- Re\_OnTime\_rx, Im\_OnTime\_rx

- Re\_Early\_rx, Im\_Early\_rx

- Re\_Late\_rx, Im\_Late\_rx

- underflow\_out

A hardware representation of the interpolator is shown in Fig. 7.6. The interpolator receives new values of Re\_rx and Im\_rx on the rising edge of every clock cycle. Along with these inputs, it also receives the interpolation control signals underflow and mu, provided by the modulo-1 decrementing counter. Since we are only interested in the value of mu when a new symbol boundary is detected, this input has to be registered. On average, a new symbol boundary is detected every N = 16 clock cycles, and it is indicated by the underflow strobe.

Figure 7.6. Hardware representation of the interpolator.

The information inputs Re\_rx and Im\_rx are interpolated as described in Eq. (5.4). In the case of the real input channel, the interpolation begins by computing the difference between the current input and the previous input. The result is multiplied by the registered value of mu, and then added with the previous input. The resulting value corresponds to the late interpolated sample Re\_Late\_rx, while the one-time and two-times delayed versions of this value correspond to the on-time sample Re\_OnTime\_rx, and the early sample Re\_Early\_rx, respectively. The interpolation process for samples in the imaginary input Im\_rx is identical. The underflow strobe is propagated through the interpolator to later be used in the matched-filters bank.

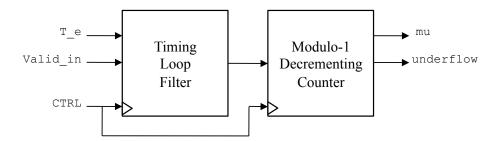

# 7.3 Timing Estimator

The timing estimator is comprised by the timing loop filter and the modulo-1 decrementing counter. It takes in the latest timing error signal from the TED, and produces the interpolation control signals mu and underflow.

Figure 7.7. Block diagram of the timing estimator.

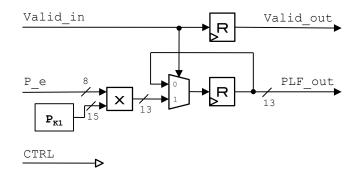

#### 7.3.1 Timing Loop Filter

The timing loop filter (TLF) is responsible for adjusting the timing error signal T\_e that is produced by the TED. Since the timing synchronizer is based on a first-order phase-locked loop (PLL), the adjustment corresponds to a simple gain. The inputs to the TLF are:

- T\_e

- Valid\_in

- CTRL.

And the outputs of the TLF are:

- TLF\_out

- Valid\_out

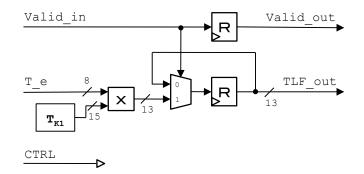

Figure 7.8. Hardware representation of the timing loop filter.

A hardware representation of the TLF is shown in Fig. 7.8. The gain operation performed by the TLF is implemented with a multiplication between the timing error signal T\_e and the PLL constant  $T_{K1}$ . The TLF output TLF\_out is updated only when the input valid signal Valid\_in is set to one. Valid\_in is propagated through the TLF to later be used in the modulo-1 decrementing counter.

The value of the PLL constant  $T_{\mbox{\scriptsize K1}}$  is given by

$$T_{K1} = -0.0026/\pi \tag{7.2}$$