# A UNIFIED HARDWARE/SOFTWARE PRIORITY SCHEDULING MODEL FOR GENERAL PURPOSE SYSTEMS

BY

#### Keith Alan Preston

Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Doctor of Philosophy

| Co-Chairperson: Dr. Arvin Agah    |

|-----------------------------------|

| Co-Chairperson: Dr. David Andrews |

| Dr. Douglas Niehaus               |

| Dr. Andrew Gill                   |

| Dr. Sara Wilson                   |

Date defended: Monday, October 17th, 2011

The Dissertation Committee for Keith Alan Preston certifies that this is the approved version of the following dissertation:

# A UNIFIED HARDWARE SOFTWARE PRIORITY SCHEDULING MODEL FOR GENERAL PURPOSE SYSTEMS

Committee:

| Co-Chairperson: Dr. Arvin Agah    |

|-----------------------------------|

| Co-Chairperson: Dr. David Andrews |

| Dr. Douglas Niehaus               |

| Dr. Andrew Gill                   |

| Dr. Sara Wilson                   |

| Date approved:                    |

#### **Abstract**

Migrating functionality from software to hardware has historically held the promise of enhancing performance through exploiting the inherent parallel nature of hardware. Many early exploratory efforts in repartitioning traditional software based services into hardware were hampered by expensive ASIC development costs. Recent advancements in FPGA technology have made it more economically feasible to explore migrating functionality across the hardware/software boundary. The flexibility of the FPGA fabric and availability of configurable soft IP components has opened the potential to rapidly and economically investigate different hardware/software partitions. Within the real time operating systems community, there has been continued interest in applying hardware/software co-design approaches to address scheduling issues such as latency and jitter. Many hardware based approaches have been reported to reduce the latency of computing the scheduling decision function itself. However continued adherence to classic scheduler invocation mechanisms can still allow variable latencies to creep into the time taken to make the scheduling decision, and ultimately into application timelines. This dissertation explores how hardware/software co-design can be applied past the scheduling decision itself to also reduce the non-predictable delays associated with interrupts and timers. By expanding the window of hardware/software co-design to these invocation mechanisms, we seek to understand if the jitter introduced by classical hardware/software partitionings can be removed from the timelines of critical real time user processes. This dissertation makes a case for resetting the classic boundaries of software thread level scheduling, software timers, hardware timers and interrupts. We show that reworking the boundaries of the scheduling invocation mechanisms helps to rectify the current imbalance of traditional hardware invocation mechanisms (timers and interrupts) and software scheduling policy (operating system scheduler). We re-factor these mechanisms into a unified hardware software priority scheduling model to facilitate

improvements in performance, timeliness and determinism in all domains of computing. This dissertation demonstrates and prototypes the creation of a new framework that effects this basic policy change. The advantage of this approach lies within its ability to unify, simplify and allow for more control within the operating systems scheduling policy.

# **Contents**

| 1 | Intr     | troduction 12                                    |    |  |  |  |

|---|----------|--------------------------------------------------|----|--|--|--|

|   | 1.1      | Operating Systems: A New Level of Portability    | 12 |  |  |  |

|   | 1.2      | Overhead: The Cost of Portability                | 13 |  |  |  |

|   | 1.3      | Invocation Mechanisms: A Lasting Hardware Legacy | 15 |  |  |  |

|   | 1.4      | Hardware Software Co-design: An Answer?          | 16 |  |  |  |

|   | 1.5      | Dissertation Contributions                       | 17 |  |  |  |

| 2 | Bacl     | kground                                          | 19 |  |  |  |

|   | 2.1      | Timers                                           | 24 |  |  |  |

|   | 2.2      | Interrupts                                       | 24 |  |  |  |

|   | 2.3      | Linux                                            | 26 |  |  |  |

|   | 2.4      | Hardware Schedulers                              | 29 |  |  |  |

| 3 | Solution |                                                  | 34 |  |  |  |

|   | 3.1      | Problem Statement                                | 34 |  |  |  |

|   | 3.2      | Hybridthreads                                    | 34 |  |  |  |

|   |          | 3.2.1 Memory Mapped I/O                          | 36 |  |  |  |

|   |          | 3.2.2 Thread Manager                             | 38 |  |  |  |

|   |          | 3.2.3 Hardware Thread Interface (HWTI)           | 39 |  |  |  |

|   |          | 3.2.4 Thread Scheduler                           | 41 |  |  |  |

|   |                 | 3.2.5                                   | Linux Software Modifications                                                                                                                                     | 14                               |

|---|-----------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|   |                 |                                         | 3.2.5.1 Data Structures                                                                                                                                          | 45                               |

|   |                 |                                         | 3.2.5.2 Functions Modifications                                                                                                                                  | 15                               |

|   |                 | 3.2.6                                   | Synchronization Manager                                                                                                                                          | 16                               |

|   |                 | 3.2.7                                   | Condition Variable Manager                                                                                                                                       | 47                               |

|   | 3.3             | Extens                                  | ons to Hybridthreads                                                                                                                                             | 48                               |

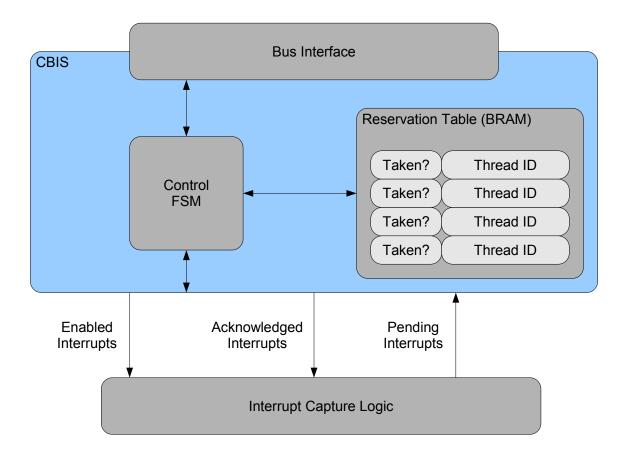

|   |                 | 3.3.1                                   | CPU Bypass Interrupt Scheduler (CBIS)                                                                                                                            | 49                               |

|   |                 |                                         | 3.3.1.1 Overview                                                                                                                                                 | 5(                               |

|   |                 |                                         | 3.3.1.2 Hardware Implementation                                                                                                                                  | 51                               |

|   |                 |                                         | 3.3.1.3 Software Implementation                                                                                                                                  | 55                               |

|   |                 | 3.3.2                                   | Timer Core                                                                                                                                                       | 57                               |

|   | 3.4             | Unifie                                  | Interrupt and Scheduling Controller                                                                                                                              | 58                               |

|   |                 |                                         |                                                                                                                                                                  |                                  |

| 4 | T71             | l <b>4.º</b>                            |                                                                                                                                                                  | -                                |

| 4 | Eval            | luation                                 |                                                                                                                                                                  | 65                               |

| 4 | <b>Eval</b> 4.1 |                                         | ncy (                                                                                                                                                            |                                  |

| 4 |                 |                                         |                                                                                                                                                                  | 67                               |

| 4 |                 | Efficie                                 | ncy                                                                                                                                                              | 67<br>67                         |

| 4 |                 | Efficie                                 | Base Operation Timings                                                                                                                                           | 67<br>67<br>68                   |

| 4 |                 | Efficie 4.1.1                           | Dase Operation Timings       6         4.1.1.1 Analysis       6                                                                                                  | 67<br>67<br>68                   |

| 4 |                 | Efficie 4.1.1 4.1.2                     | Base Operation Timings                                                                                                                                           | 67<br>67<br>68<br>70             |

| 4 |                 | Efficie 4.1.1 4.1.2                     | Base Operation Timings                                                                                                                                           | 67<br>68<br>70<br>71             |

| 4 |                 | Efficie 4.1.1 4.1.2                     | Base Operation Timings                                                                                                                                           | 67<br>68<br>70<br>71<br>72       |

| 4 |                 | Efficie 4.1.1 4.1.2 4.1.3               | Base Operation Timings                                                                                                                                           | 67<br>67<br>68<br>70<br>71<br>72 |

| 4 |                 | Efficie 4.1.1 4.1.2 4.1.3               | Base Operation Timings 4.1.1.1 Analysis 6  Overhead of an Interrupt 7  4.1.2.1 Analysis 7  Hackbench 7  4.1.3.1 Analysis 7  Dhrystone MIPS 7                     | 67<br>68<br>70<br>71<br>72<br>74 |

| 4 | 4.1             | Efficie 4.1.1 4.1.2 4.1.3 4.1.4 Control | Base Operation Timings 4.1.1.1 Analysis 6  Overhead of an Interrupt 7  4.1.2.1 Analysis 7  Hackbench 7  4.1.3.1 Analysis 7  Dhrystone MIPS 7  4.1.4.1 Analysis 7 | 67<br>67<br>68<br>70<br>72<br>72 |

| Bibliography |            |           |                             | 85 |

|--------------|------------|-----------|-----------------------------|----|

| 5            | Conclusion |           |                             | 82 |

|              |            | 4.2.3.1   | Analysis                    | 81 |

|              | 4.2.3      | Balancin  | g Processing and Interrupts | 79 |

|              |            | 4.2.2.1   | Analysis                    | 79 |

|              | 4.2.2      | Cost of a | Timers                      | 77 |

# **List of Figures**

| 1.1  | Operating System Abstractions                 | 13 |

|------|-----------------------------------------------|----|

| 2.1  | Traditional Scheduler Model                   | 27 |

| 3.1  | Hybridthreads Design                          | 35 |

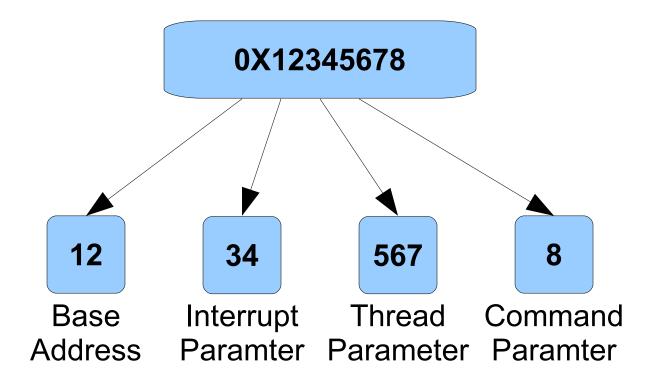

| 3.2  | Address Map                                   | 37 |

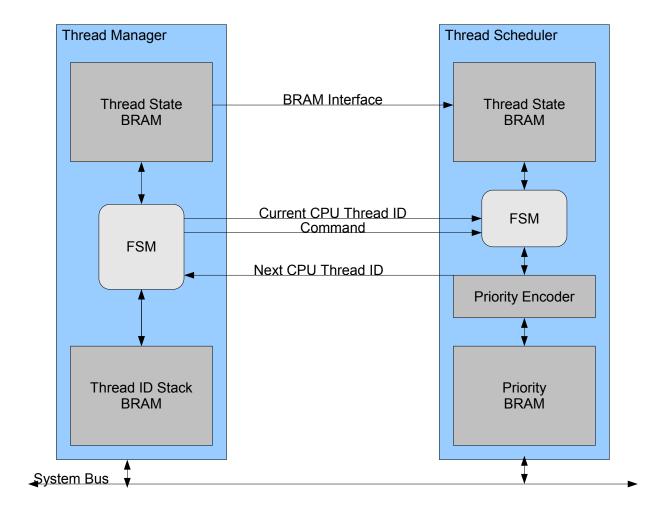

| 3.3  | Block Diagram of Thread Manager and Scheduler | 40 |

| 3.4  | CPU Bypass Interrupt Scheduler                | 49 |

| 3.5  | CBIS Address Breakdown                        | 52 |

| 3.6  | CBIS Interrupt Logic Diagram                  | 54 |

| 3.7  | Memory Mapped I/O Macro                       | 55 |

| 3.8  | CBIS Interrupt Loop                           | 56 |

| 3.9  | Associate Call                                | 56 |

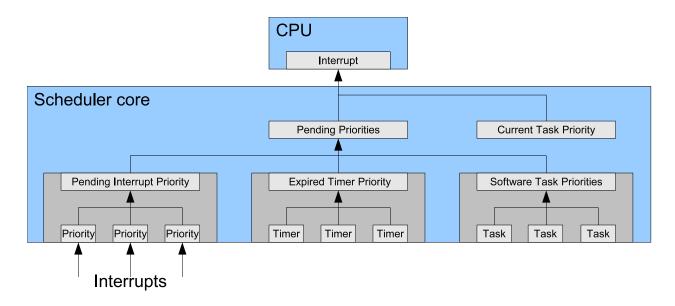

| 3.10 | Unified Scheduler Model                       | 58 |

| 3.11 | Unified Scheduler Interrupt Controller        | 60 |

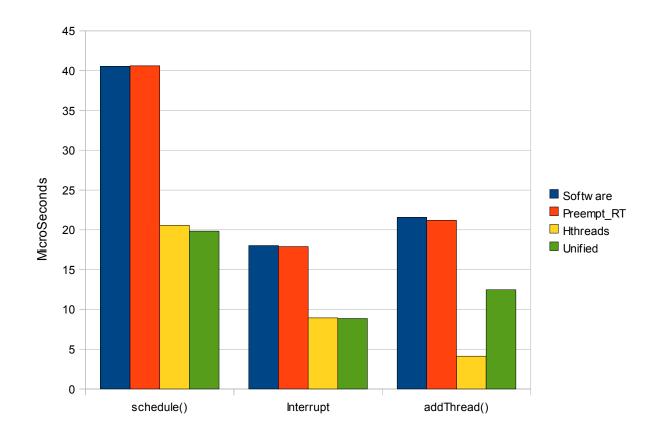

| 4.1  | Base Operation Timings                        | 69 |

| 4.2  | Overhead of Interrupt                         | 71 |

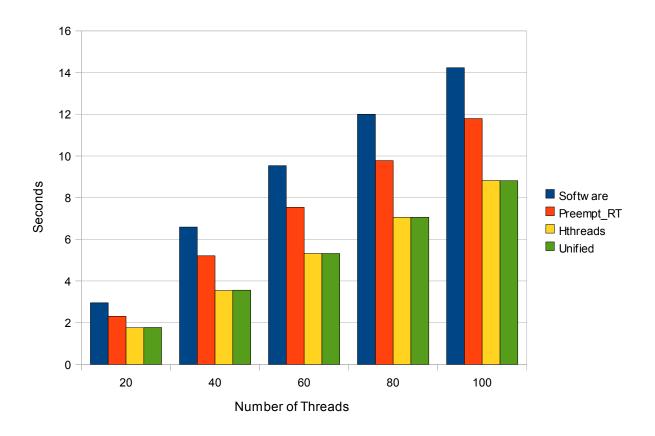

| 4.3  | Hackbench                                     | 73 |

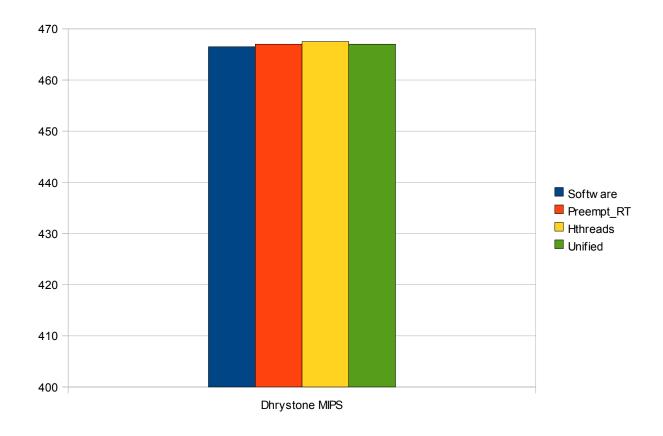

| 4.4  | Dhrystone MIPS                                | 74 |

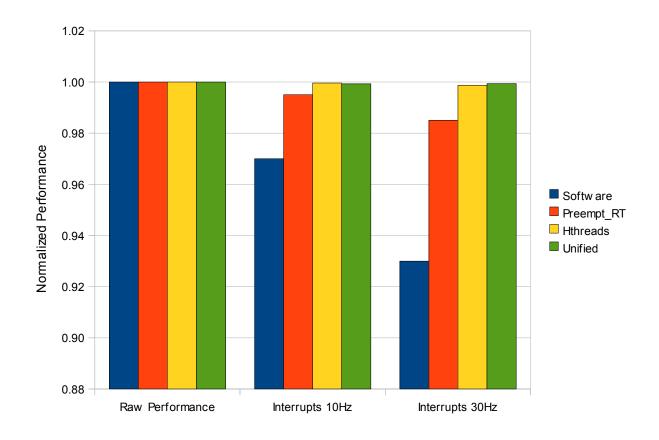

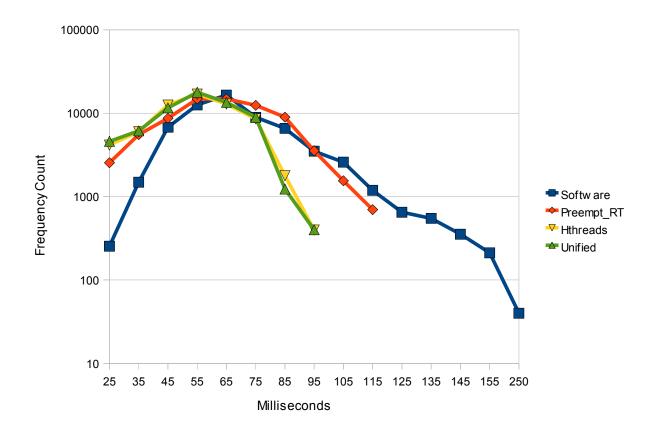

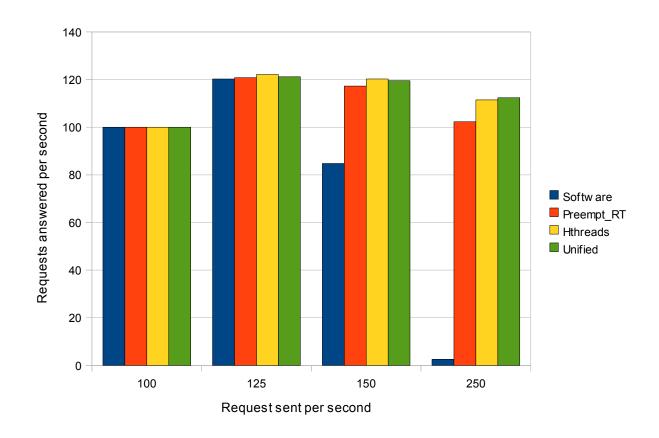

| 4.5  | Apache Benchmark                              | 76 |

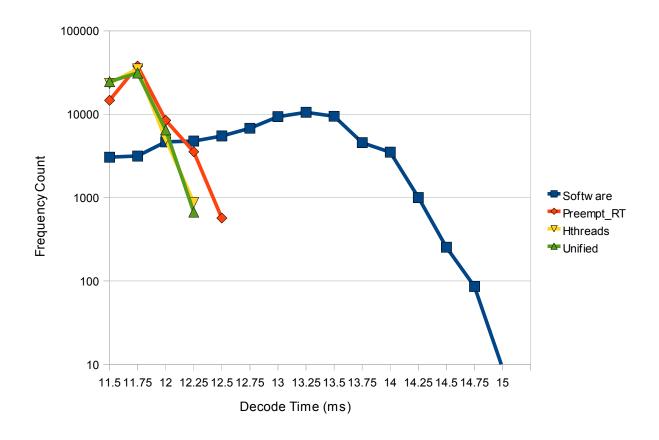

| 4.6 | Cost of a Timer    | 8 |

|-----|--------------------|---|

| 4.7 | Interrupt Overload | 0 |

# **List of Tables**

| 3.1  | Thread Status and Identifier BRAM Layout           | 39 |

|------|----------------------------------------------------|----|

| 3.2  | Thread Manager Commands                            | 41 |

| 3.3  | Thread Manager and Thread Scheduler Shared Signals | 42 |

| 3.4  | Thread Scheduling Parameter BRAM                   | 42 |

| 3.5  | Priority BRAM                                      | 43 |

| 3.6  | Thread Scheduler Commands                          | 44 |

| 3.7  | Modified Scheduler Functions                       | 45 |

| 3.8  | Mutex BRAM                                         | 46 |

| 3.9  | Thread BRAM                                        | 46 |

| 3.10 | Synchronization Manager Commands                   | 47 |

| 3.11 | Condition Variable Manager Commands                | 48 |

| 3.12 | CPU Bypass Interrupt Scheduler Commands            | 50 |

| 3.13 | CBIS BRAM                                          | 50 |

| 3.14 | Xilink IPIC Bus Interface[1]                       | 62 |

| 3.15 | CBIS FSM states                                    | 63 |

| 3.16 | Xilink BRAM Interface[2]                           | 63 |

| 3.17 | Timer Commands                                     | 63 |

| 3.18 | Unified Scheduler Commands                         | 64 |

| 4.1  | Test Systems                                       | 66 |

| 4.2 | Test Scenarios               | 67 |

|-----|------------------------------|----|

| 4.3 | Apache Benchmark Averages    | 75 |

| 4.4 | Cost of a Timer Averages     | 79 |

| 5.1 | Hybridthreads Hardware Sizes | 82 |

| 5.2 | Unified Hardware Size        | 84 |

### **Terms**

**AB** Apache Benchmark

**AP** Application Process

API Application Programming Interface

**ASIC** Application Specific Integrated Circuit

**BRAM** Block Random Access Memory

**BSP** Board Support Package

**CBIS** CPU-Bypass Interrupt Scheduler

**CFS** Completely Fair Scheduler

**CPU** Central Processing Unit

**DDoS** Distributed Denial of Service

**DoS** Denial of Service

**DSP** Digital Signal Processor

FPGA Field Programmable Gate Array

FSM Finite State Machine

**GB** Gigabyte

**GPOS** General Purpose Operating System

**GPU** Graphics Processing Unit

**HW** Hardware

HWTI Hardware Thread Interface

**IBM** International Business Machines Corporation

**ID** Identifier

I/O Input and Output

IPIC Intellectual Property Interconnect

IRQ Interrupt Request

**ISR** Interrupt Service Routine

**IST** Interrupt Service Thread

KB Kilobyte

**KURT** Kansas University Real Time Linux

LIFO Last In First Out

LITMUSRT Linux Testbed for Multiprocessor Scheduling in Real-Time systems

MB Megabyte

MHZ Megahertz

MIPS Millions of Instructions Per Second

MP3 Moving Picture Experts Group Layer 3 Codec

MPSOC MultiProcessor Systems On Chip

**NAPI** New API

**OPB** On-Chip Peripheral Bus

**OS** Operating System

**O**(1) Of Order 1

O(N) Of Order N

O(log N) Of Order Logarithm of N

PC Personal Computer

**PCT** Processor Control Threads

**PIC** Programmable Interrupt Controller

**POSIX** Portable Operating System Interface for Unix

**SW** Software

**SRAM** Static Random Access Memory

**TCP** Transmission Control Protocol

**RT** Real-time

RTLinux Real-time Linux

**RTM** Real-time Task Manager

**RTOS** Real-time Operating System

**USB** Universal Serial Bus

VGA Video Graphics Accelerator

VHDL Very High-level Design Language

## Chapter 1

### Introduction

#### 1.1 Operating Systems: A New Level of Portability

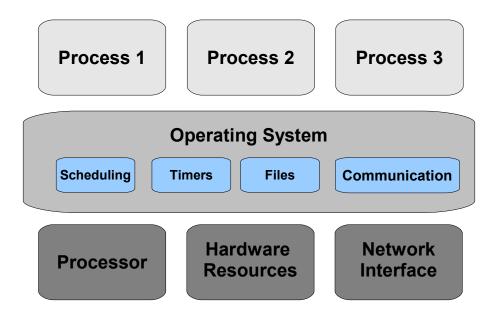

Operating systems are arguably the most fundamental system software component within modern computing systems. A fundamental role of the operating system is to abstract and manage the underlying hardware resources of the system [3]. Operating systems abstract the underlying system hardware resources through the formation of a virtual machine. Client processes interact with the virtual machine through a set of Application Programming Interfaces (APIs). These APIs allow access to the hardware resources.

The role of the operating system as virtual machine traces its lineage back to the pioneering work of the IBM OS/360 [4][5]. The OS/360 was a batch processing operating system made for IBM's System/360 Mainframe computer announced in 1964. IBM's system software designers sought to enable programmers to easily port both legacy and new application code across an emerging family of new machine architectures. This early work freed programmers from having to rework source code to match each different machine's low level platform specific hardware organization. Current operating systems such as Linux and Windows have evolved from this early work to bring the same benefits of portability to all users. The development of operating systems

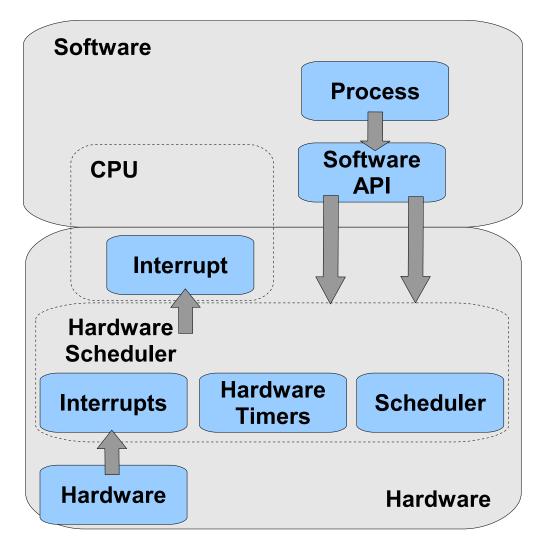

Figure 1.1: Operating System Abstractions

was important because operating systems brought portability, higher level functionality and decreased design time to all types of systems.

### 1.2 Overhead: The Cost of Portability

As a general rule, the benefits of portability and abstractions come at a tradeoff of decreased performance[6]. Operating systems are not immune from this tradeoff. As executable programs, they require processing time that takes away from cycles available for executing the application program. Thus operating system execution time is generally referred to as overhead. The actual overhead incurred by any operating system can vary based on changing system loads, and is also dependent on a machines specific hardware organization.

For a large family of general purpose computing applications, the overhead and variance introduced by the operating system are an acceptable tradeoff when compared to the benefits provided through abstraction and reuse [7]. However, for certain classes of applications, such as

those found in real time systems, the overhead and variance negatively affect the overall quality of service that can be provided by the system. Operating systems researchers of embedded and real time systems have historically sought to deliver operating systems that merge the benefits of portability and abstraction associated with general purpose operating systems, but with reduced latency and minimal jitter necessary for meeting real time requirements [8].

One of the primary resources that operating systems manage is the CPU itself. In today's complex systems, there can often be hundreds of processes competing for time on the CPU. To manage time sharing of processes on the CPU, the operating system runs a scheduling algorithm. Significant research over the last 30 years has been devoted to developing fair and appropriate scheduling algorithms. The scheduler as a program requires CPU cycles to run its scheduling algorithm. Thus, the act of running the scheduler itself can result in performance degradations for the application programs. To minimize this effect user-level thread scheduling frameworks [9] have been developed to allow groups of threads to schedule themselves. These frameworks allow the use of special scheduling algorithms that are optimized for known thread requirements and interactions of the program rather than relying on a one size fits all approach to scheduling.

Others have worked on making the operating system scheduler as fast as possible. Ingo Molnar created a new scheduler in Linux[10], termed the O(1) scheduler, to make scheduling decisions in constant time. The name O(1) can be misleading as the scheduler still has O(n) timings for certain actions such as interrupt processing. However, the most frequent decision of the scheduler, what thread should run next, is constant time, or O(1), with respect to the number of threads in the system. This capability is important for real time systems that require very precise timing of the scheduled applications. Any jitter introduced is essentially unwanted variation in timing for a periodic real time thread [11]. To further lessen the impact of the scheduler, later versions of Linux replaced the O(1) scheduler with the CFS, Completely Fair Scheduler[12]. This scheduler uses a more complex data structure, a red-black tree, to shorten more scheduling operations from O(N) to O(log n).

#### 1.3 Invocation Mechanisms: A Lasting Hardware Legacy

Even though the O(1) scheduler reduces the time taken to run the software scheduling algorithm, additional overhead and variance can still be introduced when the scheduler is invoked using historical invocation mechanisms. As an example, countdown timers are a familiar trigger for invoking a scheduling decision in Linux. In a classic configuration, the timer computes a periodic interrupt that represents a jiffy. During each jiffy interrupt, timers are checked and expired timers are executed[13]. This introduction of time keeping as a service of the operating system causes an additional overhead and variance because of a periodic interrupt.

In addition, interrupts are by definition asynchronous invocation mechanisms, and can have fairly high processing overhead in modern computers[14]. A fundamental problem arises when using interrupts as invocation mechanisms when very precise scheduling is required. The interrupts stop the CPU before determining if a scheduling decision is required. Since some real time threads could be a higher priority than interrupts, stopping the CPU to make a decision causes jitter in the system.

There have been various software approaches used to explore how to lessen the overhead of servicing interrupts. RTLinux[15] attempts to reduce the overhead of interrupts by creating an additional register that allows the system software to quickly determine if the interrupt is attempting to invoke real time or non-real time processing. The PREEMPT\_RT patch[16] for the Linux kernel takes another software approach. This approach queues the interrupt in thread context quickly, returning to a new scheduling decision, and possibly the previous task. These software approaches attempt to minimize the overhead and jitter of checking the interrupt, but they cannot fully eliminate it.

Scheduling policy is actually a combination of two scheduling mechanisms. This is true for most types of computing policies. The policies are first dictated by the design of the hardware they run on, and second, by the design of the software built to run on top of the hardware [17]. In

scheduling policy, design is first dictated by the age old concept of hardware interrupts, and secondly, by the software-based operating system scheduler. The design of the hardware can often limit what is possible with software.

### 1.4 Hardware Software Co-design: An Answer?

This overhead and jitter caused by interrupts and the operating system itself take away processing time and add timing uncertainty into the applications[18]. To eliminate this type of overhead and jitter altogether cannot be achieved through software methods along, and requires modifications to the underlying hardware micro-architecture. While researchers have long been aware of the effects of inefficient invocation mechanisms, and overhead of running the scheduler, the cost of refactoring these functions into special purpose hardware have been prohibitive. Chip manufacturers are understandably reluctant to change baseline hardware designs, as these changes would have an unacceptably large economic impact on system and application software. Creating additional application-specific integrated circuit (ASIC) accelerators can also address the problem, but they generally have non-recurring engineering costs in the millions of dollars range [19] [20].

Recently, modern FPGAs have emerged that contain significant gate densities, diffused components such as processors, and distributed SRAM based memories to form complete multiprocessor systems on chip (MPSoPC) architectures[21]. Many embedded systems designers are turning towards FPGAs to replace more expensive ASICS. FPGAs also represent convenient testbeds for exploring migration of functionality across the software/hardware boundary[22]. Thus FPGA's represent convenient sandboxes that can be used to explore different hardware software partitionings in a quick and cost effective way. The growing adoption of FPGA's as hardware infrastructure within embedded systems then makes any exploratory work performed on an FPGA available for use within these fielded systems. The Hybridthread system[23] is a great

example of this exploration in embedded systems. Through the use of FPGAs the Hybridthreads project has reimagined what an operating system looks like by transitioning many functions into hardware, such as Scheduling, Mutexes and Condition Variables. This dissertation uses an FPGA and the basis of Hybridthreads to explore and propose a new hardware/software repartitioning of the scheduling algorithm, and the invocation mechanisms to enhance the traditional scheduling goals of efficiency, timeliness, and predictability.

We perform our explorations under the constraint of not degrading the benefits associated with portability and software reuse. These benefits have been at historical odds with the timing constraints under which application designers typically must operate within the fields of embedded and real time systems. We believe a new framework can be designed that achieves both attributes by working within the framework of Linux. Our approach is to not alter or change the policies or API interfaces of Linux, but rather the mechanism used to invoke them. This allows our platform to enable desirable real-time capabilities into the general purpose operating system.

To validate the findings in this work, a wide range of tests have been run to evaluate different performance characteristics of the new scheduling framework. The benchmarks have been selected to show the effects on scheduling overhead, multi threaded performance, timing accuracy, interrupt latency, interrupt control, and real time performance. These tests include standard Linux benchmarks and programs such as Hackbench[24] and Apache[25] web server.

#### 1.5 Dissertation Contributions

The contributions of this dissertation are:

- Integrating interrupts into the HybridThreads[26] [27] operating system scheduler

- Porting the HybridThreads operating system kernel to the Linux Platform

- Redesigning the interrupt and scheduler from the HybridThreads operation system into a

unified scheduler to maximize results for lowest hardware cost

• Demonstrating and evaluating the effects of the unified model on common domain specific use cases to previous approaches

## Chapter 2

## **Background**

Operating systems continue to be a important and popular area of research due to their impact on system performance. Recently the switch from scalar to manycore systems has reinvigorated research on how the operating system should be restructured to better support scalable numbers of heterogeneous processor resources. Central to these efforts are how the new requirements of heterogeneous manycores will redefine the role and structure of the scheduler. The historical objective of scheduling threads and processes on a single shared CPU was to increase the overall utilization of the CPU. The switch to heterogeneous manycores is now causing researchers to modify this objective function to minimize application latencies and not simply maximize the utilization of a single shared resource. This is moving the scheduler towards the roll of a dispatcher and bringing in scheduling latency issues that have been a driving scheduling research within the discipline of embedded and real time systems. While traditionally limited to only specialized embedded systems, real time functionality is now been sought in all domains of computing.

There are many different ways to define a real-time system. A popular definition is "A real-time system is one in which the correctness of the system depends not only on the logical result of computation, but also on the time at which the results are generated" [28]. Generally

there are two separate categories of real time, hard real time and soft real time. Hard real time is when a missed deadline results in catastrophic failure, like the loss of life. Soft real time is when missed deadlines generally result in bad user experience, such as skipping frames in multimedia video. Operating systems are striving to be better equipped to handle real time tasks by improving real time operating system performance metrics that include task switch time, interrupt latency, preemption time, system call processing time, and overall run-time efficiency[29].

Another reoccurring theme in operating system research is the need for flexibility in design and implementation of operating systems. A research operating system, K42 [30], was made to show this need. This research operating system is designed for flexibility and monitoring. Its subsystems are replaceable, and the core system has the monitoring infrastructure to rapidly evaluate new research ideas. It has shown the fault of today's operating system in their utilization of nonflexible techniques like global data structures and global policies. K42 is only one of many other research operating systems, like Exokernel [31], Spin [32], Vino [33] which illustrate similar weaknesses in current operating system approaches.

Flexible component based operating systems generally start with a very small, fast and efficient core, and expand on this through additional components. The SPACE project [34] takes this approach in a new operating system abstraction, and is identified as a sub-micro kernel. It takes scheduling out of the base kernel, aside from a very simple priority mapping of processes groups, and lets an application decide its interaction inside the process group. This can be beneficial from an application stand point as it can define the interaction between its threads. Priority, and other scheduling models, may not extract maximum performance from these applications.

A lot of the need for flexibility in an operating system comes from the additional overhead incurred by every additional component. This has become apparent in super computer designs.

Recent studies[35] have even shown that operating system overhead on supercomputing clusters affect performance so much that if a system is designed to dedicate and isolate operating system

overhead, they can often achieve higher performance. This is done by designating one processor of a multiprocessor node to not perform normal computation and only handle operating system tasks, rather then trying to distribute the task to node running the application.

Another group, lead by Jean-Charles Tournier[36], has discussed the flexibility of an a-la-carte operating system, or an operating system that can be dynamically built with the services needed by the system. This way, systems such as supercomputers, the example in the paper, have a more flexible model to eliminate costly scheduling algorithms, software timers, time slicing or other unneeded components. They discuss Puma[37], a lightweight operating system for massively parallel systems developed at Sandia National Laboratories. Puma is a small operating system consisting of the quintessential kernel (Q-Kernel), the process control thread (PCT) and the application processes(AP). This design allows for adaptation and elimination of the PCT, or scheduling thread, if the system calls for it.

In a newer approach to supercomputing, the BEE2 project[38] has looked at a massively temporal and spatial parallel system consisting of FPGAs. They have discussed many problems from their concept of stream-based computing. The most notable is that the high bandwidth nature of data through FPGAs causes hard real-time requirements into operating systems and applications. Without real-time processing, the CPU backs ups requests and must pause the FPGA from processing to catch up. Most of these real time requirements come from message passing. The predictability of operating systems highly affect message passing performance, as the slowest node of a computational cluster will cause others to idle to its speed during synchronization. To avoid problems they have even chosen to only run the Linux kernel on one node per board of five FPGAS. The other FPGAs run a micro kernel that is a slave to the Linux FPGA to help better keep real-time requirements.

Another example of the effect of scheduling overhead is the HPC-Colony project[39], a collaboration between Lawrence Livermore National Laboratory, the University of Illinois and IBM which is funded by the Department of Energys Office of Science under the FastOS

program[40]. This project is focused on services and interfaces for systems with 100,000+ processors. The project clearly defines problems in supercomputing domains with respect to operating systems. They point out that Operating System processes and scheduling are much too coarse-grained to allow accurate load balancing. In fact, the time wasted by the scheduler in deciding the load balance often negates the benefit of load balancing.

In the same manner that super computing application exposes scheduling issues, multi threading has many issues with respect to the scheduler[41]. Unfortunately, these are exceedingly hard to quantize because of non-determinism of multi threaded systems. Projects, such as LITMUSRT (Linux Testbed for multiprocessor Scheduling in Real-Time systems)[42], have developed entire systems just to try and predictably measure this non-determinism. They establish that the four sources of overhead of relevance are task preemption, migration costs, context switching and scheduling overhead. They specifically leave out interrupts, going to lengths to try and avoid them and other background activities in their system. They do this by booting into single user mode to start only a minimal set of tasks. They establish in multiprocessor systems that migration costs between processors have the highest impact in terms of performance. Preemption and scheduling overhead are identified as sources for easy improvement because they cause performance issues when scaling algorithms from tens to thousands of cores.

With respect to real-time systems, most traditionalists have ignored multi threading and multiprocessor systems due to the lack of predictability inherent in the asynchronous models. Some use multiprocessor systems, but limit the real-time applications to run on an isolated CPU[43]. Redhawk Linux[44] is another example that uses this shielded processor approach to achieve sub 1 millisecond response times on Linux. This helps to deal with the scalability issues on scheduling algorithms on significant number of processor[45]. Recent work on this area[41] suggests that solutions to this problem involve a move to deterministic switching and scheduling, allowing multiple real-time tasks to complete deterministically, if deadlines have been proved feasible.

Most of this research points toward the idea of a low latency scheduler. Most future direction of scheduling based research is summed up well by a group at Princeton University[46]. They reiterate the idea of a new hardware/software contract. Software is to expose as much parallelism through threads, and hardware is suppose to provide facilities to provide low latency scheduling so as to not hinder multi threaded software. It is expressed as a chicken and egg problem. Due to the overhead of multi threading, software developers often do not develop multi threaded software because it can often be slower than single threaded software. This is generally true only when the number of threads is greater than the number of cores available. In the same way, hardware designers are reluctant to design high numbers of cores into processors because software cannot yet use them efficiently.

Most experts agree that to properly make a low latency scheduler, hardware must be utilized[47]. Migrating operating system functionality into hardware is not a new approach used in the world of computing. Virtual Memory is a great example of another subsystem that has a hardware component. This is generally due to the high cost of a software implementation. Virtual memory in software requires twice the amount of memory accesses. One memory access is to look up the translation from virtual to physical, and the additional access is to read the physical memory. However, with a processor memory unit, this cost is greatly reduced when a cache hit is made. Performance is not the only benefit of hardware. Power issues, a key in the embedded market, has given support for operating system hardware development. As embedded devices strive for power efficiency, they look to the obvious advantage of hardware over software in this realm. Elais T. Silva Jr et al. [48] show many reasons for the case of middleware services in hardware. They have developed a hardware core for Task Scheduling and Communication on top of the Java Real Time Specification and the FemtoJava Processor. They find that a hardware scheduler gives a more fine grain control to throttling processors, and can significantly increase energy savings and battery life.

#### 2.1 Timers

Research in scheduling affects other areas, especially the area of timers. This is because the design of most general purpose operating systems use periodic timers to regain control of the system and measure the passage of time. This is quickly being determined as inefficient by many recent efforts because this is a use of timers to do synchronous polling, which is known to be inefficient as compared to asynchronous interrupts.

Many describe this as the failure of the timing tick[49]. The tick fails mostly due to the resolution of the timer. For example Unix 6 in 1976 used a tick rate of 60 hz[50]. While this has increased slightly, it is common for operating systems to have a 100 hz timer frequency. This has been nearly unchanged for decades. This leads to failure in multiple arenas[51]. In the embedded environment, power consumption has been tied to periodic timers. Every tick in the system must wake up and waste power while taking care of operating system components dependent on the tick. The solutions for the failure of the timer tick all point to eliminating this polling at an operating system level and pushing it down to the hardware. This is done with one-shot timers, although some operating system components need to be redesigned to work with them. These timers along with other operating system overhead eliminate help to reduce System Noise[52] to a minimum.

#### 2.2 Interrupts

Interrupts, since their invention, have been both a blessing and a curse to real-time designers. Although originally designed to facilitate real-time functionally by reducing latency through their asynchronous nature, they have inherent drawbacks from a software point of view[53]. They are generally non-portable across compilers and hardware platforms. Interrupts tend to expose race conditions in software due to unpredictability. There is a need to design interrupts and interrupt software in a safe and structured way. As more real time tasks move into software, even more care

is needed to interact with interrupts. One manifestation of interrupt problems is interrupt overload[54]. Newer hardware interfaces, such as the Universal Serial Bus(USB)and Gigabit Ethernet, have high requirements on maximum interrupt frequency. Respectively, they can generate on the order of 100,000 and 1,000,000 interrupts a second, and can pose significant challenges for real-time systems[55]. This can cause many system problems, including the highly publicized denial of service attacks. These attacks take form when enough persistent network traffic causes millions of interrupts, exposing faults in how the operating system deals with scheduling these interrupts, and processing network data. Some work has been done to mitigate these effects in software. The Linux kernel has added the NAPI ("New API")[56] as a device packet processing framework that can switch drivers into polling mode during periods of high traffic.

Care must, also, be taken in the testing of interrupts. Tests designed to test interrupts should be random in nature[57]. They should be done with random uncorrelated events and stress the system to help establish failure events. Current interrupt semantics challenge predictability and timeliness by allowing asynchronous interrupts to temporarily stop the execution of the application program. This, in return, introduces additional delays in terms of costly exception processing and context switching. The performance degradation due to context switches will continue to grow as next generation CPUs, with ever deeper pipelines and hierarchical caches, introduce more states that must be saved during a context switch. Additionally, the interrupt requests are serviced outside the system scheduler, and are not deterministically considered with threads and processes within the ready-to-run scheduler queue.

There are three approaches to minimizing this effect. An operating system can process the whole interrupt every time it is stopped. A simple approach, but causing lots of jitter to threads at the advantage of short interrupt latency.

Most research in real-time operating systems (RTOSs) attempt to minimize the overhead of exception processing and reduce the nondeterministic jitter by only executing a small portion of

the interrupt service, routing the "top half" of the routine. This top half typically saves data to a buffer and schedules the "bottom half" to process the data. This approach is a balance of thread latency versus interrupt latency.

Lastly, the PREEMPT\_RT patch for Linux and other efforts [58] [59] simply marks an interrupt as an enqueue thread operation and continues. Unfortunately, this approach must allow the asynchronous request to occur and suffer the overhead and jitter of marking the interrupt as pending. Due to the adherence of the current interrupt semantics, research in pure software-based techniques has reached a plateau. This approach sacrifices interrupt latency significantly in efforts to lower thread latency. The latency of ISR can become 3-10 times higher even if parts of the ISR processing are outsourced to an external co-processor[60].

Research efforts like the SLOTH kernel[61] [62] take the opposite approach. Rather than moving interrupts into thread context, they have moved threads into interrupt context. This avoids interrupt latency, the main penalty of moving interrupts into thread. In fact, it shrink overall latency considerably, considering the system scheduler becomes a multiple priority level interrupt controller. It does have a few major drawbacks in that it is limited to the number of threads by the interrupt levels in a system, and all threads must have a run to completion semantics without blocking.

### 2.3 Linux

This plateau of software schedulers is now commonly found in general purpose schedulers. A great example of a general purpose scheduler can be seen in the Linux operating system. Linux was originally created by Linus Torvalds for use on his personal computer. It has since become a community open source effort, and today reflects a lot of the widely accepted ideas about what an operating system should be. It, currently, has made much progress in both the server and embedded market, along with the original desktop market for which it was written. Its scheduler

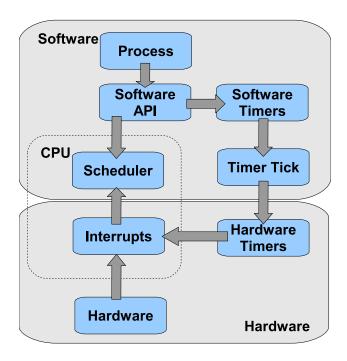

Figure 2.1: Traditional Scheduler Model

has many artifacts of the original hardware interrupt semantics, most notably the introduction of softirqs and tasklets. Softirqs and tasklets are typically used in the traditional top and bottom half interrupt paradigm. While the initial processing of an IRQ is in a dedicated response handler, the majority of the work is typically performed at a later time in a softirq and tasklet. This has the advantage of reenabling interrupts and even scaling softirqs or tasklets across multiple CPUs for the majority of the work. However, this has shown how software has been used to redefine legacy scheduling policy.

With speed and efficiency increases in computer technology, computers are doing even more work. However this makes scheduling the work an even more difficult task. This is shown by the ever evolving nature of the Linux scheduler. There has been much improvement recently, lead by Ingo Molnar. Ingo Molnar [10] started by identifying six sources of long latencies in the Linux kernel. He has established patches that have been incorporated into the mainstream kernel to fix problems. The problems Ingo identified include calls to the disk buffer cache, memory page management, /proc file system, VGA subsystem, large processes and the keyboard driver. His

work has been adopted and methods extended through other patches relating to timing and scheduling, such as the UTIME patch, developed at the University of Kansas[63]. UTIME adds higher resolution timers into Linux. This is supplemented by many other projects, such as Rapid Reaction Linux[64], which further improves upon these results through precalculating delays in processing. Ingo Molnar makes a permanent mark on the Linux kernel history with his O(1) scheduler introduced in the 2.6 version of the kernel. This scheduler accomplishes constant time operations through a trade off of memory for speed. This change from v2.4 kernel has increased the schedulers ability to handle a greater number of processes without performance degradation.

Much of this timing improvement has evolved into real time distributions of Linux like KU Real Time Linux (KURT), RTLinux [65] and Timesys Linux [66]. These projects have accomplished progress in speeding up real time[15] performance. To give better control to application developers, an extension known as the Real Time Application Interface(RTAI)[67], was made as a real-time extension to the linux kernel. These new APIs allow real-time applications to run with strict timing constraints. These APIs have been utilized in many real time systems involving motion control [68].

The KURT project has had further expansion into hardware through a hardware scheduler module as seen through a recent thesis[69]. Feasibility of a hardware scheduler with the Linux kernel is shown. Performance is not significantly improved in its design, although a distinct improvement in worst-case scenario time is shown with the hardware scheduler.

Efforts in Linux have continued into new ideas and these continue to evolve projects like HRTimers[70]. HRTimers further develop multiple timer systems that respond to the accuracy needs of different applications. Not all timers are created equal. Some are just timeouts for networking, and device drivers that rarely occur and do not need high resolution. Others are used to schedule more important events, and need more accurate precision. By creating multiple systems with different resolutions, overhead versus accuracy can be balanced.

More recently, the PREEMPT\_RT patch[71] for the Linux Kernel has been the widest used

kernel for Linux real time systems. The PREEMPT\_RT is a combination of many previous ideas of lower latency and preemptable kernel patches[72]. The biggest idea behind the PREEMPT\_RT patch is to minimize the amount of kernel code that is non-preemptable. This results in priority inheritance for many in-kernel spinlocks and semaphores to allow preemption. Many other critical sections are also shortened, deferred or made preemptable. In addition, interrupts become preemptable and can run in process context, allowing scheduling on the same priority level as threads. The PREEMPT\_RT patch is one of the best approximations in comparison to some hardware schedulers. It generally represents a plateau of what is possible in minimizing interrupt jitter[73]. While it does not completely eliminate interrupt jitter because hardware interrupts still cause the CPU to stop, it does the bare minimum to schedule the thread that services the interrupt. After this, it goes back to the highest priority process.

Despite these improvements, the Linux scheduler still adds overhead to the system. This project focuses on moving key aspects of the scheduler into hardware, primarily the run queue and the decision of what should be scheduled next. This improvement allows the CPU time consumed by the operating system scheduler to be reduced and made available to other processes.

#### 2.4 Hardware Schedulers

Hardware scheduling has also been a popular research topic in the areas of real time and embedded systems. With well co-designed hardware cores, the minimum level of jitter and overhead can be significantly reduced [74][75][76]. However, despite this effort, most of the work has not made an impact on mainstream computing. The questions of why and what can be improved must be asked of these projects.

There are many different parts of scheduling to try to improve with hardware. Invocation methods, scheduling algorithms and context switching make up the majority of time when doing scheduling. While most historical hardware schedulers have focused on moving the scheduling

algorithm to hardware, this research takes a different approach in that the focus is on all of the invocation mechanisms. There has been little research into context switching, because it generally needs a major architectural change in processors. Most of the original hardware scheduling units involve complex hardware sorters to compare thread priority. Originally, work is done to minimize sorting size in hardware but to keep the speed in insertion and extraction from the hardware sorting mechanism[77]. A few examples of the first hardware scheduling systems follow.

The Spring Kernel and Scheduling Co-Processor[78] is a project from the University of Massachusetts seeking to enhance real time scheduling. The Spring Kernel is designed for meeting hard real-time deadlines. The process sends scheduling requests to the kernel which can only be accepted for execution if the deadline constraints are possible. From this work, they design a scheduling co-processor showing significant improvements to scheduling. They even recommend incorporation of this scheduling co-processor into general purpose processors, calling it analogous to special purpose hardware for branch prediction[79]. This project starts a base line for future endeavors. As hardware design techniques and technologies improve it gives way to easier and larger hardware schedulers.

Sergio Saez of the Universidad Politecnice de Valencia proposes a circuit solution of a sophisticated interrupt controller used as a scheduler[80]. It combines systolic arrays to achieve constant time decisions. They propose a few advancements to real time deadlines. One advancement is keeping deadline information in the hardware and looking for slack between deadlines. This slack can be used to run lower priority processes with early deadlines. His designs show the advantages and disadvantages of hardware schedulers with lots of process state information. Although deadline information allows better hard real-time performance, the size and complexity trade off makes it unsuitable for general purpose systems.

A group from Mlardalens University has created their ASIC hardware scheduler[81]. It can handle up to 64 tasks at eight priority levels that can be mapped on up to three CPUs. Most of the

communication between the processor and scheduler are done through interrupts and 4-6 bus accesses to registers. It introduces new ideas on multiple CPU systems. However, its register system has issues with atomic operations and extra care has to be given to this design. This project shows how a hardware scheduler can support a tickless kernel. It determines a time model for comparison of real-time systems and explores new hardware accelerated operating system functions like semaphores.

Paul Kohout with the University of Maryland[47] has also designed and simulated a Real time Task Manager (RTM) that takes the most common RTOS operations, like task scheduling, time management and event management. It implements static priority scheduling for up to 64 threads. His design differs from existing approaches, by taking a more minimalistic design. He has a status and a timer register for each priority level. No other information is kept about priority levels. In simulation, he shows results of 80-90% speed up in common scheduling tasks, even though the hardware design is also very small. However, the system is lacking in that it is not designed to accommodate interrupts. Although never actually implemented, this design characterizes a base for this dissertation. The design is being expanded to a larger and more general system while being implemented.

Early implementation of hardware schedulers focuses on a limited scope system that is as fast as possible [75]. It usually includes a limited amount of threads and utilizes a great number of hardware resources to achieve this goal. Generally these implementations require additional hardware resources for each additional thread in the system because of the use of systolic arrays[82]. With significant hardware resources needed, much planning is needed to implement this type of system. This leans away from the idea of a general purpose system. This thesis seeks to minimize hardware resources, only using hardware when there is a specific advantage to it. After these initial designs, complex hardware scheduling designs evolve that begin to involve interrupts and timers. A group from Georgia Tech[83] takes a look at moving the scheduler and the periodic timer tick into hardware with interrupts at eight priority levels. Their scheduler is

flexible and can be configured to three algorithms: Priority, Earliest Deadline First and Rate Monotonic. This is an advantage provided by their hardware platform of FPGAs. The speed development and dynamic programmability of FPGA allow their scheduler to be reprogrammed to the best algorithm. Their synthesis hardware supports up to 16 tasks and eight external interrupt sources. It is fairly extensive hardware and supports queue operations in hardware. This advanced functionality has not been seen in previous generation projects due to lack of hardware resources. This work improves hardware schedulers to a more modern scheduler design with run queues and sleep queues. This group's work shows significant improvement over earlier designs and has set the foundation for future works.

More recently, a project called Hybridthreads[23] takes a more general approach to the problem. The Hybridthreads project originated at the University of Kansas and has recently migrated to the University of Arkansas. The Hybridthreads group created a hardware scheduler and operating system that abstracted the notion of thread. This thread can be either a hardware or software thread and is treated the same through the operating system. Hybridthreads are a unique approach to hardware scheduling as it is geared toward FPGA hybrid hardware software systems. Its hardware design is also unique in it is similar to the O(1) linux schedulers. It has a queue for each priority level and is extremely fast and efficient in scheduling operations. The Hybridthreads system has expanded into semaphores, timers and interrupts to support its hardware scheduler, and extends its new hardware/software neutral threaded computational model.

This thesis is a branch off of the Hybridthreads project at the University of Kansas. One of many projects taking the concepts of Hybridthreads and extending them [84]. The lessons learned from creating a efficient, timely, and predictable hardware operating system in a hybrid environment of hardware and software are being applied towards more general systems. More specifically, Hybridthreads is ported to a mainstream platform, Linux. The knowledge learned from this is used to redesign for software threads, removing the ability to support hardware threads. Although new FPGA computational models are being developed and advancing quickly,

their affect on general computing in the near future will probably be limited, hence, the redesign of a scheduler to focus on software threads. The goal of this dissertation is to show that the inclusion of a lightweight hardware scheduling core into the next generation of processor is merited due to the increase in performance and response of all types of systems.

# Chapter 3

## **Solution**

### 3.1 Problem Statement

Question: How can the knowledge gained from real-time hardware scheduler research be used to improve a general-purpose operating system?

Hypothesis: Unifying scheduling policy by merging the mechanisms of hardware interrupts, timers, and a software scheduler through creation of new hardware will facilitate improvements to scheduling policy in efficiency, timeliness and predictability, while maintaining a full featured general purpose scheduler.

### 3.2 Hybridthreads

Microkernels are changing the design of operating systems, however FPGAs are making it easier to change the hardware software boundary in today's operating systems. FPGAs do this by allowing quick turn-around between hardware design and implementation. The logic fabric of an FPGA can be reprogrammed in seconds, although typically taking a few hours to synthesize the logic gates from hardware description languages. This new hardware testing paradigm has led to

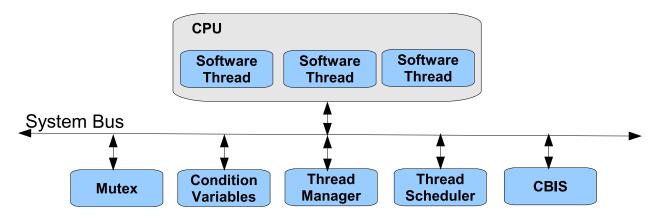

Figure 3.1: Hybridthreads Design

much experimentation in the hardware software boundary for a kernel. The Hybridthreads microkernel from the University of Kansas[85] is a development of this new process. Through experimentation with the hardware software boundary of operating system, the Hybridthreads kernel was developed as an FPGA operating system that maximizes the parallel nature of its specialized hardware circuit to execute common operating system tasks.

Each of these common system tasks are completed in an independent hardware core. The cores independent design allow them to act in parallel. The hardware cores can communicate with each other without processor intervention, enabling a variety of improvements. These improvements include faster and more predictable responses from operating system service to advanced interaction with specialized hardware cores[85]. The Hybridthreads system has improved performance and predictability of the operating system through moving specialized pieces of an operating system into hardware. Utilization of these hardware components to off-load scheduling decisions has been shown to be a practical way to reduce OS jitter[85].

The Hybridthreads system is built with predictability as a design goal. The modules have deterministic execution times and can all act in parallel to each other. They do not depend on the CPU for execution and lack global shared data structures. The Hybridthreads operating system is shown in Figure 3.1 and currently contains dedicated hardware components including:

#### Thread Manager

- Thread Scheduler

- Synchronization Manager

- Condition Variable Manager

With the exception of virtual memory, which typically has its own hardware unit, these cores form a basic microkernel. These dedicated cores are programmed in VHDL. They are implemented as custom finite-state machines, realized in hardware on an FPGA. The Hybridthreads cores communicate over the FPGA's internal bus and work together to form the standard set of Operating System primitives, while being able to act independently of each other.

### 3.2.1 Memory Mapped I/O

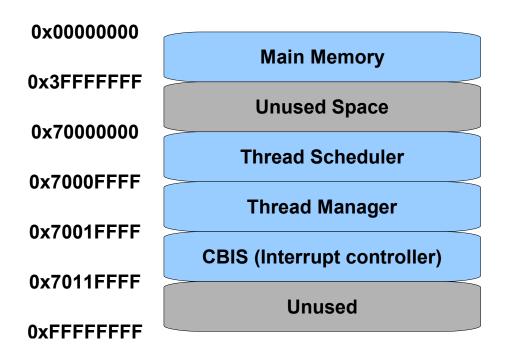

Communication and interaction between Hybridthreads components happen through memory mapped I/O over the system bus. The Hybridthreads system exploits the design of the master memory bus to do the majority of its operations atomically through a load command. System buses are typically designed to be atomic, only allowing a single operation at a time and blocking access until that operation is done. Essentially, Hybridthreads is using the parallel arbitration mechanism of the system bus, rather that establishing a software protocol to accomplish the same idea. Parameters for the call are encoded into the lower bits of the load address, and the return of the load indicate the results of this single atomic operation. This can be seen through a typical memory map, as seen in Figure 3.2

While this operation does have the advantage of being atomic, it limits the amount and size of arguments as a tradeoff for defined memory space. This can be seen in Figure 3.2. The Thread Scheduler has been assigned 65KB of address space, giving it 16 bits of possible arguments. This 16 bits of arguments can be divided among command and arguments. In addition, the CBIS has been assigned 1MB of address space, giving it 20 bits of possible arguments. Considering the practical maximum of a 32 bit system, assigning 2GB or half the address space, gives 31 bits of

Figure 3.2: Address Map

arguments. Giving the thread scheduler, this amount of space would allow us to have 16 commands, 1024 priority levels, and 131072 threads. While this can be a slight constraint in a 32 bit system, 64 bit systems relax most of the design challenges this proposes. The extra address space in a 64 bit system allows larger parameters without monopolizing the address space. Alternatively, this limit can be worked around with store commands, which not only have an address, but a value, thus doubling the amount of data one can send atomically. This extra encoding comes at a cost because store commands do not allow a return value.

Memory mapped interface operating services have an advantage of allowing access from software and hardware services. These hardware services, including operating system components and other devices, can request service without stopping the CPU. This direct hardware to hardware interaction for operating system services can facilitate new and interesting interactions between hardware, including in Heterogeneous computing environments. In the growing embedded System on a Chip market, this could include advanced interaction with

Graphic Processing Units(GPUs)[86], Digital Signal Processors(DSPs)[87] and Modems[88]. The design of Hybridthreads takes full advantage of direct hardware to hardware communications, with scheduling commands flowing from the synchronization, interrupt and timer cores directly to the thread scheduler.

### 3.2.2 Thread Manager

The first core of Hybridthreads is the thread manager. The thread manager is responsible for creating, deleting and maintaining state for the threads in the system. Internally, the thread manager keeps track of state information, including running, suspended, exited or ready-to-run, and parent/child relationship. The thread manager is, also, a liaison to the thread scheduler because many thread management operations result in a scheduling decision. The thread manager has two internal data structures, the thread status array and the thread identifier stack.

The thread identifier stack is a data structure that keeps track of unused thread IDs. It does this through a LIFO (Last In First Out) stack created in a BRAM. When initialized, all the free thread IDs are written into the BRAM in order. The stack pointer is initialized to the final entry. As requests for new threads come in, the stack pointer, stored in a register, is deferenced into the BRAM to grab the top of the stack. This value is returned for the new thread and the stack pointer is decremented to the next BRAM value. As threads are deleted, the stack pointer is incremented and the deleted thread ID is placed in the BRAM at the new stack pointer address for reuse.

The Thread Status Array, as seen in Table 3.1, is responsible for storing all the parameters and run time status of a specific thread. It is implemented in a BRAM, with the thread ID as the index. This includes thread ID, parent/child information, joinability, and exit status. Commands to change and look up these data are simple reads and writes from the BRAM with the thread ID as the index. This information is shared with the thread scheduler through the BRAM second access port. This allows the thread scheduler to check on thread validity without contacting the thread manager.

Table 3.1: Thread Status and Identifier BRAM Layout

| Field                 | Width  | Bits  |

|-----------------------|--------|-------|

| Stack Thread ID Entry | 8 bits | 0-7   |

| Unused                | 8 bits | 8-15  |

| ParentID              | 8 bits | 16-23 |

| Detached              | 1 bit  | 24    |

| Joined                | 1 bit  | 25    |

| Used                  | 1 bit  | 26    |

| Exited                | 1 bit  | 27    |

| Unused                | 4 bits | 28-31 |

To save space and be more efficient in the FPGA implementation, the Thread Status and Thread Identifier array share the same BRAM, as seen in Table 3.1. Xilinx Virtex 2 Pro has a 32-bit wide BRAM, natively. Since the arrays require 8 and 12 bits respectively, they can be compressed into one BRAM. Conceptually, they are treated separate, but in the implementation are shared. This does limit simultaneous access to the BRAM, but normal operations can serialize their access.

Internally, a finite state machine responds to commands and compiles information into these two data structures that are shared with the thread scheduler. For example, a Create call will cause the Thread Manager to communicate that the thread needs to be enqueued with the scheduler. These states form all the basic commands to create, delete and change status on threads. There are, also, control signals that go between the thread manager and the thread scheduler, as shown in Figure 3.3. These signals tell the scheduler when to update its status. A list of the thread manager operations is in Table 3.2

### 3.2.3 Hardware Thread Interface (HWTI)

The Hybridthreads Thread Manager supports an abstract notion of a threads. The Threads Manager implements a pthread interface to support software threads. In addition, it can support

Figure 3.3: Block Diagram of Thread Manager and Scheduler

hardware threads. The concept of hardware threads is a bit different because hardware threads are on uninterruptible and dedicated hardware computational units. The Thread Manager and the other cores allow these hardware threads to interact with operating system primitive through the Hardware Thread Interface (HWTI) core. This is a hardware core that abstracts access to thread and synchronization operations. Allowing access to the same primitives, such as mutexes, through a similar interface helps in porting algorithms from hardware to software. Increasingly, complex interactions of specialized hardware units with the operating system are allowed with operating system primitives accessible without interrupts.

Table 3.2: Thread Manager Commands

| Command   | Description                                                  |

|-----------|--------------------------------------------------------------|

| Create    | Create new thread and Reserve a new TID                      |

| Current   | Returns the current thread running                           |

| Next      | Gets the next thread to be run and sets it to current thread |

| Clear     | Deletes and thread and recycles TID                          |

| Is_Queued | Query if thread is in ready to run queue                     |

| Yield     | Yield Current thread to other threads of same priority       |

| Exit      | Ends thread and notifies parent of exit status               |

| Join      | Blocks parent thread until child exits                       |

| Detach    | Changes from joinable to detached thread                     |

#### 3.2.4 Thread Scheduler

Originally, the Hybridthreads system uses a simple FIFO scheduler built into the Thread Manager[89]. However this poses a problem in which the storage for thread management and scheduling operations are in the same state machine and these operations cannot happen in parallel. To accommodate for more complex schedulers, the Hybridthreads teams decide to separate the scheduling mechanism into a coprocessor. This thread scheduler can act independently, but is often controlled by the thread manager through a special interface as to not monopolize the system bus. This, also, allows a convenient interface for multiple scheduling algorithms, since the scheduling algorithm is in a separate core. The growth of partially reconfigurable FPGAs[90][91][92] allows changing the algorithm at run-time.

The second core in the Hybridthreads system is the thread scheduler. The thread scheduler works in combination with the thread manager to control which thread is running on the CPU. It is internally organized like the O(1) scheduler of Linux. It keeps track of a doubly linked list for each priority level and uses a high speed priority encoder to determine the highest outstanding priority in the system. It shares information with the thread manager through a few signals and a shared BRAM. In addition, it has two additional data structures, a priority BRAM and another thread scheduling parameter BRAM.

Table 3.3: Thread Manager and Thread Scheduler Shared Signals

| Signal                | Width   |

|-----------------------|---------|

| Next_CPU_Thread_ID    | 8 bits  |

| Current_CPU_Thread_ID | 8 bits  |

| Command               | 12 bits |

Table 3.4: Thread Scheduling Parameter BRAM

| Field                               | Width  | Bits  |

|-------------------------------------|--------|-------|

| Queued                              | 1 bit  | 0     |

| Priority Level                      | 8 bits | 1-8   |

| Ready to Run Queue Next Pointer     | 8 bits | 9-16  |

| Ready to Run Queue Previous Pointer | 8 bits | 17-24 |

| Unused                              | 7 bits | 25-31 |

The shared signals are Next\_CPU\_Thread\_ID, Current\_CPU\_Thread\_ID and Command.

Next\_CPU\_Thread\_ID is a signal from the thread scheduler to the thread manager, indicating the next highest priority thread to be run. Current\_CPU\_Thread\_ID is a signal from the thread manager to the thread scheduler, indicating the currently running thread. These two signals are constantly monitored to determine the Next Thread, of higher priority than the current thread.

When this happens, a traditional interrupt is sent to the CPU to kick off changing threads. The Command signal includes both an action, Enqueue\_Request or Dequeue\_Request and a datum value, a thread ID. These commands are done when the a thread manager operation needs to enqueue or dequeue a thread, such as a delete thread call would dequeue a thread. This command signal will kick off the appropriate thread scheduler logic to respond to the command.

The Priority BRAM, seen in table 3.5, is used to keep track of the data of the threads at each priority level. It does this through a doubly linked list of each priority. The data structure is indexed by priority level. The entry for each priority level contains a head and tail pointer to the list of threads currently queued at that priority level.

Table 3.5: Priority BRAM

| Field                       | Width   | Bits  |

|-----------------------------|---------|-------|

| Priority Queue Head Pointer | 8 bits  | 0-7   |

| Priority Queue Tail Pointer | 8 bits  | 8-15  |

| Unused                      | 16 bits | 16-31 |

These head and tail pointers point into the Thread Scheduling Parameter BRAM, seen in Table 3.4, which is indexed by thread ID. The entries in this BRAM are priority, parameters, previous thread, and next thread, creating a doubly linked list of all threads in a priority level. Most operations are fairly quick given this doubly linked list. To add a thread to the queue, simply deference the priority of the thread into the priority BRAM to find the tail pointer of the priority list. With that tail pointer, index into the thread scheduling parameter BRAM and change the next pointer in that entry to the newly added thread. Change the tail pointer to the thread being added in the priority BRAM to complete the operation. More complex operations like dequeue, require walking the list to find the entry and removing it. This is still fairly fast, given that the list is in local BRAM memory.

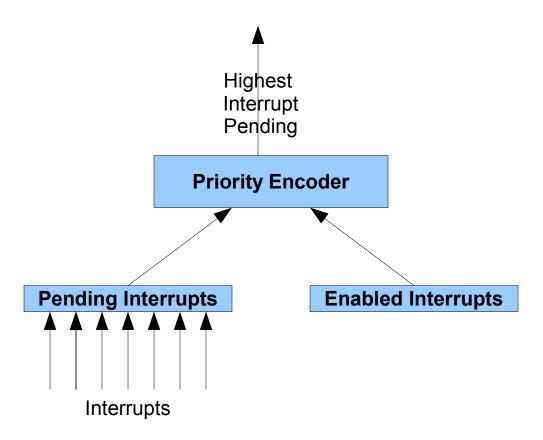

A 256 bit register keeps track of the priorities with enqueued threads. The priority register is updated on each thread operation to reflect the current state of the doubly linked priority list. If a priority level has no threads in the list because no threads are ready to run, the corresponding bit in this register will be 0. If the priority level has threads ready to be run, the corresponding bit in the register will be 1.

A high speed encoder takes this 256 bit register and determines the highest bit set to 1. It outputs the number of this highest bit as an integer representing the index of the highest priority in the queue. This highest priority level is compared to the priority level of the current running thread. If priority indicates a switch in running process, the thread scheduler will directly interrupt the CPU and switch to the new thread. In parallel, it will fetch the Thread ID of the pending processes from the priority BRAM head pointer for that priority level. The high speed

Table 3.6: Thread Scheduler Commands

| Command           | Description                               |

|-------------------|-------------------------------------------|

| Enqueue           | Add thread to ready to run queue          |

| Dequeue           | Remove thread from the ready to run queue |

| Get_Entry         | Return a threads attributes               |

| Toggle_Preemption | Allow the scheduler to preempt the CPU    |

| Get_Priority      | Sets a thread's priority                  |

| Set_Priority      | Sets a thread's priority                  |

| Is_Queued         | Test if thread is Queued                  |

| Is_Empty          | Status Bit to see if threads are queued   |

| Set_SchedParam    | Return Scheduling Parameter Entry         |

| Set_Idle_Thread   | Set Idle Thread ID                        |

| Get_Idle_Thread   | Set Idle Thread ID                        |

priority encoder is able to calculate the highest priority level very fast in 5 clock cycles. This allows for extremely fast and jitter free scheduling decisions.

The biggest advantage of this scheduler is that preemption only happens when a thread change is in-progress. Scheduling operations do not speculatively have to include a check for preemption with calls to the core schedule function. The preemption check is always done in parallel. The thread scheduler allows many standard thread management calls to enqueue, dequeue and set priority over the memory bus, allowing both hardware and software to do scheduling operations. The operations of the thread scheduler are listed in Table 3.6

#### 3.2.5 Linux Software Modifications

To get the Thread Scheduler and Thread Manager ported into Linux, many adjustments had to be made to the Linux kernel. This includes modifications to both the Linux Scheduling function, as seen in Table 3.7, and to the internal Linux structures

Table 3.7: Modified Scheduler Functions

| Command                    | Description                                       |

|----------------------------|---------------------------------------------------|

| sched_init                 | Initialization of Scheduler                       |

| enqueue_task               | Add a task into scheduling queue                  |

| dequeue_task               | Remove a task from scheduling queue               |

| requeue_task               | Move a task to the back of its priority queue     |