# Framework of Real-Time Optical Nyquist-WDM Receiver using Matlab & Simulink

By

# Adam Vincenzo Crifasi

Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Master of Science.

| Chairperson Dr. Rongqing Hui |

|------------------------------|

|                              |

|                              |

| Dr. Shannon Blunt            |

|                              |

|                              |

| Dr. Erik Perrins             |

Date Defended: June 3, 2013

# The Thesis Committee for Adam Crifasi certifies that this is the approved version of the following thesis: Framework of Real-Time Optical Nyquist-WDM Receiver using Matlab & Simulink

Chairperson Dr. Rongqing Hui

Date approved: June 3, 2013

I investigate an optical Nyquist-WDM Bit Error Rate (BER) detection system. A transmitter and receiver system is simulated, using Matlab and Simulink, to form a working algorithm and to study the effects of the different processes of the data chain. The inherent lack of phase information in the N-WDM scheme presents unique challenges and requires a precise phase recovery system to accurately decode a message. Furthermore, resource constraints are applied by a cost-effective Field Programmable Gate Array (FPGA). To compensate for the speed, gate, and memory constraints of a budget FPGA, several techniques are employed to design the best possible receiver. I study the resource intensive operations and vary their resource utilization to discover the effect on the BER. To conclude, a full VHDL design is delineated, including peripheral initialization, input data sorting and storage, timing synchronization, state machine and control signal implementation, N-WDM demodulation, phase recovery, QAM decoding, and BER calculation.

# In loving memory of Kyle

Thank you Lindsey, Mom, and Dad for all the love and support

Thank you Sydney for your encouragement

| Table | of Contents                                                             |     |

|-------|-------------------------------------------------------------------------|-----|

|       | Introduction                                                            | . 9 |

|       | Fiber Optic Communications                                              | . 9 |

|       | FPGAs in Communications Systems                                         | 10  |

|       | Background                                                              | 12  |

|       | General Properties of Fiber Optic Communications                        | 12  |

|       | Optical System using Coherent Detection                                 | 12  |

|       | Coherent Detection with Phase Diversity                                 |     |

|       | Digital-Subcarrier Multiplexing (DSCM)                                  |     |

|       | General Communications and Applicable Digital Signal Processing         |     |

|       | Anti-Alias Filter                                                       |     |

|       | Digital Filtering                                                       |     |

|       | Viterbi-Viterbi Algorithm                                               |     |

|       | Symbol Recovery                                                         |     |

|       | Data Start Sequence                                                     |     |

|       | Preliminary Simulation, Simulink, and Post-Processing                   |     |

|       | Matlab Simulink Components                                              |     |

|       | Normalizer                                                              |     |

|       | IO filter                                                               |     |

|       | ~=                                                                      |     |

|       | Phase_Recovery                                                          |     |

|       | QAM_PLL                                                                 |     |

|       | QAMDemod                                                                |     |

|       | Ninety Degree Shift                                                     |     |

|       | Barker Checker & Data Checker                                           |     |

|       | Simulation Execution                                                    |     |

|       | ReceiverSimulink.m                                                      |     |

|       | Data and Clock Timing                                                   |     |

|       | TX_Func.m                                                               |     |

|       | DataIn1_maker.m                                                         |     |

|       | chebysfilter.m                                                          |     |

|       | Simulink Simulation Results                                             |     |

|       | Post-Processing of Data from a Real Fiber-Optic System                  | 8   |

|       | Post-Processing Results                                                 | 9(  |

|       | Hardware Implementation Perspective                                     | 95  |

|       | ADC12D1600RB                                                            | 95  |

|       | ADC12D1600                                                              | 9"  |

|       | Xilinx Virtex-4 (XC4VLX25)                                              |     |

|       | PLL (LMX2531 LQ1570E)                                                   |     |

|       | BLP-550+                                                                |     |

|       | Hardware Implementation                                                 |     |

|       | VHDL-only Components                                                    |     |

|       | dclk dcm.vhd                                                            |     |

|       | clk100_dcm.vhd                                                          |     |

|       | genericcounter.vhd                                                      |     |

|       | PLL init.vhd                                                            |     |

|       | adcDATAinterface.vhd                                                    |     |

|       | ReceiverFinal.vhd                                                       |     |

|       | TopLevelDesign.vhd                                                      |     |

|       | -                                                                       |     |

|       | Hardware Results                                                        |     |

|       | Future Work and Possible Improvements                                   |     |

|       | Appendix                                                                |     |

|       | A. Digital PLL with Proportional plus Integrator loop filter derivation |     |

|       | B. Bilinear Transformation                                              |     |

|       | C. ReceiverSimulink.m                                                   |     |

|       | D. ReceiverPP.mat                                                       |     |

|       | E. BER Data                                                             | 14( |

| _      | 1 - Comparison of External Lightwave Modulators (Kikuchi K. , 2010) 12               |  |

|--------|--------------------------------------------------------------------------------------|--|

|        | 2 - Spectrum (left) and time pulse (right) for N-WDM (Gabriella Bosco, 2010) 18      |  |

|        | 3 - Spectrum (left) and time pulse (right) for OFDM (Gabriella Bosco, 2010) . 18     |  |

|        | 4 - Nyquist filter transfer function and spectrum at the output (Gabriella           |  |

|        | 2010)                                                                                |  |

|        | 5 - Multiplexed N-WDM (Gabriella Bosco, 2010)                                        |  |

|        | 6 - Analog Anti-Alias Filter Example                                                 |  |

| _      | 7 - Interpolation Filter Example (8x) - Blue: Magnitude Response - Green: Phase      |  |

|        | se 24                                                                                |  |

| Figure | 8 - Random Phase Shift Example - Blue symbol sent - Green symbol received $\dots$ 27 |  |

|        | 9 - Symbol Timing Example (Rice, 2009)                                               |  |

|        | 10 - Eye Diagram Derivatives (Rice, 2009)                                            |  |

|        | 11 - Symbol Recovery Block Diagram (Rice, 2009)                                      |  |

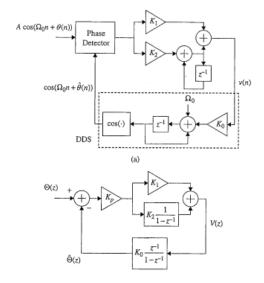

| Figure | 12 - Linearized Frequency Domain Phase Equivalent PLL (Rice, 2009) 32                |  |

| Figure | 13 - (above) discrete time PLL and DDS; (below) linearized phase equivalent . 33     |  |

| Figure | 14- Phase detector gain for raised cosine pulse                                      |  |

| Figure | 15 - Random signal + length 13 Barker code correlated with length 13 Barker          |  |

| code   |                                                                                      |  |

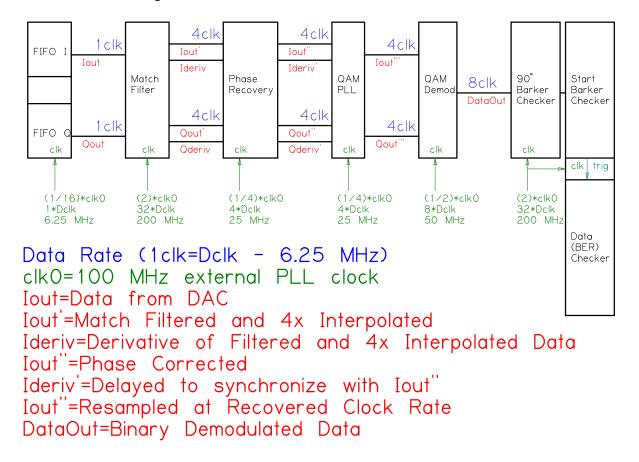

| Figure | 16 - Simulink Receiver System Configuration                                          |  |

| Figure | 17 - Normalizer Simulink Model                                                       |  |

|        | 18 - IQ_Filter Simulink Model 41                                                     |  |

|        | 19 - Interpolated Match Filter Responses vs Channel Spacing                          |  |

| Figure | 20 - Derivative Filter Frequency Response                                            |  |

|        | 21 - Phase Recovery Simulink Model                                                   |  |

| _      | 22 - "(a + jb)^4" Simulink Subsystem 47                                              |  |

|        | 23 - Summing Simulink Subsystems                                                     |  |

|        | 24 - QAM_PLL Simulink Model 50                                                       |  |

|        | 25 - Sign Alter Simulink Subsystem 50                                                |  |

|        | 26 - Modulo -1 Simulink Subsystem                                                    |  |

|        | 27 - QAM Demod Simulink Model                                                        |  |

|        | 28 - Transmit QAM Constellation                                                      |  |

|        | 29 - Ninety Degree Shift Simulink Model                                              |  |

|        | 30- Constellation Correction Subsystem                                               |  |

|        | 31 - QAM Constellation Correction                                                    |  |

|        | 32 - Barker Checker and Data Checker Simulink Model                                  |  |

|        | 33 - Error Counter Subsystem                                                         |  |

|        | 34 - Integration of Simulink Models into a Matlab Simulation                         |  |

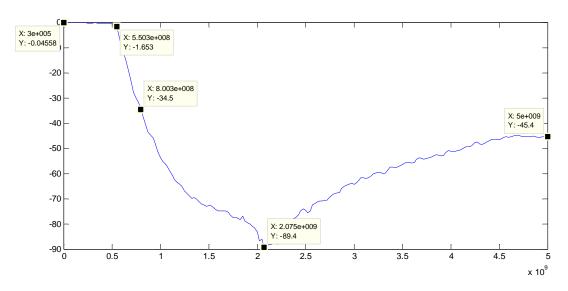

|        | 35 - Measured Analog Anti-Aliasing Filter Response                                   |  |

|        | 36 - Data and Clock Timing                                                           |  |

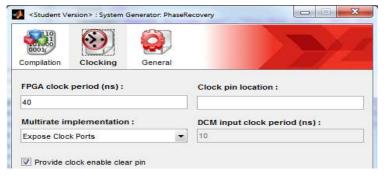

|        | 37 - Simulink Clock Configuration                                                    |  |

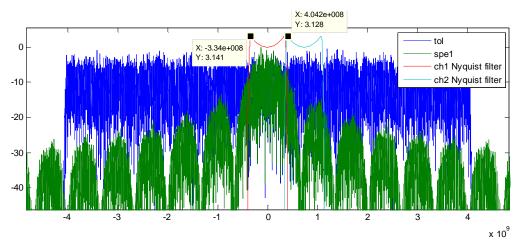

|        | 38 - Baseband Subchannel Input, Nyquist filter, and Transmitter Output Spectra       |  |

|        |                                                                                      |  |

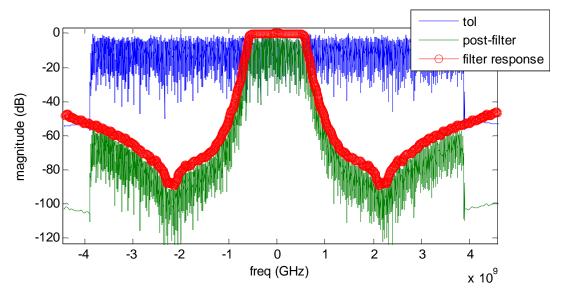

|        | 39 - Anti-Aliasing Filter Demonstration                                              |  |

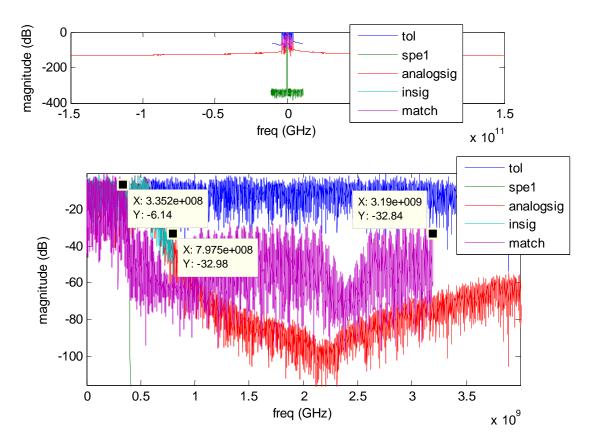

|        | 40 - Simulink Simulation Spectra Comparison (above: full; below: zoomed in) . 77     |  |

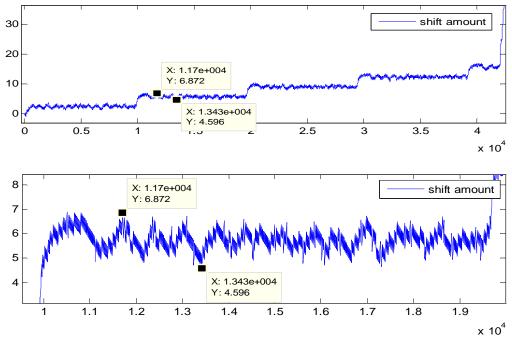

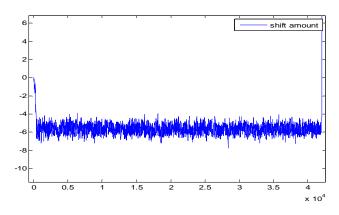

|        | 41 - QAM PLL Shift                                                                   |  |

|        |                                                                                      |  |

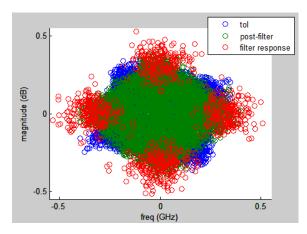

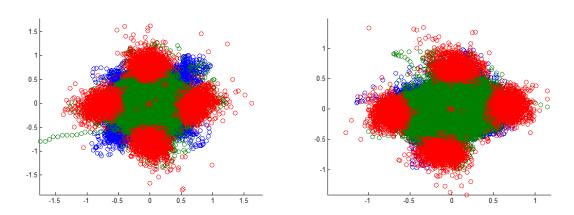

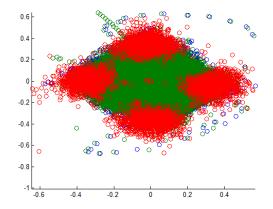

|        | 42 - Scatter Plot Comparison                                                         |  |

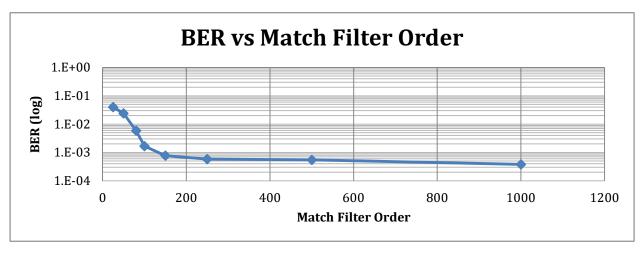

| _      | 43 - BER vs Match Filter Order (N)                                                   |  |

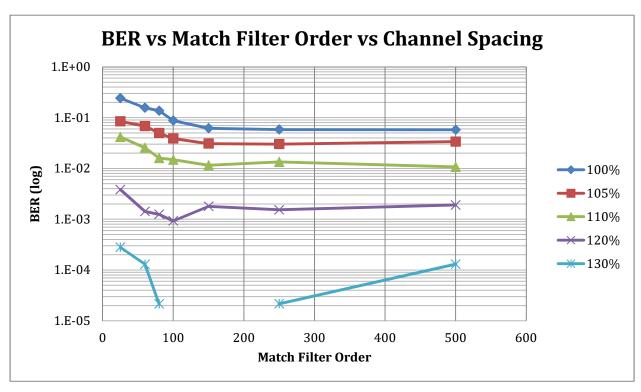

|        | 44 - BER vs N vs Channel Spacing                                                     |  |

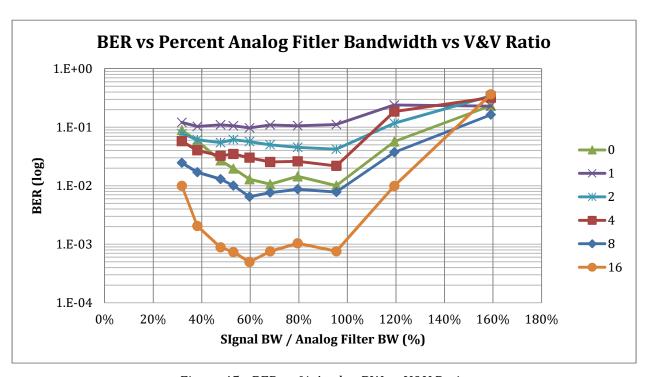

|        | 45 - BER vs % Analog BW vs V&V Ratio                                                 |  |

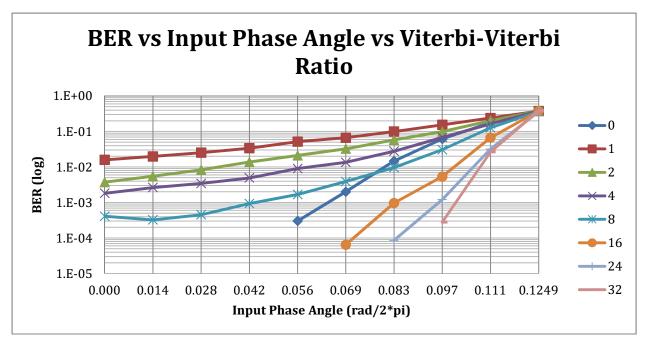

|        | 46 - BER vs Input Phase Angle vs V&V Ratio                                           |  |

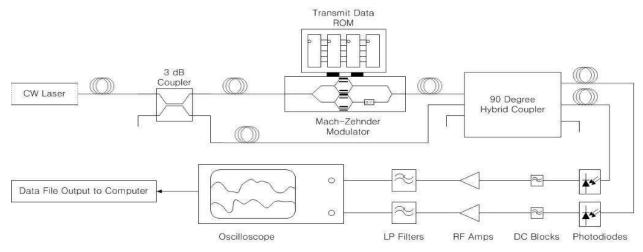

|        | 47 - Test Setup                                                                      |  |

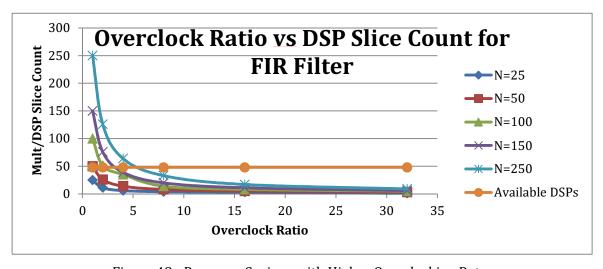

|        | 48 - Resource Savings with Higher Overclocking Rates                                 |  |

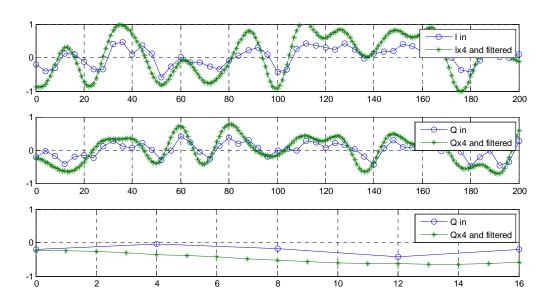

|        | 49 - Input & Filtered Data vs Time                                                   |  |

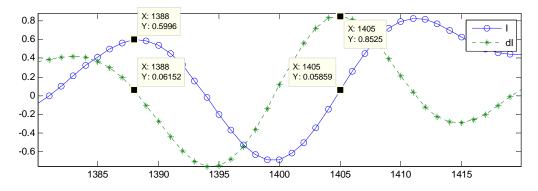

|        | 50 - Filtered and Differentiated Signals vs Time                                     |  |

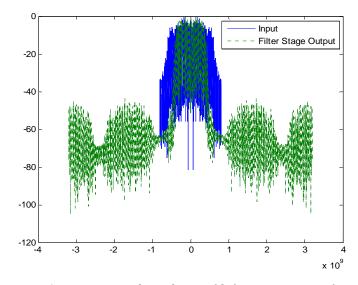

|        | 51 - Input & Filtered Data (dB) vs Frequency (GHz) 91                                |  |

|        | 52 - QAM PLL Shift Amount                                                            |  |

|        | 53 - V&V and QAM PLL Constellations vs Input Data (125% Channel Spacing) 93          |  |

|        | 54 - V&V and QAM PLL Constellations vs Input Data (115% Channel Spacing) 93          |  |

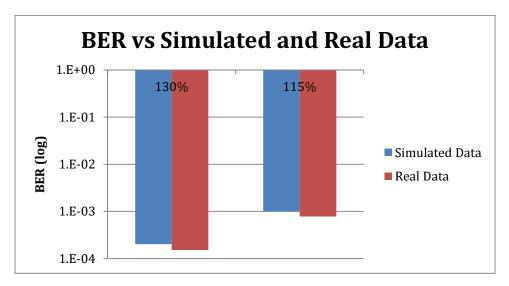

| Figure | 55 - Comparison of Real and Simulated Data 94                                        |  |

|        |                                                                                      |  |

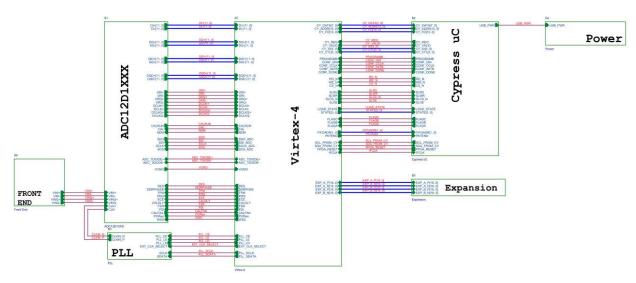

| Figure | 56 | - | ADC12D1600RB Top Level Design                     | 95  |

|--------|----|---|---------------------------------------------------|-----|

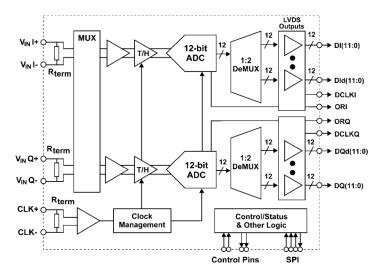

| Figure | 57 | _ | ADC12D1600 Functional Block Diagram               | 97  |

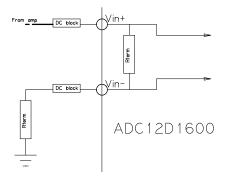

| Figure | 58 | _ | Single Channel Analog Input Configuration         | 98  |

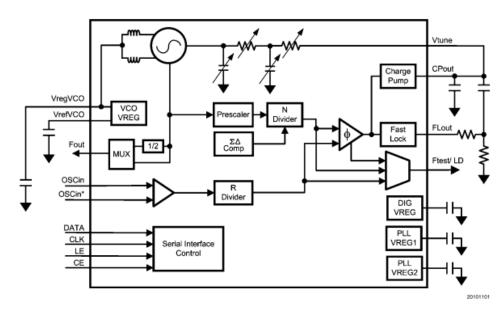

| Figure | 59 | _ | LMX2351LQ1570E Functional Block Diagram           | 100 |

| Figure | 60 | _ | Top Level Block Diagram                           | 104 |

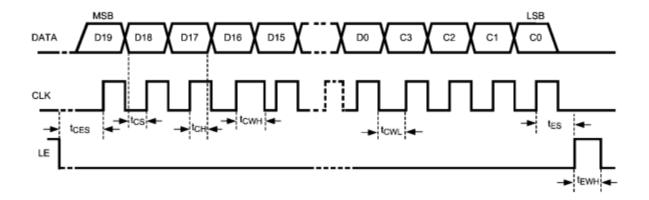

| Figure | 61 | _ | Serial Interface Diagram                          | 10  |

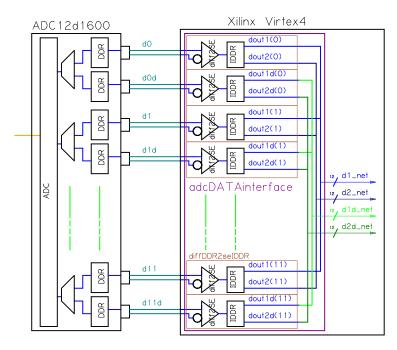

| Figure | 62 | _ | Single Channel adcDATAinterface.vhd Block Diagram | 10  |

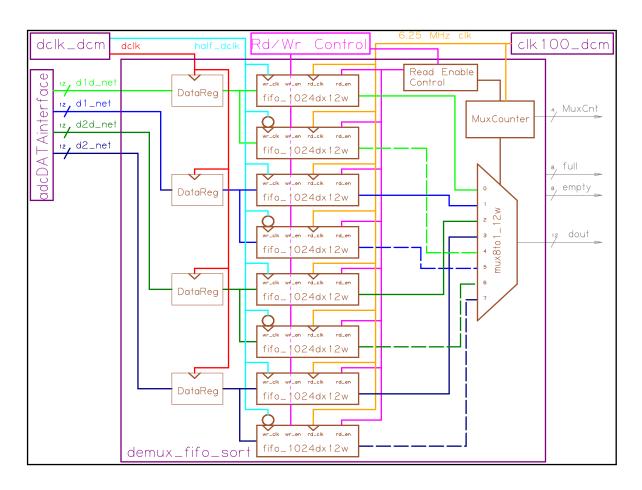

| Figure | 63 | _ | Single Channel demux_fifo_sort.vhd Block Diagram  | 108 |

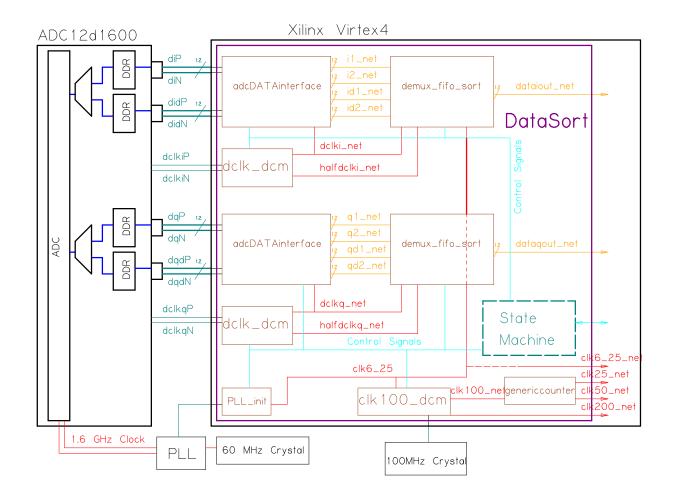

| Figure | 64 | _ | Dual Channel DataSort.vhd Block Diagram           | 111 |

| Figure | 65 | _ | DataSort.vhd State Machine                        | 113 |

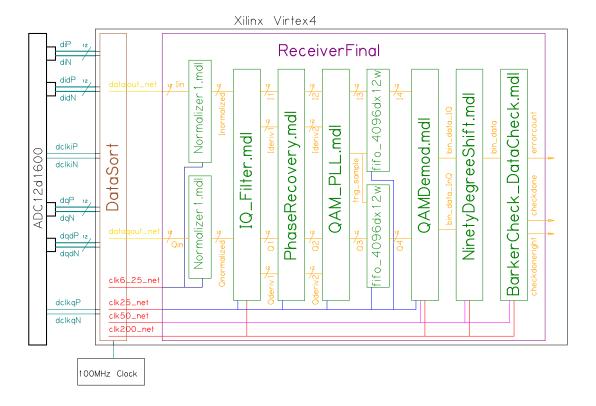

| Figure | 66 | _ | ReceiverFinal.vhd Block Diagram                   | 11  |

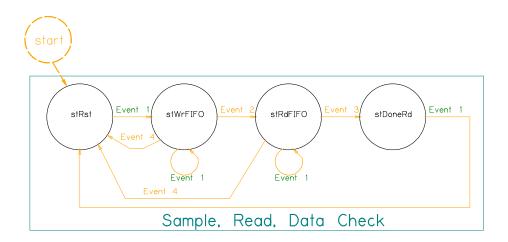

| Figure | 67 | _ | ReceiverFinal.vhd State Machine                   | 119 |

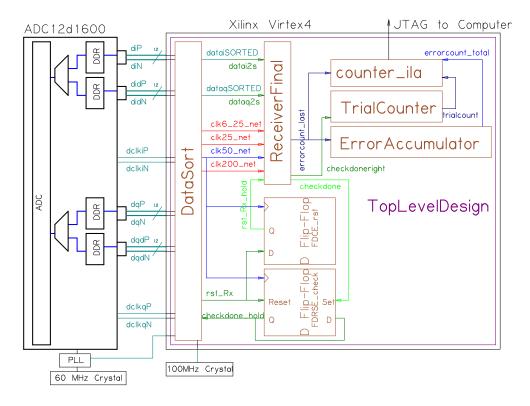

| Figure | 68 | - | TopLevelDesign.vhd Block Diagram                  | 122 |

|        |    |   |                                                   |     |

| Table | 1 - | Interpolated Match Filter Specifications vs Channel Spacing | 43  |

|-------|-----|-------------------------------------------------------------|-----|

| Table | 2 - | Length 11 Barker Code                                       | 56  |

| Table | 3 - | Barker code and Filter Coefficient Comparison               | 56  |

| Table | 4 - | Phase Shift MUX's Alterations                               | 58  |

| Table | 5 - | Triggers vs MUX Selections                                  | 58  |

| Table | 6 - | Length 13 Barker Code                                       | 6(  |

| Table | 7 - | Key Specifications of the ADC12D1600                        | 98  |

| Table | 8 - | Virtex 4 LX Model Comparison                                | 9 9 |

| Table | 9 – | Key Specifications of the BLP-550+ 1                        | 02  |

| Table | 10  | - Data Sort Order 1                                         | 1(  |

| Table | 11  | - DataSort.vhd State Machine Events 1                       | 13  |

| Table | 12  | - DataSort.vhd Control Signals 1                            | 15  |

| Table | 13  | - ReceiverFinal.vhd Block Diagram 1                         | 19  |

| Table | 14  | - ReceiverFinal.vhd Control Signals 1 1                     | 20  |

| Table | 15  | - ReceiverFinal.vhd Control Signals 2 1                     | 20  |

| Table | 16  | - FDRSE_reset Logic Sequence                                | 23  |

### Introduction

# Fiber Optic Communications

The world of networking relies on a mixture of wireless, copper, and fiber optics communication media to transfer data from anywhere to everywhere. No one medium can conquer the whole task and each provides advantages and disadvantages. Wireless links provide a means to communicate without the physical infrastructure needed with copper or fiber, but are restricted by the structured frequency bands and suffer from extra signal degradation. Copper provides a direct electrical link with ease of transmission and receiving, but has mediocre relative bandwidth capabilities and suffers from electromagnetic interference. Fiber optics boast the most advantageous potential of them all, but also has its faults.

Fiber optics are a necessity in this modern world of communications. Their extreme bandwidth capabilities and electrical isolation represent their most important features.

Telecom providers continue to push the data rate envelope to reduce the number of fibers needed, utilize modern networking equipment, and deliver their users the bandwidth they crave. Power utilities, among others, enjoy the safety of a communication link that does not carry fault current.

The process of creating and demodulating a light signal is similar, yet unique, when using a light source. The complex modulation schemes require expensive equipment and precise considerations. Variances in the forces laying on a fiber, for example, can alter the lightwave within the fiber. Chromatic and modal dispersion inherently smear the signal

inside the core. But companies around the world will continue to utilize fiber above the other options due to the bandwidth available.

# **FPGAs in Communications Systems**

The efficiency of communication systems has rapidly improved over the years, but with the price of increased system more complexity. More data can be packed into smaller bandwidth by clever signal processing. Higher order systems need precision equipment to sample and decode these signals. Technology is continuously striving to chase the requirements of the internet, cell phone usage, and other data demand.

Networking hardware has to process a lot of data while minimizing latency. This requires many repetitive and parallel processes. All computers can accomplish repetitive tasks; that's what they were made for. But many computer architectures are not suited for parallel tasks. For instance, microcontrollers (MCUs) can execute multiplication functions in milliseconds, but can only process one operation at a time. Two multiplication operations take approximately twice as long as one multiplication. This is where FPGAs excel.

Commercial communication equipment usually employ application-specific integrated circuit (ASIC) for high reliability, low power consumption and miniature footprints. However, the cost of ASIC development is high and the design process is long, and therefore it is usually not used for prototyping. In comparison, a Field Programmable Gate Array (FPGA) offers increased flexibility, as its a chip containing massive amounts of gates which can be arranged in any fashion. Along with the embedded hardware are

hundreds of pins which can be programmed as inputs or outputs. Whereas all operations have to process through a common core in a MCU, the logic on an FPGA can take any form, be completely independent of one another, and even belong to different clock domains.

Modern FPGAs contain more than programmable AND and OR gates, built in modules help ease the amount of programming and generate a better product. Most FPGAs, for instance, have clock controllers to ensure the sequential logic performs as expected.

Digital signal processing (DSP) almost always consists of repetitive tasks. Many times, there are separate channels which require the exact same processing. The FPGA hardware and programming architecture thrive at parallel processing, and thus parallel pipelines can execute the required process on several channels at once, depending on gate availability. Each parallel process can be seen as a multiplier to the system's clock speed. The FPGA's ability to run at already high clock speeds coupled with the parallel multiplier means the chip can provide a developer with the right tool to create the fastest, most robust systems.

# Background

### **General Properties of Fiber Optic Communications**

### **Optical System using Coherent Detection**

To convert an electrical signal into the optical domain and send into fiber optic systems, the laser itself can be modulated directly or an external modulator can act upon the launched light. Only amplitude modulation (AM) can come of modulating the laser itself. An external modulator can modulate a light signal a number of ways: AM, phase modulation (PM), or more complex modulation schemes (Kikuchi K., 2010).

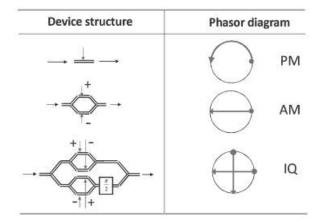

Figure 1 - Comparison of External Lightwave Modulators (Kikuchi K., 2010)

An external modulator with a Mach-Zehnder configuration, driven in push-pull mode, can perform AM of a light source. By placing two Mach-Zehnder push-pull modulators in parallel with a 90 degree phase shift between the arms, a complex IQ signal is generated (S. Shimotsu, 2001). The in-phase and quadrature signals now exist independently of each other. With no higher order modulation, the signal information is

doubled within the same bandwidth. Any kind of higher order modulation is possible with this complex modulation setup, just as it is in RF or wireless communications (eg, 16 QAM).

An optical receiver system performing coherent detection in the correct configuration can demodulate a complex signal. The signal must be downshifted from the transmitter carrier frequency. This is done, fundamentally, by taking the product of the electric fields of the signal and the local oscillator. The local oscillator (LO) is a continuous wavelength (CW) light source. Define the modulated optical signal and the local oscillator as:

$$\vec{E}_s(t) = \vec{A}_s(t)e^{j\omega_s t + j\phi_s(t)}$$

Equation 1

$$\vec{E}_{LO}(t) = \vec{A}_{LO} e^{j\omega_{LO}t + j\phi_{LO}}$$

Equation 2

where  $A_S$  and  $A_{LO}$  are the complex amplitudes, and  $\omega_S$  and  $\omega_{LO}$  are the angular frequencies. Note that the complex amplitude of the LO is constant, whereas the signal's complex amplitude changing with time (Kikuchi K. , 2010). Both the amplitude and the angle of the signal vary with time.

The two outputs of a 2x2 optical coupler mixing the source and local oscillator light waves is given by the following transfer function:

$$\begin{bmatrix} \vec{E}_1 \\ \vec{E}_2 \end{bmatrix} = \begin{bmatrix} \sqrt{1 - \varepsilon} & j\sqrt{\varepsilon} \\ j\sqrt{\varepsilon} & \sqrt{1 - \varepsilon} \end{bmatrix} \begin{bmatrix} \vec{E}_s(t) \\ \vec{E}_{LO} \end{bmatrix}$$

Equation 3

The square roots describe an energy mixing equation and  $\epsilon$  is the power-coupling coefficient (Hui & O'Sullivan, 2009). In a simple setup, one output is terminated and the signal contained in the other fiber is

$$\vec{E}_1(t) = \sqrt{1 - \varepsilon} \vec{E}_s(t) + j\sqrt{\varepsilon} \vec{E}_{LO}$$

Equation 4

A photodiode placed at the end of the output produces the current

$$i(t) = R \left| \vec{E}_1(t) \right|^2$$

Equation 5

=  $R \left\{ (1 - \varepsilon) \left| \vec{A}_s(t) \right|^2 + \varepsilon \left| \vec{A}_{LO} \right|^2 + 2\sqrt{\varepsilon(1 - \varepsilon)} \vec{A}_s(t) \cdot \vec{A}_{LO} \cos(\omega_{IF} t + \Delta \emptyset(t)) \right\}$

where  $\omega_{\text{IF}} = \omega_{\text{s}}$ -  $\omega_{\text{LO}}$ ,  $\Delta \emptyset(t) = \emptyset_s(t) - \emptyset_{LO}$ , and R is the responsivity of the photodiode (Hui & O'Sullivan, 2009). The term  $\omega_{\text{IF}}$ , or intermediate frequency, is the difference between the two light source's frequencies and  $\Delta \emptyset(t)$  is the time dependent relative phase of the two light waves. Another term, the sum of the two light sources, exists but is ignored due to the fact that the RF circuitry will not couple this signal.

To reduce this equation to a compact form, a few assumptions shall be made. Firstly, the LO is a continuous light source with little to no intensity noise, leaving  $\vec{A}_{LO} = \sqrt{P_{LO}}$ , a constant. A DC block after the photo diode will remove this component of the output current. The LO light source is assumed to have a much larger amplitude than the incoming signal. Therefore, the  $|\vec{A}_S(t)|^2$  can also be ignored as  $|\vec{A}_S(t)|^2 \ll \vec{A}_S(t) \cdot \vec{A}_{LO}$  (Hui & O'Sullivan, 2009). A 3dB coupler should be used in the coherent receiver since the maximum power output is achieved when  $\varepsilon=1/2$  (Hui & O'Sullivan, 2009). These assumptions produce a simplified coherent detection photocurrent of

$$i(t) \approx R\sqrt{P_S(t) \cdot P_{LO}}\cos(\omega_{IF}t + \Delta\emptyset)$$

Equation 6

When the LO and signal center frequencies are equal, the system is said to be in homodyne configuration. Therefore, since  $\omega_{IF} = \omega_{s} - \omega_{LO} = 0$ , the equation further reduces to

$$i(t) \approx R\vec{A}_s(t) \cdot \vec{A}_{LO}\cos(\Delta \emptyset)$$

Equation 7

Set up in a homodyne detection scheme, the desired electrical signal from the photodiode exists in baseband, ready to be demodulated by an external system. The

incoming light signal is often very weak. As expressed in Equation 7, the resulting photocurrent benefits from a strong LO to amplify the electrical signal. The relative phase of the LO and the incoming signal will shift, causing the  $\Delta\emptyset$  term to be time dependent. Demodulation techniques further down the signal chain must compensate for this fluctuation.

### **Coherent Detection with Phase Diversity**

A coherent receiver in certain arrangements can detect the complex amplitude information from a modulated signal. The setup and theory is very similar to that of standard coherent detection. To achieve coherent detection with complex phase information, the local oscillator must mix with the signal with an in-phase and quadrature (90°) component. This can be achieved with the use of a 90° hybrid. Ideally, the component would be a 2x2 90° hybrid, mimicking the system above exactly, but this configuration is theoretically impossible (Hui & O'Sullivan, 2009). Therefore, a real substitute in the 3x3 90° hybrid can be used instead. The transfer function is as follows:

$$\begin{bmatrix} \vec{E}_1 \\ \vec{E}_2 \\ \vec{E}_3 \end{bmatrix} = \begin{bmatrix} \sqrt{0.2} & \sqrt{0.4} \exp(j\frac{3\pi}{4}) & \sqrt{0.4} \exp(j\frac{3\pi}{4}) \\ \sqrt{0.4} \exp(j\frac{3\pi}{4}) & \sqrt{0.2} & \sqrt{0.4} \exp(j\frac{3\pi}{4}) \\ \sqrt{0.4} \exp(j\frac{3\pi}{4}) & \sqrt{0.4} \exp(j\frac{3\pi}{4}) & \sqrt{0.2} \end{bmatrix} \begin{bmatrix} \vec{E}_s(t) \\ \vec{E}_{LO} \\ 0 \end{bmatrix}$$

Equation 8

where  $E_3$  has no power applied and only two outputs are used. Essentially, the 3x3 coupler is being used as a 2x2 coupler.

Working through similar math as before:

$$\vec{E}_{1}(t) = \sqrt{0.2}\vec{E}_{s}(t) + \sqrt{0.4}\exp(j\frac{3\pi}{4})\vec{E}_{LO}$$

Equation 9

$$\vec{E}_{2}(t) = \sqrt{0.4}\exp(j\frac{3\pi}{4})\vec{E}_{s}(t) + \sqrt{0.2}\vec{E}_{LO}$$

Equation 10

Continuing after photodetection and ignoring direct detection components:

$$i_1(t) \approx 2R\sqrt{0.08}\vec{A}_s(t) \cdot \vec{A}_{LO}\cos(\Delta \phi(t) - \frac{3\pi}{4})$$

Equation 11

$$i_2(t) \approx 2R\sqrt{0.08}\vec{A}_s(t) \cdot \vec{A}_{LO}\sin(\Delta \phi(t) - \frac{3\pi}{4})$$

Equation 12

Since the two current terms apply the cosine and sine of the time dependent phase difference, they extract perpendicular components of the light signal. Thus, complex information can be demodulated.

### **Digital-Subcarrier Multiplexing (DSCM)**

In order to make efficient use of the low-loss bandwidth of the optical fiber, wavelength division multiplexing (WDM) has been used widely. In a WDM system, multiple wavelengths are used to carry independent data channels along the same fiber. A frequency guard band is required such that crosstalk can be avoided when passing through a WDM de-multiplexing filter. Commercial high speed optical systems with 50 GHz channel spacing, 10 Gb/s data rate per channel, and 0.2 bit/Hz efficiency are widely deployed. Increasing data rates to 40 or 100 Gb/s will improve spectral efficiency, however these systems are sensitive to the impact of chromatic dispersion and polarization mode dispersion (PMD).

To continue to increase the spectral efficiency of fiber optic communication links while maintaining high quality of transmission, several techniques are being explored to combine several subchannels of data into a single optical signal, or wavelength. The subchannels can contain independent sets of data in each channel, or they can be modulated such that the entire channel is a single data stream. In the past, sub-carrier multiplexing schemes have been implemented in fiber-optic systems to partition a high data rate wavelength channel into many subchannels to significantly improve the tolerance to fiber chromatic dispersion and PMD. However, these subcarrier channels were created

with analog techniques, and as such, frequency spacing was still needed and spectral efficiency was not increased compared to traditional WDM technology.

Recent advances in high speed digital electronics enables multi-giga-sample operation of analog to digital converters (ADC), digital to analog converters (DAC), and digital signal processing (DSP). This allows the generation and processing of subcarrier channels in the digital domain, utilizing advanced digital modulation formats and DSP algorithms to dramatically increase spectral efficiency. We'll call this technique Digital Subcarrier Multiplexing (DSCM). Two currently popular DSCM techniques being implemented and studied are Nyquist-WDM (N-WDM) and Orthogonal Frequency Division Multiplexing (OFDM).

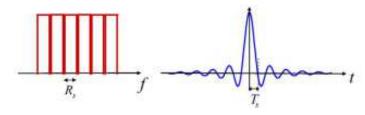

Figure 2 - Spectrum (left) and time pulse (right) for N-WDM (Gabriella Bosco, 2010)

Figure 3 - Spectrum (left) and time pulse (right) for OFDM (Gabriella Bosco, 2010)

N-WDM and OFDM can be thought of as "opposites" in the frequency and time

domains. An N-WDM pulse and the spectra of an OFDM subchannel will both, ideally, take

the shape of a sinc. The spectra of a single N-WDM channel and an OFDM spectra will both,

ideally, take the shape of a perfect square.

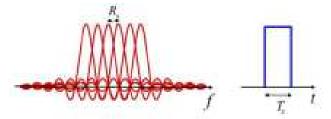

Figure 4 - Nyquist filter transfer function and spectrum at the output (Gabriella Bosco, 2010)

An OFDM signal is generated using the following transmit function (Q. Yang, 2011):

$$s(t) = \sum_{i=-\infty}^{+\infty} \sum_{k=1}^{N_{sc}} c_{ki} s_k (t - iT_s)$$

Equation 13

$$s_k(t) = \mu(t)e^{j2\pi f_k t}$$

Equation 14

$$\mu(t) = \begin{cases} 1, & (0 < t \le T_s), \\ 0, & (t \le 0, t > T_s) \end{cases}$$

Equation 15

where  $c_{ki}$  is the ith symbol of the kth subcarrier,  $s_k$  is the waveform of the kth subcarrier, the number of subcarriers is denoted by  $N_{sc}$ ,  $f_k$  is the subcarrier center frequency, and  $T_s$  is the symbol period. The last equation,  $\mu(t)$ , is the pulse shaping function. Rewriting the expressions, sampling the signal at N/T, and normalizing the equation by 1/N yields:

$$S_n=rac{1}{N}\sum_{i=0}^{N-1}A_ie^{j2\pirac{i}{N}n}$$

,  $n=0,1,\ldots,N-1$  Equation 16

where  $S_n$  is the nth time domain sample. Clearly, this expression is the same as an inverse discrete Fourier transform (IDFT) (Q. Yang, 2011). Similarly, to demodulate, a discrete Fourier transform is used:

$$A_i = \sum_{j=0}^{N-1} R_n e^{-j2\pi \frac{i}{N}n}, n = 0, 1, ..., N-1$$

Equation 17

where  $R_n$  is the received signal.

An OFDM system requires sampling of the entire spectrum of all the subchannels to be able to process the data of a certain subchannel (Junyi Wang, 2012). This is evident by the OFDM spectrum presented in Figure 3 as well as the IDFT modulation function. The breadth of research and algorithms to implement discrete Fourier functions can optimize the resource usage, or throughput speed, whichever is more crucial to the project.

The formation of a Nyquist-WDM transmit signal need only be filtered by an inverse-sinc filter set to the bandwidth of the subchannel, with a certain roll-off rate (such as 0.1). This allows the subchannels to have a flat spectral shape while minimally overlapping with adjacent subchannels. Ideally, the transmitter utilizes a filter with the number of taps equally that of the length of the signal (if packet based). A time domain or frequency domain filtering method can be chosen by the user based on ease of implementation.

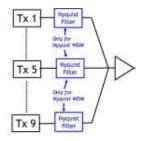

The full N-WDM channel can be created several ways depending on the requirements of the system. If all the signals originate in the same machine which is applying the digital filters, The filters can all be applied, as well as the subchannels shifted into their allotted frequency range, in one operation. If the different subchannels originate from several different sources, each signal can have a baseband filter applied, and the separate signals shifted into their slots, as completely independent operations. See Figure 5 for a diagram of the multiplexing scheme.

Figure 5 - Multiplexed N-WDM (Gabriella Bosco, 2010)

A clear advantage of Nyquist-WDM is the fact that a single subcarrier can be a separate entity of the signal (Junyi Wang, 2012). A subchannel can be added into an existing signal if that particular frequency slot is currently unoccupied. Also, a single channel of a Nyquist-WDM system can be sampled and demodulated independently: the entire N-WDM channel does not need to be sampled. Therefore, an intermediate router could drop one subchannel and add another to an existing N-WDM spectrum without disturbing adjacent subchannels. When considering a real system, N-WDM can extract a single channel using lower bandwidth ADC, saving money. This project studies the technique of N-DWM, the effects of the parameters in the receiver chain, and the tradeoffs of a realistic, cost effective build.

# General Communications and Applicable Digital Signal Processing

### **Anti-Alias Filter**

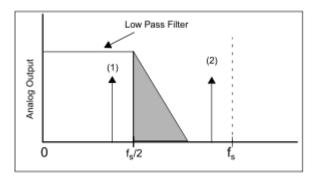

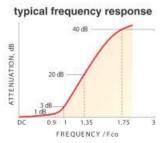

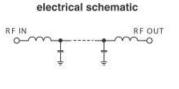

Figure 6 - Analog Anti-Alias Filter Example

If high spectral power exists beyond the Nyquist sampling rate of the ADC, an analog anti-aliasing filter is required (Baker, 1999). The chosen filter needs to sufficiently attenuate the out-of-band signals such that they will not interfere with the desired signal. Since the downshifted signal exists at baseband in this project, a lowpass filter is required for signals beyond the Nyquist frequency. For some systems, it is reasonable to employ a filter which has a passband with the same bandwidth as the Nyquist rate, attenuating undesirable signals beyond the Nyquist rate, as seen in Figure 6. This project, though, must demodulate a single subchannel from a very cluttered spectra. There is no guard-band in a perfect N-WDM system. Therefore, due to the specifications of real analog filters, the passband of the filter should occupy only a fractional portion of the 1st Nyquist region. This allows room for the rolloff of the filter's response from passband to Nyquist rate.

### **Digital Filtering**

Filtering is a fundamental aspect of communications. Filtering can, and must, be done in both the analog domain and in the digital domain. There are many advantages to filtering after the signal has been digitized. Analog filters have many non-ideal qualities: dependent on temperature, being produced with imperfect parts, taking up physical space, having relatively poor frequency rolloff, etc. Digital filters overcome these setbacks and add the advantage of programmability, easy integration in digital systems, ability to produce nearly any response, ability to adapt to incoming signals, and much more. There are inherent disadvantages in digital filering: quantization, complexity, and possible instability. The advantages clearly outweigh the disadvantages in this digital world and digital filtering is implemented everywhere it can be. Of course, it is not always an option, as with anti-aliasing filter above.

Digital systems most commonly implement linear filters. As the name implies, a filter is considered linear if the output signal is a linear function of the observations applied to the filter input (Haykin, 2002). The linear filter family splits into infinite impulse response (IIR) and finite impulse response (FIR). Simply put, the difference between the two is IIR filters apply feedback, whereas FIR filters contain only a feedforward path. Therefore, the response of each impulse subject to the IIR filter infinitely exists, whereas the response of the FIR filter exists only in the set number of taps.

The two filter types have many different features and uses. IIR filters can produce much sharper responses with fewer coefficients than FIR filters. FIR filters, though, have the advantage of always being stable, whereas IIR filters can have instability problems. IIR

filters are based off of analog filters, and thus easier to design; FIR filters are difficult to design without CAD support. A very important feature for communications is that FIR filters can have exactly linear phase.

Two specific forms of FIR filters important to this research is the interpolation match filter and the derivative filter. The interpolation match filter is essentially the combination of two separate filters to achieve an ultimate goal. As a linear system, the filters can be implemented in series in either order or, if possible, as a single combination. An interpolation filter's job is to remove the undesired spectral replications of the signal.

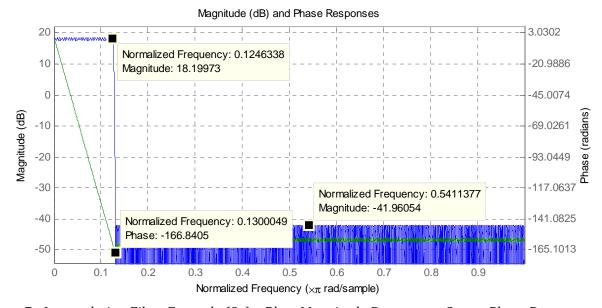

Figure 7 - Interpolation Filter Example (8x) – Blue: Magnitude Response – Green: Phase Response Figure 7 displays an example of an 8x interpolation filter. There are several key properties to notice. Firstly, the cutoff of the filter lies at 0.125, or 1/8 (Ifeachor & Jervis, 2001): the frequency of the signal decreased by 8 in the digital domain. It is important to add, though, the frequency of the signal has not actually changed; only its digital representation. A digital signal can take many forms based on the designer's requirements.

Secondly, the amplitude of the passband amplifies the signal by  $\sim$ 18.06 dB. This factor compensates for the loss of power during the interpolation process. Assuming the input signal is a voltage signal, the amplification is found by:

$$A = 20\log_{10}(N) [dB]$$

Equation 18

where N is the interpolation factor. Next, the phase response is linear throughout the passband. Since the phase information is equally as important as the magnitude in complex modulation, linear phase is required. The phase in the stop band needs not be linear, because the demodulator doesn't use the higher frequency information.

The Matlab "filter builder" tool created this filter, and all the filters henceforth in this project. This particular filter, in Figure 7, used the "Lowpass Design" with an "Interpolation Factor" of 8. The passband and stopband were specified at .125 and .13, respectively, with a passband ripple of 1 dB and stopband attenuation of 60 dB. The figure shows the stopband attenuated by 42 dB, but relative to the 18 dB amplification of the passband due to the interpolation, this equates to a 60 dB difference.

The above example is a simple interpolation filter with the passband including the entire original signal. A match filter is a single rate filter which selects a certain band, depending on the desired signal. An interpolation match filter combines both these concepts. The desired passband is scaled down and contained within the passband of the interpolation filter. Simply divide the passband and stopband frequencies of the match filter specifications by the interpolation factor to calculate the associated frequencies in the interpolated match filter.

Another important filter in this project is the derivative filter. This filter can also be implemented by an FIR filter. The following provides a quick proof on how the transfer function of the derivative is derived.

$$y(n) = \frac{d}{dn}x(n)$$

Equation 19

$$F\{y(n)\} = j\Omega \cdot X(\Omega)$$

Equation 20

$$Y(\Omega) = j\Omega \cdot X(\Omega)$$

Equation 21

$$\therefore H(\Omega) = j\Omega \rightarrow h(n) = \frac{\cos(\pi n)}{n}$$

where  $\Omega$  is the digital frequency component and  $F\{\circ\}$  is the Fourier transform operator. This function will return the derivative of the entire signal. Although the coefficients of this filter have a relatively simple function in this form, it becomes much more complicated in application. Usually the derivative of only a particular band is desired, as it is in this project. Therefore, Matlab design tools are employed to create the derivative filter.

A final note on Matlab filter builder design tools; the weight vector can save the number of taps and better tailor the filter. The filter design weight vector allows the user to specify which components of the transfer function are most important, and thus, the design tools should devote resources to. This is particularly helpful when there's a predefined number of taps available. For example, consider a lowpass filter. There are two critical components, outside of the frequency choices: passband ripple and stopband attenuation. A user could choose to define a weight vector (in the same order) of [1, .2] if the passband response must be flat, but does not require a significant amount of attenuation in the stopband.

### Viterbi-Viterbi Algorithm

A 4-QAM signal is constructed with a certain, predetermined phase. The QAM receiver is programmed to demodulate the signal, expecting a certain phase as well. The phase can differ depending on design requirements or preference. However, during the transmission and downshifting processes the received signal will suffer arbitrary phase shifts. Recall Equation 7, the output current from the photodetector after homodyne coherent detection.

$$i(t) \approx R\vec{A}_s(t) \cdot \vec{A}_{LO} \cos(\Delta \emptyset)$$

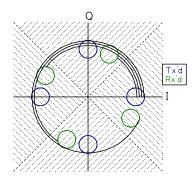

The  $\Delta\emptyset$  term represents this random phase shift. Figure 8 visualizes this random phase shift. The blue circles represent the transmitted QAM signal, and the green circles have experienced a phase change. The constellation must be realigned to the axes for the demodulator circuit to effectively do its job.

Figure 8 - Random Phase Shift Example – Blue symbol sent – Green symbol received

The Viterbi-Viterbi algorithm solves this problem. The first step is to estimate the

phase. Although the equation is applied in one step, it will be explained as a series of

operations. First, the phase of the incoming signal must be estimated (Kikuchi K., 2011).

The phase modulation should be removed by applying the M-power to the incoming

complex signal, where M-ary is the PSK format. The phase estimation is then averaged over 2k+1 samples to improve SNR of the estimated phase. Then apply the "angle" (or arg()) function to the complex average. This function is basically an arctangent function with an interval over  $[0,2\pi)$ . Finally, divide the angle by M to remove the power of M previously applied. The phase has now been estimated (Equation 22). Now subtract that phase error from the signal by complex multiplying the signal and the phase error, after negating the imaginary term.

$$\theta_e(n) = \arg\left(\sum_{j=-k}^k E(n-j)^M\right)/M$$

Equation 22

In this paper, the "Viterbi-Viterbi ratio" (V&V ratio) is equal to the number of samples to be averaged divided by the number of samples per symbol. For instance, if the received signal (after interpolation) has 10 samples per symbol and the phase estimation algorithm averages over 51 samples (k=25), the Viterbi-Viterbi ratio is 5.1.

The phase change also has a  $2\pi/M$  ambiguity (Kikuchi K. , 2011). Proper techniques must be utilized at the transmitter and receiver to combat these effects. A discussion of the method to overcome this barrier takes place in the implementation section of this paper.

# Symbol Recovery

Once the phase has been corrected the system must lock onto to the signal clock and perform symbol synchronization. This process' goal is to resample the signal at peak values of the received signal without the benefit of a dedicated clock signal. Some communication systems forfeit some bandwidth to transmit a data clock signal in order to simplify the receivers. In communication systems where bandwidth is at a premium and

cannot afford to sacrifice any for a clock signal, extra circuitry is required to synchronize the receiver with the data clock.

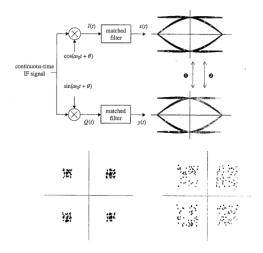

Figure 9 - Symbol Timing Example (Rice, 2009)

The above example shows the importance of proper clock synchronization. A QPSK signal enters the circuit from the left where it is downshifted by an in-phase and quadrature source and match filtered. An ideal eye diagram emerges from the filters. The constellation on the left was sampled at (1) arrow, and the constellation on the right corresponds with the (2) arrow. An approximate 15% symbol length shift dramatically deteriorates the constellation. Even with a clean, filtered signal, a bad symbol recovery circuit can ruin an otherwise good receiver.

Figure 10 - Eye Diagram Derivatives (Rice, 2009)

If a signal is being reclocked at the wrong time, one of the 4 following situations exists. Eye diagram (a) represents the timing occurring too early on the rising portion of the signal, (b) shows a late timing situation on the down slope, (c) is being clocked early on the downslope, and (d) is late on the upslope. The derivative of the signal clearly indicates the timing error, with larger magnitudes as the point drifts further from the center. This fact can be exploited and used in a feedback system to align the timing circuit. The indicator should have a positive sign if the timing is occurring early to increase the sampling time and negative when late. As it stands, the two early and late situation derivatives have opposite signs. To correct this, the sign of the signal can be multiplied to the derivative. Therefore, situation (a) and (c) produce a positive error and (b) and (d) produce a negative. Now these errors can be utilized to synchronize the system with the signal.

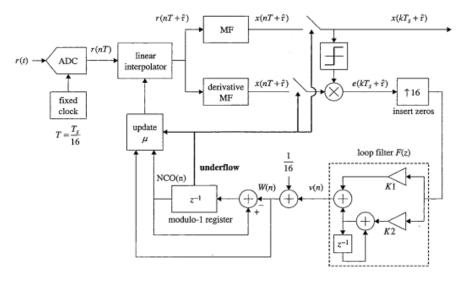

Figure 11 - Symbol Recovery Block Diagram (Rice, 2009)

First, a quick walkthrough of the circuit, followed by a more detailed explanation of the some of the components. The analog signal must be sampled by an ADC with a fixed clock source. A linear interpolator adds additional data points per symbol period. The interpolated signal feeds into a matched filter as well as a derivative filter. The resampling process takes place at this step, as directed by the update block. The derivative signal is multiplied to the sign of the match filter signal to adjust the sign of the derivative, as previously discussed. The error signal is zero padded by 16, the interpolated points per period in this example. This ensures the feedback loop only receives one error pulse per period. The proportional-plus-integrator filter allows the circuit to be tuned to a specific input signal. The processed error, v(n), is added to a constant 1/16 factor. This term, unaltered by v(n), would obviously accumulate to 1 after one symbol period. A modulo-1 register follows another summation, which also provides feedback. The update block processes the data from the modulo-1 register and the fixed summation and triggers the resampling process.

The most crucial part of this, and most, feedback systems is the loop filter. Many configurations exist, but the proportional-plus-integrator filter is attractive due to its balance of simplicity and effectiveness, producing an a steady state error of 0 for both the step and ramp function.

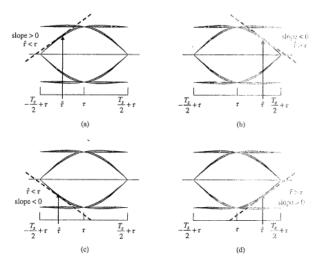

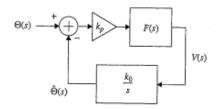

Figure 12 – Linearized Frequency Domain Phase Equivalent PLL (Rice, 2009) Figure 12 represents the model used to derive the gain coefficients. The phase estimate,  $\hat{\theta}(s)$ , is the output of the PLL. Let's being at V(s) to form the transfer function of the closed loop:

$$V(s) = k_p F(s) \left(\theta(s) - \hat{\theta}(s)\right) = \frac{s}{k_0} \hat{\theta}(s)$$

Equation 23

$$\hat{\theta}(s) * \left(s + k_0 k_p F(s)\right) = k_0 k_p F(s) \theta(s)$$

Equation 24

$$H_a(s) = \frac{\hat{\theta}(s)}{\theta(s)} = \frac{k_0 k_p F(s)}{s \mp k_p F(s)}$$

Equation 25

The continuous time function of a proportional-plus-integrator filter leads to the final closed loop transfer function:

$$F(s) = k_1 + \frac{k_2}{s}$$

Equation 26

$$\therefore H_a(s) = \frac{k_0 k_p k_1 s + k_0 k_p k_2}{s^2 + k_0 k_p k_1 s + k_0 k_p k_2}$$

Equation 27

$$H_a(s) = \frac{2\zeta \omega_n s + \omega_n^2}{s^2 + 2\zeta \omega_n s + \omega_n^2}$$

$$\zeta = \frac{k_1}{2} \sqrt{\frac{k_0 k_p}{k_2}}$$

where

$$w_n = \sqrt{k_0 k_p k_2}$$

The discrete time PLL is essentially is same as the continuous time model (Rice, 2009). An analog phase detector and loop filter are replaced by their discrete counterparts, and a direct digital synthesizer (DDS) replaces the VCO. The design of a digital PLL typically begins by transforming a continuous time version PLL to produce a discrete-time version (Rice, 2009). The process again starts by forming the transfer function from the linearized closed loop system. The two systems can be seen below in Figure 13.

Figure 13 - (above) discrete time PLL and DDS; (below) linearized phase equivalent Similarly as before, a transfer function can be derived from the system. A more complete derivation can be found in Appendix A.

$$V(z) = K_p F(z) \left(\theta(z) - \hat{\theta}(z)\right) = \frac{1}{K_0} \frac{1 - z^{-1}}{z^{-1}} \hat{\theta}(z)$$

Equation 29

$$\widehat{\theta}(z) * \left(\frac{1 - z^{-1}}{z^{-1}} + K_0 F(z)\right) = K_0 F(s) \theta(z)$$

Equation 30

$$H_d(z) = \frac{\hat{\theta}(z)}{\theta(z)} = \frac{K_0 F(s) \theta(z)}{\frac{1 - z^{-1}}{z^{-1}} + K_0 F(z)}$$

Equation 31

$$H_d(z) = \frac{K_p K_0 (K_1 + K_2) z^{-1} - K_p K_0 K_1 z^{-2}}{1 - 2(1 - \frac{1}{2} K_p K_0 (K_1 + K_2)) z^{-1} + (1 - K_p K_0 K_1 z^{-2})}$$

Equation 32

The digital gain factors,  $K_0$ ,  $K_1$ ,  $K_2$ , and  $K_p$ , can be found by incorporating the continuous time loop filter equation (Equation 26). Applying the bilinear transform to the continuous time transfer function produces a relation in the denominators that can be exploited. The full transformation can be found in Appendix B, resulting in the following digital representation of the continuous system:

Equation 33

$$H_a\left(\frac{2}{T}\frac{1-z^{-1}}{1+z^{-1}}\right) = \frac{\frac{2\zeta\theta_n + {\theta_n}^2}{1+2\zeta\theta_n + {\theta_n}^2} + 2\frac{2{\theta_n}^2}{1+2\zeta\theta_n + {\theta_n}^2}z^{-1} + \frac{-2\zeta\theta_n + {\theta_n}^2}{1+2\zeta\theta_n + {\theta_n}^2}z^{-2}}{1-2\frac{1-{\theta_n}^2}{1+2\zeta\theta_n + {\theta_n}^2}z^{-1} + \frac{1-2\zeta\theta_n + {\theta_n}^2}{1+2\zeta\theta_n + {\theta_n}^2}z^{-2}}$$

where

$$\theta_n = \frac{w_n T}{2}$$

Setting the coefficients of the  $H_a(s)$  (Equation 32) and  $H_d(z)$  (Equation 33) polynomials equal yields:

$$1 - \frac{1}{2}K_pK_0(K_1 + K_2) = \frac{1 - \theta_n^2}{1 + 2\zeta\theta_n + {\theta_n}^2}$$

Equation 34

$$1 - K_p K_0 K_1 = \frac{1 - 2\zeta \theta_n + {\theta_n}^2}{1 + 2\zeta \theta_n + {\theta_n}^2}$$

Equation 35

Some simple algebra solves for the loop constants:

$$K_p K_0 K_1 = \frac{4\zeta \theta_n}{1 + 2\zeta \theta_n + {\theta_n}^2}$$

Equation 36

$$K_p K_0 K_2 = \frac{4\theta_n^2}{1 + 2\zeta\theta_n + {\theta_n}^2}$$

Equation 37

The previous and following equations contain these variables: dampening ratio  $\zeta$ , natural frequency  $\omega_n$ , sampling period T, and equivalent noise bandwidth  $B_n$ . Substituting the  $\theta_n$  term for a proportional plus integrator filter produces the final result for the gain factors (Rice, 2009):

$$\theta_n = \frac{B_n T}{\zeta + \frac{1}{4\zeta}}$$

$$4\zeta \left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right)$$

$$K_p K_0 K_1 = \frac{1 + 2\zeta \left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right) + \left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right)^2}$$

Equation 38

$$K_p K_0 K_2 = \frac{4\left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right)^2}{1 + 2\zeta \left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right) + \left(\frac{B_n T}{\zeta + \frac{1}{4\zeta}}\right)^2}$$

Equation 39

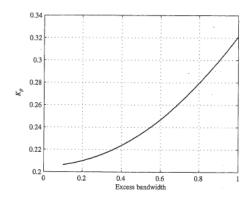

The  $K_1$  and  $K_2$  gain factors can now be calculated for the symbol recovery system. The dampening ratio is set to critically dampening at  $1/\sqrt{2}$ . For the modulo-1 system,  $K_0$  is set to -1. The noise bandwidth,  $B_nT$  and phase detector gain,  $K_p$ , depend on the specific application. The noise bandwidth factor must be tuned to the specific signal and its expected noise power. The value  $K_p$  can be extracted from the following chart:

Figure 14- Phase detector gain for raised cosine pulse

### Data Start Sequence

A crucial function of a communications system is determining the start of a data block. When processing the actual 1's and 0's being received after demodulation, the system must be able to identify the beginning of a string of data. One such tactic involves placing a certain, known data pattern at the start of the block and constantly scanning for the pattern. When the receiver detects the pattern it sets off a trigger and other digital components down the signal path can begin their necessary processes.

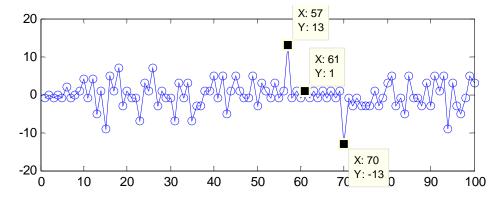

Barker codes are commonly used as a message preamble to mark the start. Barker codes are unique for their high peak to side lobe ratio. Barker codes produce a large spike (equal to the length of the Barker code) surrounded by small ripples when autocorrelated. This presents the system with a predictable and unique response to search for. To further the uniqueness and decrease the probability of a data anomaly triggering the system, a Barker sequence followed by a negated version can provide an even more uncommon response. Barker codes of length 1, 2, 3, 4, 5, 7, 11, and 13 have been discovered. The functional peak of the autocorrelated signal is equal to the length of the Barker code

Figure 15 displays the response of a correlation function of a random sequence with a regular and negated length 13 Barker codes inserted in the middle. Note the spikes of 13 at index 57 and 70 with values of 1 of -1 in between. The autocorrelation function replicates an FIR filter with the sequence values flipped from left to right. Therefore, any system with the access to FIR filters can implement the autocorrelation function, and therefore the Barker code start of sequence process.

Figure 15 - Random signal + length 13 Barker code correlated with length 13 Barker code

Preliminary Simulation, Simulink, and Post-Processing

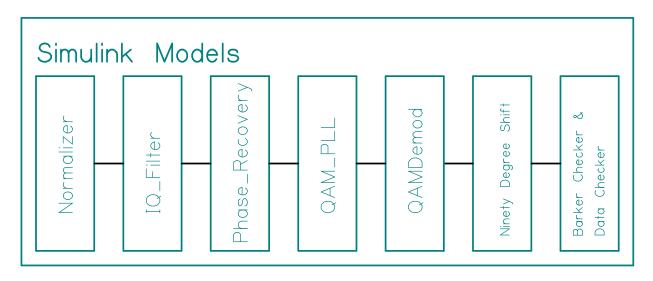

## Matlab Simulink Components

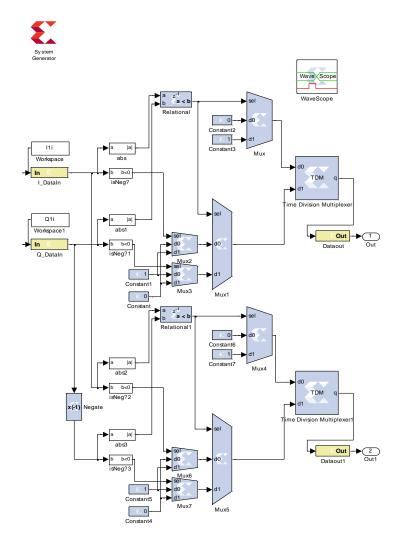

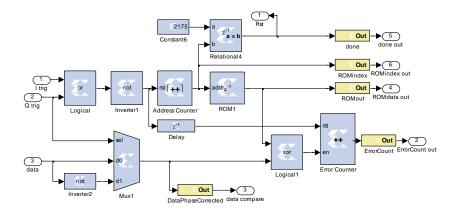

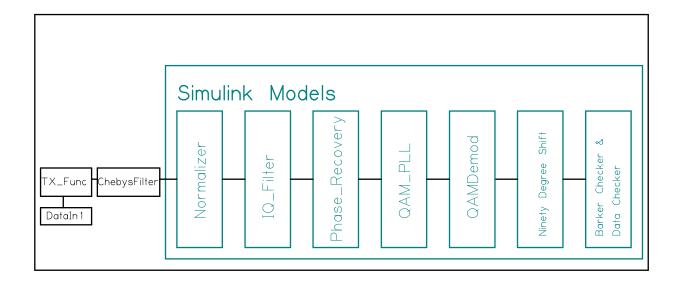

The following models were designed, created, and simulated in Matlab Simulink.

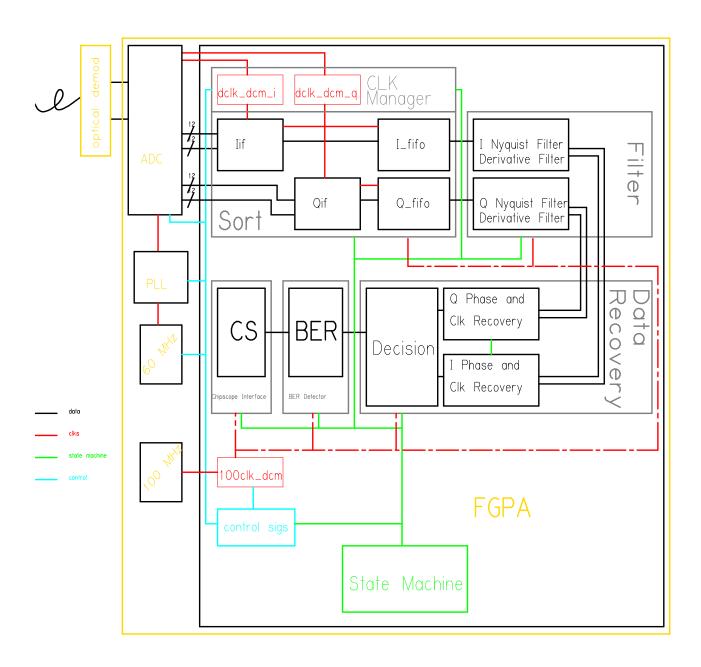

System Generator (in Simulink) then generates the models into VHDL files. These files were then connected and implemented in VHDL. The data chain follows the order of this section. The figure below shows a high level overview of the receiver system, sectioned off by Simulink model.

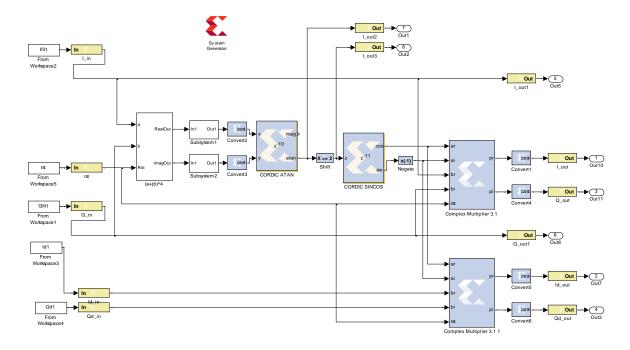

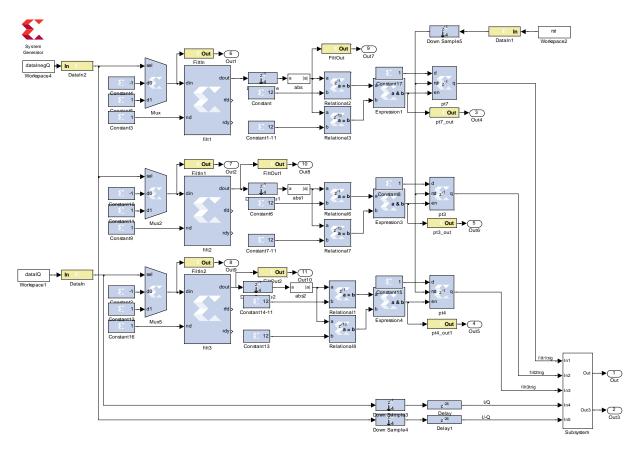

Figure 16 - Simulink Receiver System Configuration

The input data stream consists of 11 subchannels. The baseband channel is a pseudo-random binary data block and is consistent from trial to trial. The baseband channel is surrounded by 5 channels on each side which are randomly generated preceding each trial. Each data stream is individually modulated into 4QAM signals. From there, the subchannel signals are up or down-shifted to their respective center frequency, filtered by the Nyquist filter, and finally summed together to create the full channel. Subsequent to the Simulink model descriptions is further detail of the binary data generation and full channel transmit signal generation.

#### Normalizer

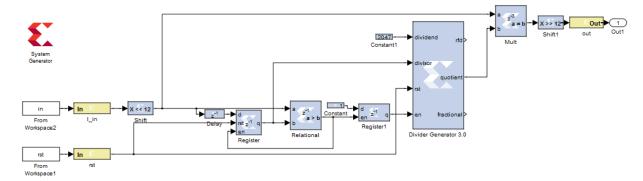

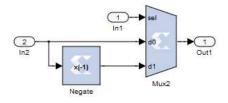

Figure 17 - Normalizer Simulink Model

The data stream must be normalized first before any digital signal processing. The normalization process ensures that all data blocks will be treated equally regardless of input magnitude. A signal well below the threshold voltages of the analog to digital converter will certainly be subject to a higher level of quantization error, and the normalization process cannot fix that problem. It is still necessary for the filtering process to always have relatively similar data magnitudes to ensure regularity. If the amplitude is too small, lesser fluctuations in the waveform can be lost in when rounding on the output.

This normalizer system first shifts the input signal leftward (higher) 12 bits. This is only necessary for the Simulink model to correctly place the decimal point in the divider block and does not actually take any FPGA resources. The delay, register, and relational blocks work to hold the maximum data amplitude in the register. Once the first maximum is found, Register1 enables the divider block. Being a signed 12 bit system, the maximum amplitude possible is 2047. The divider block creates a ratio of 2047 and the maximum detected point. This ratio is then multiplied to the data stream, such that the absolute value

product with the highest amplitude will be 2047. The binary number is then shifted back to a range of -.5:.5 and output.

## IQ\_filter

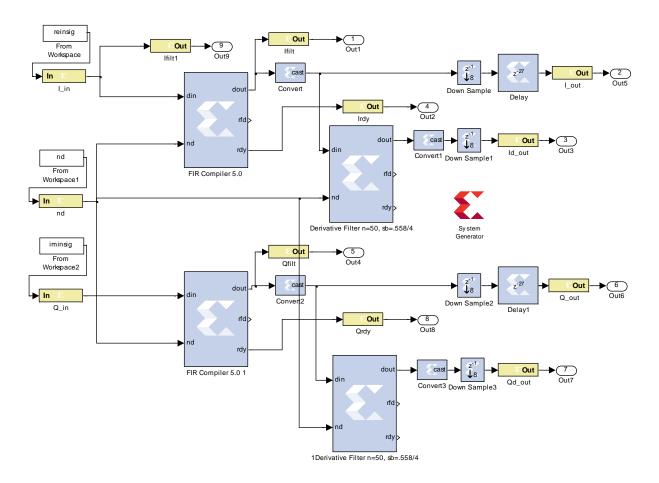

Figure 18 - IQ\_Filter Simulink Model

The two channels of data require filtering to implement the Nyquist WDM demodulation scheme. The inputs to this model are reinsig (the I channel data stream), iminsig (the Q channel data stream), and nd (set always to '1' to enable the filters). A 100 order inverse sync, match filter shapes the response. The normalized passband and cutoff frequencies are defined by:

$$F_{ch} = \frac{F_{s,Tx} * ChanSp}{Pt/Sym}$$

Equation 40

$$f_{p,mf} = \frac{F_{ch}}{F_{s,ADC} * N * ChanSp}$$

Equation 41

$$f_{c,mf} = \frac{F_{ch} * (2 - (1 - \beta))}{F_{s,ADC} * N}$$

Equation 42

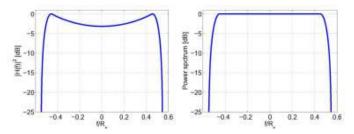

where  $F_{ch}$  is the subchannel symbol bandwidth ( $\sim$ 702 MHz for 32 point/symbol) at 100% channel spacing, ChanSp is the channel spacing ratio,  $F_{s,Tx}$  is the Tx sampling frequency ( $\sim$ 21.4 GHz),  $F_{s,ADC}$  ADC sampling frequency (1.6 GHz), N is the interpolation factor, and  $\beta$  is the N-WDM roll-off factor. This filter block also performs a 4x interpolation to increase the samples per symbol from 2.39 to 9.5621 in the 32 point per symbol case. The filter amplifies the passband region by  $\sim$ 12 dB to offset the 4x interpolation ( $20*log10(4) \sim 12$  dB). The cutoff frequency is placed at the peak Nyquist filter point of the closest adjacent sub-channel. The passband frequency is independent to the channel spacing, whereas the cutoff frequency is. This allows the filter more "room" to produce a flat passband response and higher level of rejection of undesired signals as the channel spacing is increased.

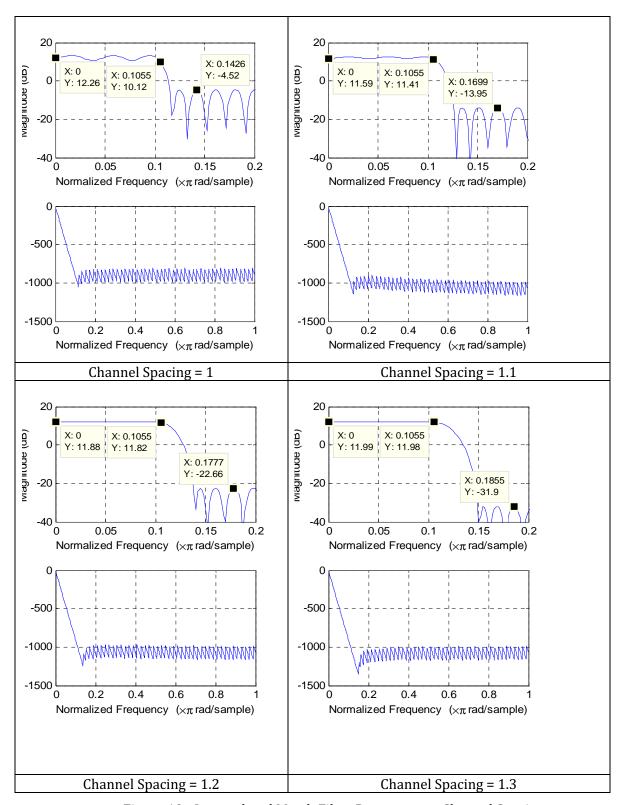

The following Table 1 defines some key attributes of different match filters with different channel spacing ratios. All the following assume a 32 points per symbol transmission rate, as above, which yields a single-sideband bandwidth of 334.7 MHz. The Fpass\*4 and Fstop\*4 columns are included to compare the true passband and stopband frequencies prior to interpolation. The Fpass and Fstop column reveal the normalized bandwidth, assuming a sampling frequency of 2 and the interpolation has been applied. Passband ripple is difficult to define because inverse sinc transfer function inherently introduces a difference in passband response, so a difference of adjacent ripples is used. The following estimate is the difference from DC to Fpass. The difference between the

Fpass and stopband peaks is the stopband attenuation. The selected filter design method, equiripple, produces a stopband with peaks of equal height; therefore selecting any peak for measure is adequate. As this is an interpolation filter, this stopband will include copies of the desired baseband signal as well as unwanted channels, thus a high level of relative rejection is required. The desirable linear phase response is realized in all the filters.

| channel | Fpass*4             | Fstop*4             | Fpass   Fstop | Passband    | Stopband         |  |

|---------|---------------------|---------------------|---------------|-------------|------------------|--|

| space   | (freq   normalized) | (freq   normalized) | (normalized)  | ripple (dB) | attenuation (dB) |  |

| 1       | 334.7 MHz   .418    | 352 MHz   .440      | .1046   .1150 | 2.56        | 14.64            |  |

| 1.1     | 334.7 MHz   .418    | 387 MHz   .484      | .1046   .1265 | 0.85        | 25.36            |  |

| 1.2     | 334.7 MHz   .418    | 423 MHz   .528      | .1046   .1380 | 0.31        | 34.48            |  |

| 1.3     | 334.7 MHz   .418    | 458 MHz   .572      | .1046   .1495 | 0.10        | 43.88            |  |

Table 1 - Interpolated Match Filter Specifications vs Channel Spacing

Figure 19 - Interpolated Match Filter Responses vs Channel Spacing

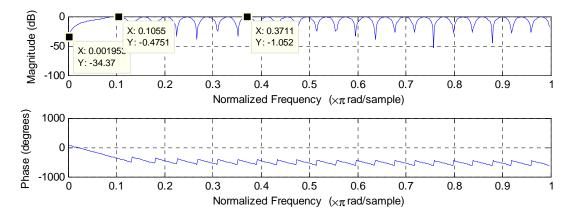

The method of clock recovery requires the derivative of the input signal to run a digital PLL. Therefore, after match filter processes the signal an FIR derivative filter calculates the change. A conversion block is placed between the two filters for ease of use and to reduce the resources necessary in the derivative filter by truncating the output. Since the derivative filter is in series with the matched filter, high attenuation in the signal stopband has already been achieved and mustn't be duplicated. Thus, the weight vector of the filter weighed heavily on the passband shape of the derivative and put less emphasis on the stopband.

Both the passband and cutoff frequencies of the derivative filter differ from the match filter. The passband does not divide out the channel spacing factor, allowing all the transmitted phase information to be encapsulated in output of the filter. The cutoff frequency is similar to the match filter's, only the 2/1.9 factor on the beta term opens the main lobe further to, again, transfer the maximum phase information of the baseband signal.

$$f_{p,df} = \frac{F_{ch}}{F_{s,ADC} * N}$$

Equation 43

$$f_{c,df} = \frac{F_{ch} * (2 - \frac{2}{1.9} * (1 - \beta))}{F_{s,ADC} * N}$$

Figure 20 – Derivative Filter Frequency Response

Finally, all the signal paths are downsampled by 8 to conserve resources. The delay blocks hold the match filter output value for 27 clocks to synchronize the signal with the correct phase of the derivative. Without the downsampling blocks the delay would be 8 times longer, unnecessarily wasting flip-flops. The block parameters of the filters and delay must be adjusted depending on input signal bandwidth and filter order. This is done automatically by inserting the appropriate variable names from the script into the prompts.

Due to the limited resources necessary to perform the FIR filtering in the FPGA (namely the 48 available XtremeDSP blocks), the matched and derivative filters are overclocked by 32 times the FIFO read data rate. Since the data from the matched filter is 4x interpolated, though, the derivative filter is only overclocked 8 times its input data rate. Further discussion on data clock rates located below in the simulation details.

## Phase\_Recovery

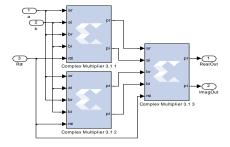

Figure 21 - Phase Recovery Simulink Model

To correct the phase and align the constellation to the transmitted signal, the Viterbi-Viterbi algorithm was implemented. The Simulink system is straight forward, with respect to the algorithm. First the complex signal is squared twice due to the 4 points of the constellation. The subsystem shown below completes this process, named " $(a + jb)^4$ " in Figure 21 above. The multiplication is a complex process as needed.

Figure 22 - "(a + jb)^4" Simulink Subsystem

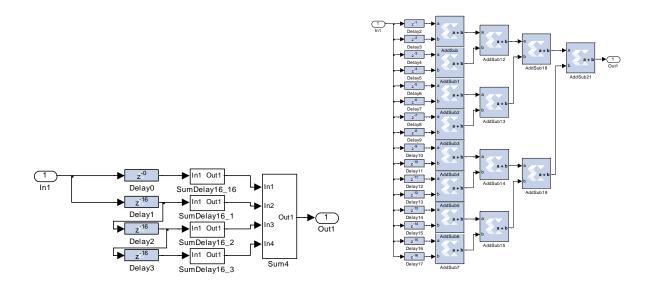

The product is independently summed over 64 points by channel. Ideally, the current point being aligned is centered in the summation by using delays on the pass-through data lines to assure proper alignment. For instance, the bottom two derivative lines would be delayed in order to be temporally aligned with the phase product calculated by the central Viterbi-Viterbi system. The thin linewidth of the local oscillator and requirement to save FPGA resources allows this process to be ignored. Figure 23 shows and implements the column of z-16 delays, followed by a chain of adders to complete the 64 point summation. Each proceeding 16 point delay is latched to the previous delay, thus the delay accumulates down the chain. Each delay feeds into a block which sums the last 16 data points. The "SumDelay16" block internals are shown to the right. The 4 16 point sums are then summed in "Sum4."

Figure 23 - Summing Simulink Subsystems

A "CORDIC ATAN" block calculates the magnitude and angle of the 64 points of data.

The magnitude of the point is unneeded and left unconnected. The "shift" block performs a

divide by 4 function by shifting the binary data right two places. This is to compensate for the fourth power operation. The "CORDIC SINCOS" outputs the cosine and sine of the current phase detected by the previous process. The final step involves keeping the sign of the cosine term, negating the sine term, and complex multiplying this to the current data point. The output constellation should then be corrected and rotated to the input phase, with the desired point means at 0, 90, 180, and 270 degrees.

# QAM\_PLL

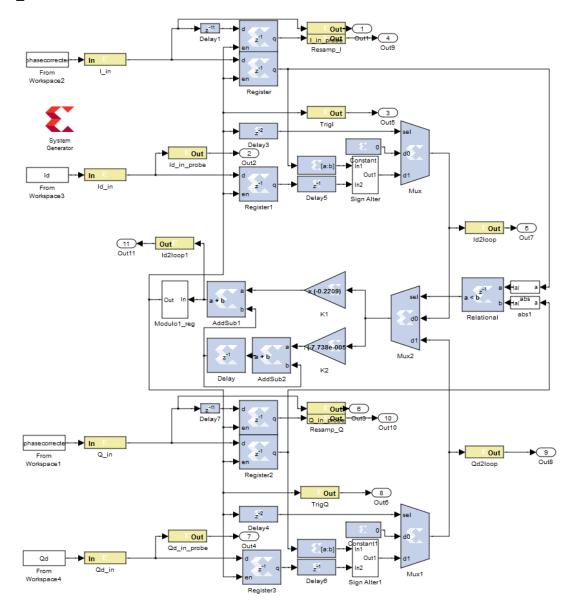

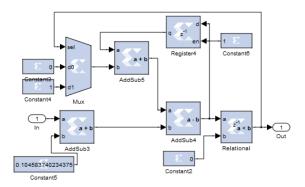

Figure 24 - QAM\_PLL Simulink Model

Figure 25 - Sign Alter Simulink Subsystem

Figure 26 - Modulo -1 Simulink Subsystem

The most complex system is the digital QAM PLL. The system consists of 2 equivalent components (the upper and lower portions of Figure 24), which come together into the center, feedback portion. The top (or I) equivalent component will be referred to in this discussion. The process of this system was discussed in detail in the previous section. The primary role of this system is to reclock the waveform to switch from the DAC clock domain to the QAM signal's clock domain. The data is reclocked by the column of registers. The 'enabled' source of the registers is the output of the modulo -1 subsystem, displayed in Figure 26.

Beginning at the inputs, the phase-corrected waveform and phase-corrected derivatives of both the I and Q channels are stored in the registers. The registers themselves begin with a 1 on their enabled ports, so after a single clock, the data continues to the output q of the registers. The very top register is the reclocked output of the system. The second register feeds into the relational input of the feedback loop and will be discussed shortly. The third subsection registers the derivative. As discussed previously, the sign of the derivative must be altered before being fed into the feedback system depending on whether the current clock approximation is in front of or behind the QAM peak. The signal's first bit, which represents the sign, and the derivative feed into the 'Sign Alter' subsystem to complete this process. The sign altered derivative and a constant '0' are ten muxed together. The 'sel' bit is the reclocking signal, such that the approximated peak's derivative passes through the mux for one clock, followed by zeroes until the next reclock

The center feedback section beings with a mux. This mux selects between the I and Q sign-altered derivative signals. The 'sel' bit chooses the derivative whose anti-derivative has a larger magnitude. For instance, consider a moment in time with I=0.8, Id=-.1, Q=0.1, and Qd=-0.3. The derivative signal selected to drive the feedback loop in this instance would be from the I side. The reason this extra layer of complexity was added is due to the band-limited nature of this system. When a QAM signal is very band-limited, as in a

Nyquist WDM signal, the peaks tend to be flatter than the zeros of the I and Q waveforms. Therefore, the derivative of the peaks more accurately represent whether the reclocking estimate is truly ahead or behind.

The feedback loop begins with the two scaling multipliers for the 1st and 2nd order signals. The two are summed and the 'Modulo1\_reg' preforms the reclocking process. First the scaled signal is added to 0.1046... which is the inverse of the ratio of clocks per symbol period of the transmitter clock and DAC clock. The 0.1046... constant creates a correctly spaced reclocking signal if the input stimulus consisted of only zeros. The summed signal subtracts subtracts from the feedback loop of the Modulo-1 counter. This creates the downward slope of the feedback loop. A relational block checks to see if the feedback difference is less than zero. If not, nothing happens. Once the difference is less than zero, a '1' is added into the loop to begin counting towards the next period, and a '1' is output to the outer system. This output signal is the reclocked signal which is the estimation of the input QAM clock.

## **QAMDemod**

Figure 27 - QAM Demod Simulink Model

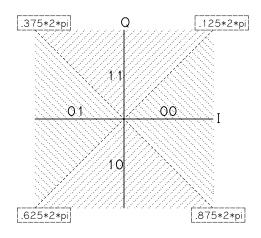

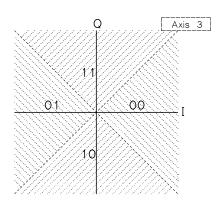

The QAM demodulation performed by this Simulink model requires no normalization to the input symbol. Figure 28 displays the demodulation decision areas; the solid lines define the I and Q data axes, the dashed line divides the QAM decision areas, and the dotted lines fill in the decision areas. The numbers at the end of each division line represent the angular location of the line. First, the absolute value of the I and Q points is taken and compared. Whichever has a larger magnitude chooses which axis on the

constellation the symbol exists. As seen in Figure 28, this decides the first binary digit of the symbol: I>Q=0, Q>I=1. The demodulator decides on the second digit based on the sign of the dominant point: I>Q, sgn(I) chooses second digit. Thus, since the decision engine relies only on the magnitude comparison of the two points and the sign of the larger, no the data requires no normalization for demodulation.

Figure 28 - Transmit QAM Constellation

The QAM Demod block simultaneously converts each QAM symbol into 2 different 2-bit words. One word is translated regularly from the I and Q (I/Q) symbol (the upper system in Figure 27). The second negates the Q value and translates the symbol from the I and –Q (I/-Q) symbol (the lower system in Figure 27). The two demodulators are otherwise equivalent. These two bit streams are needed for the following blocks to perform their phase correction duties.

## Ninety Degree Shift

Figure 29 - Ninety Degree Shift Simulink Model

The 90 degree shift model exploits the 11 length Barker codes located at the beginning of the data sequence. Referring to Figure 28, the data phase can flip over the I axis, over the Q axis, over either of the decision axes, or any combination of the 4. Therefore, sometimes the phase of the I axis is correct with respect to the expected constellation, but incorrect on the Q axis. For this reason, the QAM Demod box outputs the I & Q data stream and the I & -Q data stream.

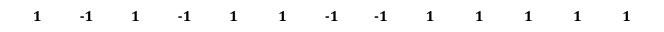

The length 11 Barker code has the following sequence:

| -1 | 1 | -1 | -1           | 1 | -1 | -1 | -1 | 1            | 1            | 1 |

|----|---|----|--------------|---|----|----|----|--------------|--------------|---|

| _  | _ | _  | <del>-</del> | _ | _  | _  | _  | <del>-</del> | <del>-</del> | _ |

#### Table 2 - Length 11 Barker Code

Note, to test the correlation the zeros are represented as negative ones to create a larger, more accurate spike in the correlation process. To check for 180 degree phase shifts on the Cartesian and constellation axes, 3 variations of the above code are checked with 1 more as default. The first, the default, does not flip any bits and feeds through the I/Q bitstream by leaving all the select bits of the MUXs on the bottom of the model set to 0. When this mode is enabled, the 00 transmitted phase is aligned with the 00 and so on.

The other 3 variations of the length 11 Barker code overhead will trigger one of the three similar paths. First, each path translates the zeros into negative ones with the input mux. The sequence of ones and negative ones are correlated with variations of the input Barker code using the FIR filter builder. By entering the following filter coefficients flipped left-to-right, the filter operation becomes a correlation operation.

| Symbol# | 1  |    | 2  |    | 3 |    | 4  |    | 5 |    |   |

|---------|----|----|----|----|---|----|----|----|---|----|---|

| Input   | -1 | 1  | -1 | -1 | 1 | -1 | -1 | -1 | 1 | 1  | 1 |

| Filt1   | -1 | 1  | -1 | -1 | 1 | -1 | -1 | -1 | 1 | 1  | 1 |

| Filt2   | -1 | -1 | -1 | 1  | 1 | 1  | -1 | 1  | 1 | -1 | 1 |

| Filt3   | -1 | -1 | -1 | 1  | 1 | 1  | -1 | 1  | 1 | -1 | 1 |

Table 3 - Barker code and Filter Coefficient Comparison

Note the partitioning by every 2 bits, because each QAM symbol represents 2 bits.

The absolute value of the output of each filter (correlator) is then taken. To cause a trigger to occur, the system must detect a magnitude 11 spike twice, exactly 12 samples apart. The separation between the spikes represents the length 11 Barker code, plus the extra bit added after each code in the data formation. The relational blocks check if the

data equals 11 at 1 delay (minimum) and 13 delay, for a separation of 12. The two outputs drive an AND logical block, whose output is a trigger lasting one clock length. To extend the trigger longer, the trigger sets the following D flip-flop. A reset signal is necessary to return the D flip-flop to 0. A universal reset follows the end of every data set.

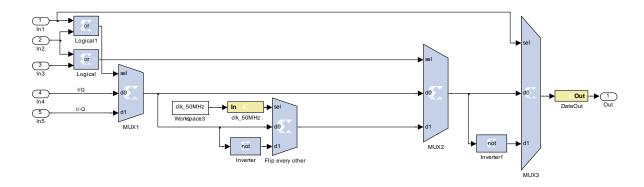

Figure 30- Constellation Correction Subsystem

The triggers control a system of MUXs choosing between different 90 and 180 degree rotated data lines, as seen in Figure 30. There are 4 MUXs in the subsystem. The first (left to right), named MUX1, chooses between it's the I/Q and I/-Q demodulated bitstreams. This flips the constellation over the I axis. The second MUX runs continuously on a 50 MHz clock, flipping every bit, regardless of the triggers. A 50 MHz clock is used as that is the data rate. Flipping every other bit flips the constellation over the I and Q axes at the same time: 11->10, 10->11, 00->01, and 01->00. The next MUX (MUX2) chooses between the unaltered data line or the one flipped by the 50 MHz clock. The final MUX (MUX3)chooses between another unaltered data line or one flipping every bit. This can be seen as flipping the constellation over Axis 3 in Figure 31. The following table breaks down the choices and how the data is altered.

Figure 31 - QAM Constellation Correction

| MUX  | SEL 0    | SEL 1           | Alteration         |

|------|----------|-----------------|--------------------|

| MUX1 | I/Q      | I/-Q            | Flip over I axis   |

| MUX2 | MUX1 Out | Not every other | Flip over I&Q axes |

| MUX3 | MUX2 Out | Not all bits    | Flip over Axis 3   |

Table 4 - Phase Shift MUX's Alterations

| Event         | MUX1 Select | MUX2 Select | MUX3 Select | Rotation |

|---------------|-------------|-------------|-------------|----------|

| No Trigger    | 0           | 0           | 0           | 0°       |

| Filt1 Trigger | 1           | 0           | 1           | 90°      |

| Filt2 Trigger | 1           | 1           | 1           | -90°     |

| Filt3 Trigger | 0           | 1           | 0           | 180°     |

Table 5 - Triggers vs MUX Selections

This whole system is 4 times overclocked with respect to the data rate to reduce the resources needed for the FIR components. After the data has been processed by the filters, the data lines are downsampled by 4 to their native clock speed. The blocks after the filters contain registers which would actually increase the resources used if the data was overclocked. The I/Q and I/-Q bitstreams are also downsampled and delayed before

entering the phase correction subsystem. The delays are necessary to correct the all the data processed by the system and not merely the data after a trigger event occurs.

#### Barker Checker & Data Checker

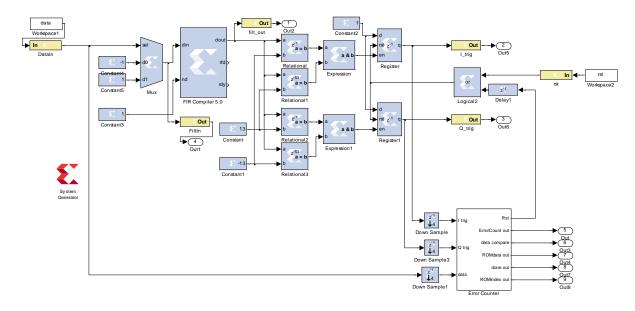

Figure 32 - Barker Checker and Data Checker Simulink Model

The bit error counter system completes the Simulink receiver. To begin counting and comparing the stored binary data to the received data it must be triggered. The system towards the top will trigger the BER comparator circuit much like the previous component, except the sequence the datastream is correlated with is the length 13 Barker code:

Table 6 - Length 13 Barker Code

The system has two triggers, one for a positive then immediate negative spike, one for the opposite. The data can still be 90° out of phase depending on the phase relation of the 50 MHz clock and the bitstream. A negative spike first will flip every 0 to 1 and every 1 to 0. The overclocked triggers and received binary data are downsampled and fed into the Error Counter Subsystem.

Figure 33 - Error Counter Subsystem