# Synthesis Techniques for Semi-Custom Dynamically Reconfigurable Superscalar Processors

BY

Jorge Ortiz

Submitted to the graduate degree program in Electrical Engineering and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Thesis Committee:

| Dr.      | Perry Alexander: Chairperson |

|----------|------------------------------|

| Dr.      | David Andrews: Co-Chair      |

| Dr.      | Arvin Agah                   |

| Dr.      | Swapan Chakrabarti           |

| Dr.      | James Sterbenz               |

| Dr.      | Kirk McClure                 |

| —<br>Dat | e Defended                   |

2009 Jorge Ortiz

The Dissertation Committee for Jorge Ortiz certifies that this is the approved version of the following dissertation:

# Synthesis Techniques for Semi-Custom Dynamically Reconfigurable Superscalar Processors

| Dr.     | Perry Alexander: Chairperson |

|---------|------------------------------|

| Dr.     | David Andrews: Co-Chair      |

| Dr.     | Arvin Agah                   |

| Dr.     | Swapan Chakrabarti           |

| Dr.     | James Sterbenz               |

| <br>Dr. | Kirk McClure                 |

#### Abstract

The accelerated adoption of reconfigurable computing foreshadows a computational paradigm shift, aimed at fulfilling the need of customizable yet high-performance flexible hardware. Reconfigurable computing fulfills this need by allowing the physical resources of a chip to be adapted to the computational requirements of a specific program, thus achieving higher levels of computing performance. This dissertation evaluates the area requirements for reconfigurable processing, an important yet often disregarded assessment for partial reconfiguration.

Common reconfigurable computing approaches today attempt to create custom circuitry in static co-processor accelerators. We instead focused on a new approach that synthesized semi-custom general-purpose processor cores. Each superscalar processor core's execution units can be customized for a particular application, yet the processor retains its standard microprocessor interface. We analyzed the area consumption for these computational components by studying the synthesis requirements of different processor configurations. This area/performance assessment aids designers when constraining processing elements in a fixed-size area slot, a requirement for modern partial reconfiguration approaches. Our results provide a more deterministic evaluation of performance density, hence making the area cost analysis less ambiguous when optimizing dynamic systems for coarse-grained parallelism.

The results obtained showed that even though performance density decreases with processor complexity, the additional area still provides a positive contribution to the aggregate parallel processing performance. This evaluation of parallel execution density contributes to ongoing efforts in the field of reconfigurable computing by providing a baseline for area/performance trade-offs for partial reconfiguration and multi-processor systems.

I dedicate this dissertation to the three most important women in my life.

To my mother, who shaped me into the man I am today.

To my sister, for encouraging me to touch the sky.

To my fiancée, for sharing her life with me.

# Acknowledgments

I would like to thank my committee members for helping me decide on an area of focus for my education through their coursework.

A special thanks to Dr. David Andrews, my advisor, for initiating me into research, and allowing me enough freedom to choose a project of my liking.

I wish to also thank my labmates for their insights and feedback for the implementation of this project, especially Jason, whose clever solutions saved me weeks of work.

# Contents

| A  | ccept | cance Page                                             | ii  |

|----|-------|--------------------------------------------------------|-----|

| Li | st of | Figures                                                | x   |

| Li | st of | Tables                                                 | xii |

| 1  | Intr  | roduction                                              | 1   |

|    | 1.1   | Background                                             | 1   |

|    | 1.2   | Reconfigurable Computing                               | 2   |

|    | 1.3   | General-purpose specialized processor                  | 3   |

|    | 1.4   | Processor characteristics                              | 4   |

|    | 1.5   | Processor evaluation                                   | 4   |

|    | 1.6   | Toward dynamic run-time reconfiguration                | 5   |

|    | 1.7   | Dissertation Organization                              | 5   |

| 2  | Obj   | fectives                                               | 6   |

|    | 2.1   | Create a configurable superscalar processor            | 6   |

|    | 2.2   | Processor's synthesis onto reconfigurable fabric       | 7   |

|    | 2.3   | Monitoring resource use under different configurations | 8   |

|    | 2.4   | Evaluating resource use and area expenditure           | 8   |

|    | 2.5   | Constraining area for slotted synthesis                | 9   |

|    | 2.6   | Thesis Statement                                       | 9   |

|    | 2.7   | Contributions                                          | 9   |

| 3 | Rela | ated W | Vork                                                                         | 11 |

|---|------|--------|------------------------------------------------------------------------------|----|

|   | 3.1  | Introd | luction                                                                      | 11 |

|   | 3.2  | ASIC   | technologies                                                                 | 12 |

|   | 3.3  | Recon  | figurable computing background                                               | 13 |

|   | 3.4  | Types  | of reconfigurable computing $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ . | 15 |

|   |      | 3.4.1  | Reconfigurable architectures                                                 | 15 |

|   |      |        | 3.4.1.1 Granularity                                                          | 15 |

|   |      |        | 3.4.1.2 Structure                                                            | 15 |

|   |      |        | 3.4.1.3 Reconfigurability                                                    | 18 |

|   |      | 3.4.2  | Soft-core processors                                                         | 18 |

|   | 3.5  | Currer | nt State of soft-core processors                                             | 20 |

|   |      | 3.5.1  | Xilinx - MicroBlaze                                                          | 21 |

|   |      | 3.5.2  | Altera - Nios II                                                             | 22 |

|   |      | 3.5.3  | Lattice - LatticeMico32                                                      | 22 |

|   |      | 3.5.4  | Other soft-core processors                                                   | 23 |

|   | 3.6  | Instru | ction-level parallelism                                                      | 23 |

|   | 3.7  | Hepha  | nestus' approach                                                             | 25 |

|   | 3.8  | Summ   | ary                                                                          | 28 |

|   |      |        |                                                                              |    |

| 4 | Imp  | olemen | tation Methodology                                                           | 29 |

|   | 4.1  | Struct | ure and configuration variables                                              | 29 |

|   |      | 4.1.1  | Rationale                                                                    | 31 |

|   |      | 4.1.2  | Advantages                                                                   | 32 |

|   |      | 4.1.3  | Disadvantages                                                                | 32 |

|   | 4.2  | Instru | mentation                                                                    | 34 |

|   |      | 4.2.1  | Platform Selection                                                           | 34 |

|   |      | 4.2.2  | Programming language                                                         | 35 |

|   |      | 4.2.3  | Simulation tools                                                             | 35 |

|   |      | 4.2.4  | Synthesis tools                                                              | 35 |

|   | 4.3  | Model  | implementation                                                               | 36 |

|   |      | 4.3.1  | Design Overview                                                              | 36 |

|   |      | 4.3.2  | Components                                                                   | 39 |

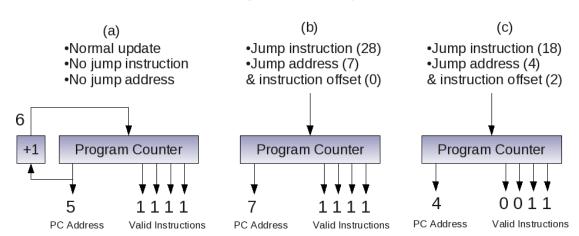

|   |      |        | 4.3.2.1 Program Counter                                                      | 39 |

|   |      |        | 4.3.2.2 Instruction Memory                                                   | 41 |

|     |                   | 4.3.2.3 Jump Decoder                                                                                                                 |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------------------------|

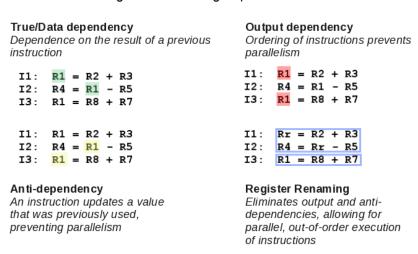

|     |                   | 4.3.2.4 Register Rename                                                                                                              |

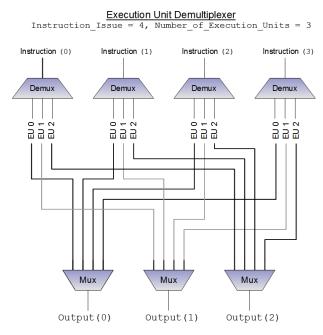

|     |                   | 4.3.2.5 Execution Unit Demultiplexer                                                                                                 |

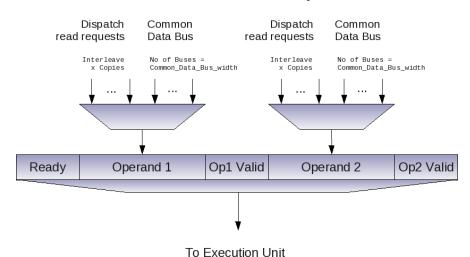

|     |                   | 4.3.2.6 Instruction Dispatch                                                                                                         |

|     |                   | 4.3.2.7 Register File/Future File                                                                                                    |

|     |                   | 4.3.2.8 Reservation Station Manager                                                                                                  |

|     |                   | 4.3.2.9 Execution Unit Manager                                                                                                       |

|     |                   | 4.3.2.10 Common Data Bus                                                                                                             |

|     |                   | 4.3.2.11 ReOrder Buffer                                                                                                              |

|     | 4.3.3             | Interconnect                                                                                                                         |

|     |                   | 4.3.3.1 Pipeline Control                                                                                                             |

|     |                   | 4.3.3.2 Design Hierarchy                                                                                                             |

|     | 4.3.4             | Protocols                                                                                                                            |

| 4.4 | Proces            | ssor assessment                                                                                                                      |

|     | 4.4.1             | Instruction set architecture                                                                                                         |

|     | 4.4.2             | Software execution                                                                                                                   |

|     | 4.4.3             | Simulation and debugging                                                                                                             |

|     | 4.4.4             | Synthesis                                                                                                                            |

|     | 4.4.5             | Reconfigurability                                                                                                                    |

|     | 4.4.6             | Limitations                                                                                                                          |

|     | 4.4.7             | Complexity                                                                                                                           |

| 4.5 | Summ              | ary                                                                                                                                  |

| Eva | luatio            | n 75                                                                                                                                 |

| 5.1 | Area ı            | ase                                                                                                                                  |

|     | 5.1.1             | Synthesized area                                                                                                                     |

|     | 5.1.2             | Area constraints                                                                                                                     |

|     | 5.1.3             | FPGA resources                                                                                                                       |

|     | 5.1.4             | Area cost metrics                                                                                                                    |

| 5.2 | Perfor            | mance gains                                                                                                                          |

|     | 5.2.1             | Clock frequency limitations                                                                                                          |

|     |                   | 5.2.1.1 Register Rename delay                                                                                                        |

|     |                   | 5.2.1.2 Instruction Dispatch delay                                                                                                   |

|     | 5.2.2             | Performance metrics                                                                                                                  |

|     | 4.5<br>Eva<br>5.1 | 4.3.4 4.4 Proces 4.4.1 4.4.2 4.4.3 4.4.4 4.4.5 4.4.6 4.4.7 4.5 Summ  Evaluation 5.1 Area to 5.1.1 5.1.2 5.1.3 5.1.4 5.2 Perfor 5.2.1 |

| 5.3   | Performance/area evaluation               | 90  |

|-------|-------------------------------------------|-----|

|       | 5.3.1 Instruction-execution density       | 90  |

|       | 5.3.2 Bit execution density               | 91  |

|       | 5.3.3 Maximum instruction execution       | 91  |

| 5.4   | Summary                                   | 92  |

| 6 Res | sults and Discussion                      | 94  |

| 6.1   | Performance                               | 9   |

|       | 6.1.1 Clock frequencies                   | 95  |

|       | 6.1.2 Logic and routing delays            | 96  |

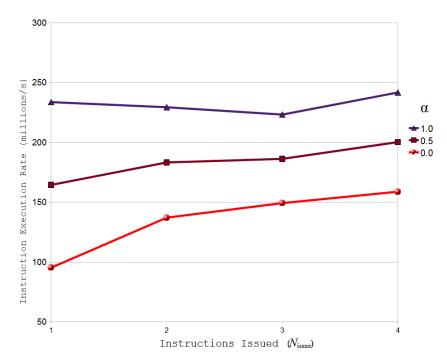

|       | 6.1.3 Instruction Execution Rate          | 98  |

|       | 6.1.4 Processor configuration performance | 10  |

| 6.2   | Area                                      | 104 |

|       | 6.2.1 Costs of Parallelism                | 10  |

|       | 6.2.2 Total area                          | 10  |

|       | 6.2.3 Area Constraints                    | 109 |

|       | 6.2.4 Area Use Reduction                  | 110 |

|       | 6.2.5 Synthesis time                      | 11: |

| 6.3   | Performance/Area trade offs               | 11: |

|       | 6.3.1 Maximum execution rate              | 11: |

|       | 6.3.2 Instruction execution rate density  | 110 |

|       | 6.3.3 Bit execution density               | 118 |

|       | 6.3.4 Secondary Independent Variables     | 119 |

| 6.4   | Summary                                   | 125 |

| 7 Coi | nclusions                                 | 12  |

| 7.1   | Limitations and Future Work               | 120 |

| 7.2   |                                           | 12' |

|       |                                           |     |

128

# List of Figures

| 3.1  | ASIC vs FPGA Market                        | 13 |

|------|--------------------------------------------|----|

| 3.2  | FPGA Dollar Consumption                    | 14 |

| 3.3  | Regular Reconfigurable Architectures       | 16 |

| 3.4  | Morphware Terminology                      | 17 |

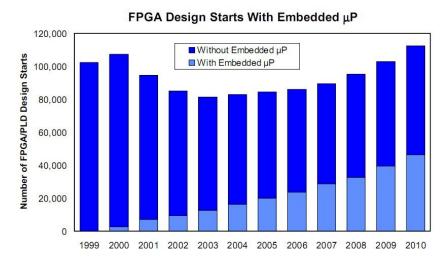

| 3.5  | Microprocessor Use in FPGAs                | 19 |

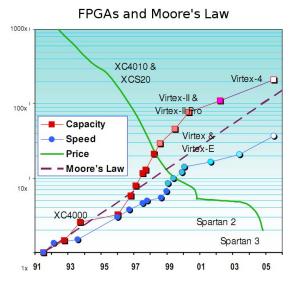

| 3.6  | FPGAs and Moore's Law                      | 26 |

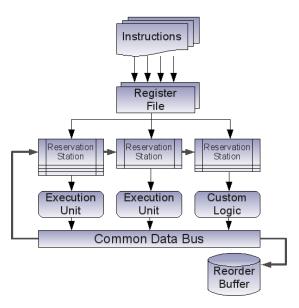

| 4.1  | Simplified Hephaestus Structure            | 30 |

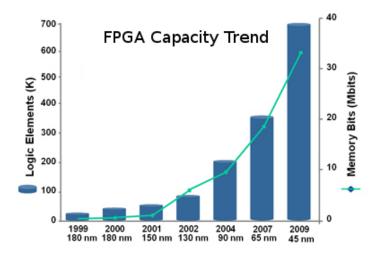

| 4.2  | FPGA logic element and memory capacity     | 33 |

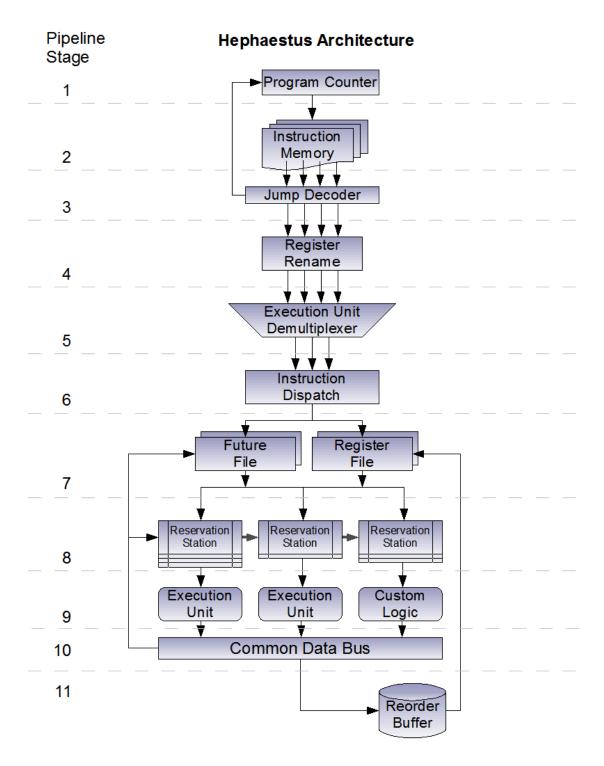

| 4.3  | Hephaestus Superscalar Structure           | 38 |

| 4.4  | Program counter updates                    | 40 |

| 4.5  | Instruction memory Block RAM configuration | 42 |

| 4.6  | Instruction memory locations               | 42 |

| 4.7  | Register-renaming dependencies             | 44 |

| 4.8  | Mapping and reclaiming registers           | 46 |

| 4.9  | Demultiplexing instructions                | 49 |

| 4.10 | Register/Future File Organization          | 52 |

| 4.11 | Reservation Station Entry                  | 53 |

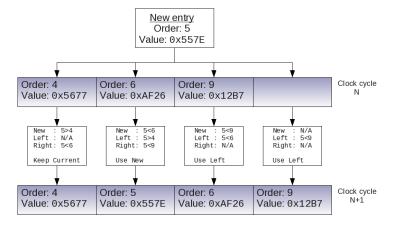

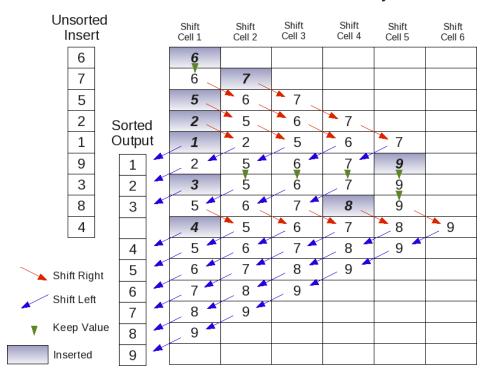

| 4.12 | Shift Cell Logic                           | 57 |

| 4.13 | ReOrder Buffer Functionality               | 58 |

| 4.14 | Instruction Set Architecture               | 64 |

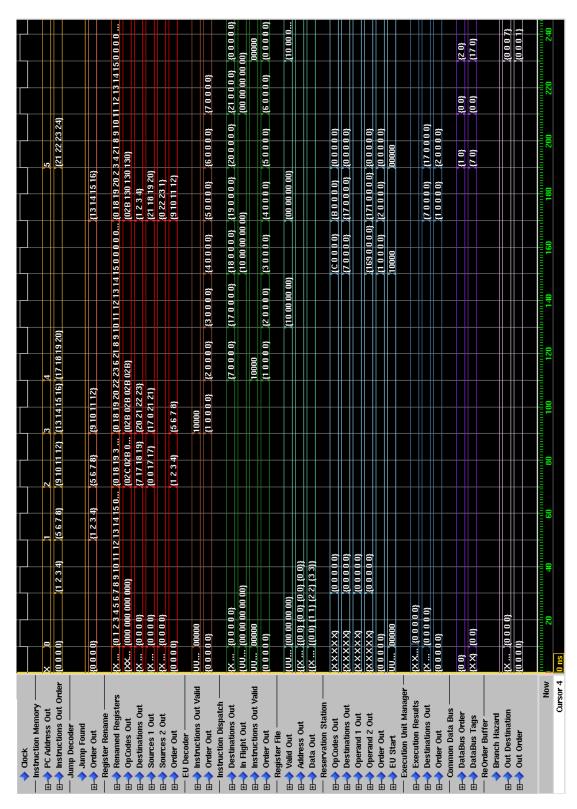

| 4.15 | Pipeline Simulation                        | 67 |

| 4.16 | Matrix Multiplication Results              | 68 |

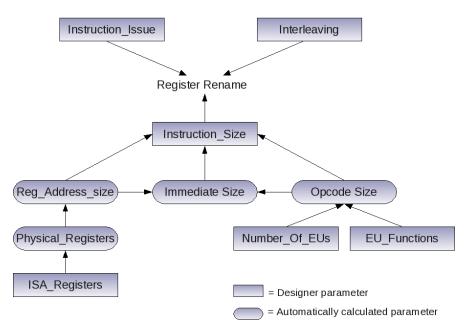

| 4.17 | Synthesis parameter dependencies           | 71 |

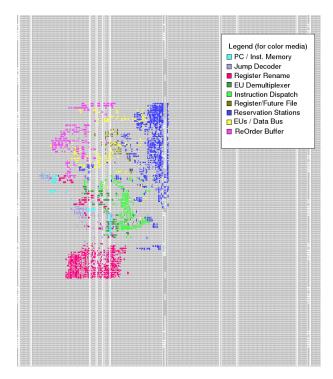

| 5.1  | Unconstrained Area                     | 77  |

|------|----------------------------------------|-----|

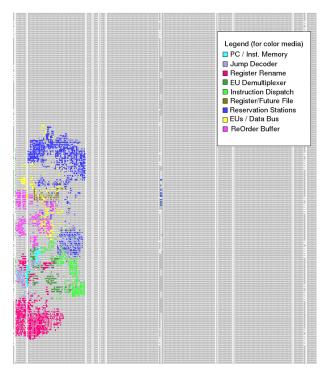

| 5.2  | Constrained Area 1                     | 79  |

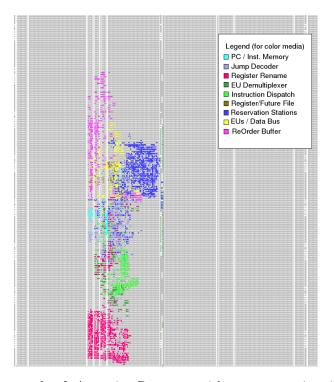

| 5.3  | Constrained Area 2                     | 80  |

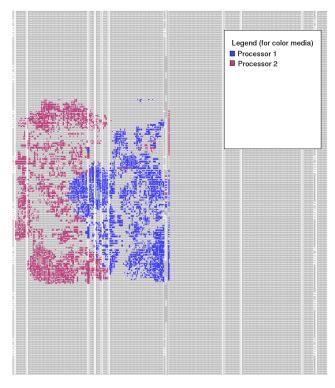

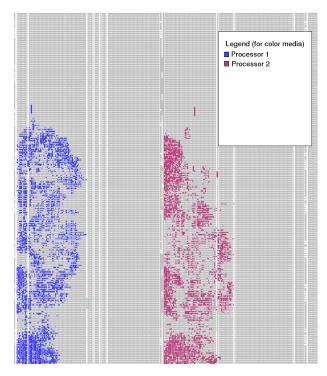

| 5.4  | Dual-processor system                  | 81  |

| 5.5  | Dual-processor floorplanning           | 82  |

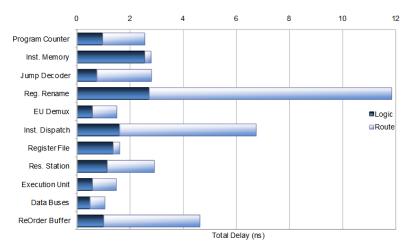

| 6.1  | Pipeline Stage Delay                   | 97  |

| 6.2  | Logic Delay by EU                      | 98  |

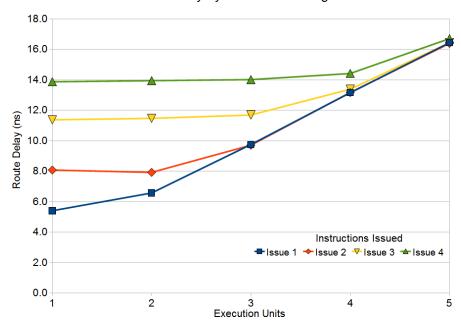

| 6.3  | Route Delay by EU                      | 99  |

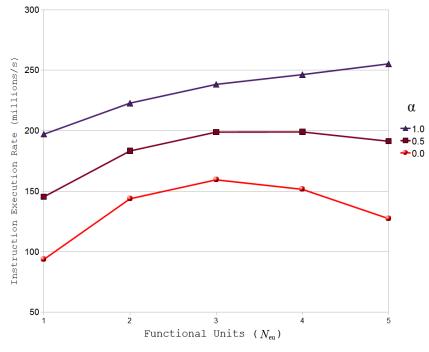

| 6.4  | Instruction Issue IER                  | 100 |

| 6.5  | Functional Units IER                   | 100 |

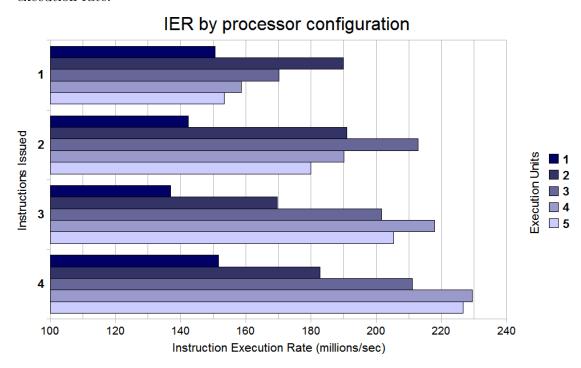

| 6.6  | Figure: Instruction Execution Rate     | 102 |

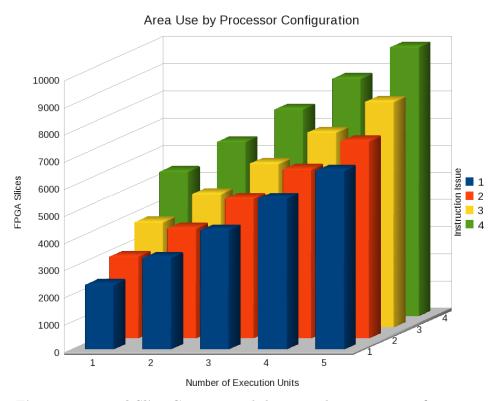

| 6.7  | Total Slice Count                      | 105 |

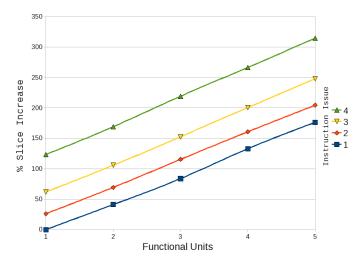

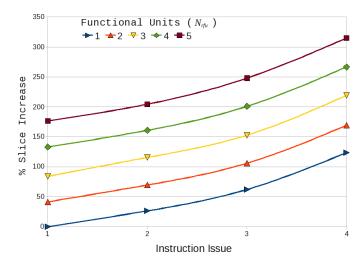

| 6.8  | Area Increase per Execution Unit       | 106 |

| 6.9  | Area Increase per Instruction Issue    | 106 |

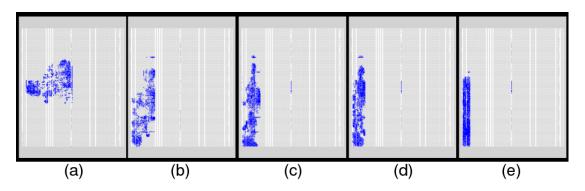

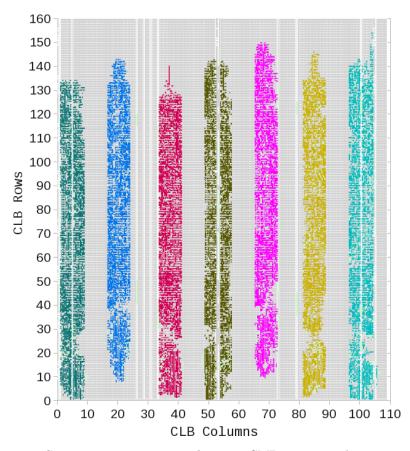

| 6.10 | Floorplanning                          | 109 |

| 6.11 | Seven processors 16 columns            | 110 |

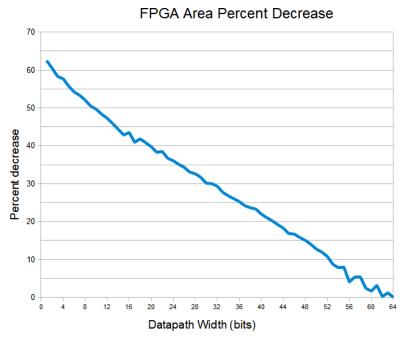

| 6.12 | Datapath Area Use                      | 111 |

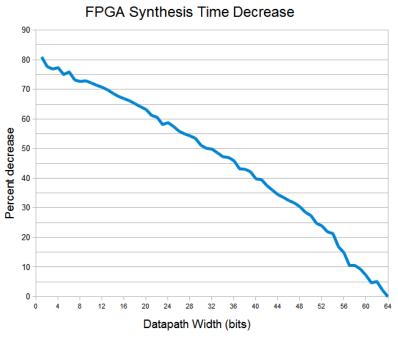

| 6.13 | Datapath Synthesis Time                | 112 |

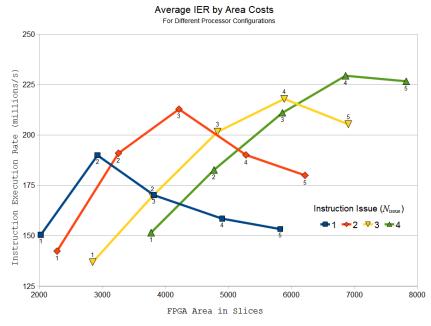

| 6.14 | IER by Area Costs                      | 113 |

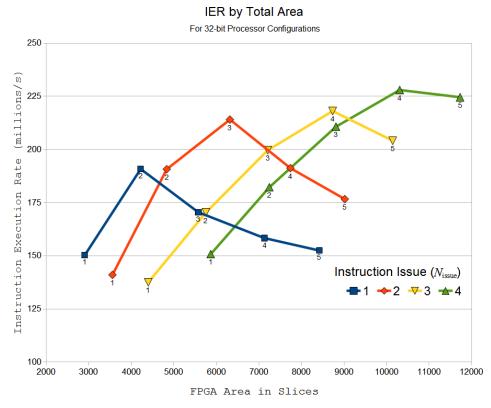

| 6.15 | IER by Area Costs - 32 bits            | 114 |

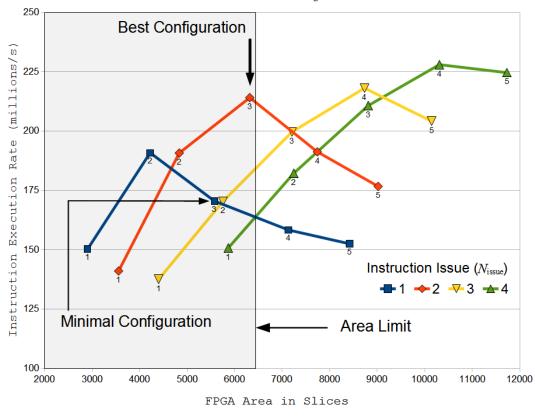

| 6.16 | Best IER Configuration - 32 bits       | 115 |

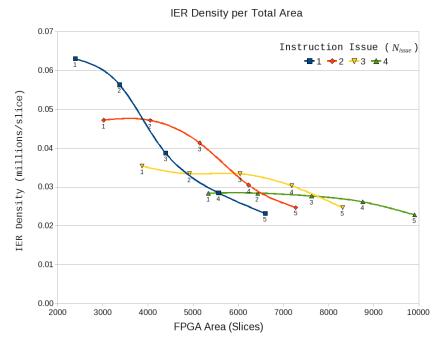

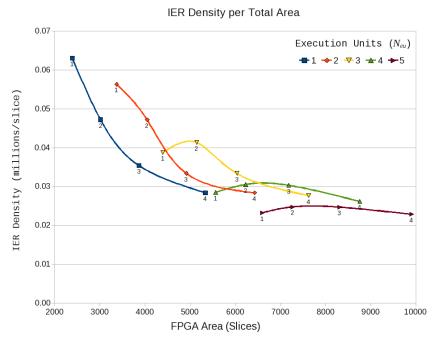

| 6.17 | IER Density by Instruction Issue       | 117 |

| 6.18 | IER Density by Execution Units         | 117 |

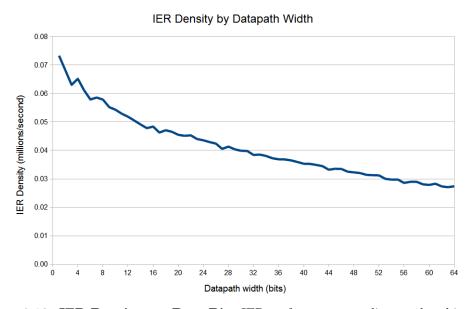

| 6.19 | IER Density per Data Bit               | 118 |

| 6.20 | IER Data Bit-Density by Datapath Width | 119 |

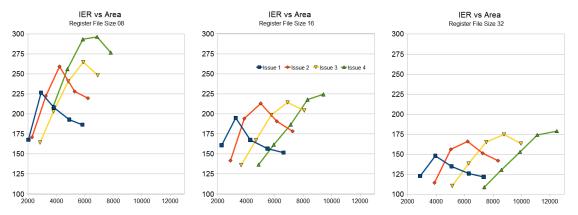

| 6.21 | IER/Area per Register File Size        | 120 |

# List of Tables

| 4.1 | Hazard Hierarchy Label                          | 61  |

|-----|-------------------------------------------------|-----|

| 4.2 | Soft-core processor execution comparison        | 65  |

| 5.1 | Virtex II Pro components                        | 83  |

| 5.2 | Virtex 5 components                             | 83  |

| 5.3 | Virtex II Pro CLB density                       | 85  |

| 5.4 | Virtex 5 CLB density                            | 85  |

| 5.5 | Interleaving 4 instructions                     | 87  |

| 5.6 | Interleaving 2 instructions                     | 87  |

| 5.7 | Interleaving 1 instructions                     | 87  |

| 5.8 | System Setup 1                                  | 89  |

| 5.9 | System Setup 2                                  | 89  |

| 6.1 | Clock Frequencies (MHz) for processor subset.   | 95  |

| 6.2 | Normalized Clock Frequencies                    | 96  |

| 6.3 | Maximum IER (millions/second)                   | 101 |

| 6.4 | FPGA Slice Use                                  | 105 |

| 6.5 | Percent Area Increase by Processor Architecture | 107 |

| 6.6 | Area Equation Values by System Parameters       | 108 |

# List of Code

| 4.1        | VHDL package definition                                              | 36       |

|------------|----------------------------------------------------------------------|----------|

| 4.2        | Instruction Memory in BlockRAM                                       | 41       |

| 4.3        | Instruction Memory synthesis report                                  | 41       |

| 4.4        | Register rename signal declaration                                   | 45       |

| 4.5        | Register Renaming Issue Dependencies                                 | 47       |

| 4.6        | VHDL reservation station definition and assignment for a system with |          |

|            |                                                                      |          |

|            | <pre>Number_of_Execution_Units = 3</pre>                             | 54       |

| 4.7        | Number_of_Execution_Units = 3                                        | 54<br>68 |

| 4.7<br>4.8 |                                                                      |          |

|            | C code for Array Multiplication                                      | 68       |

| 4.8        | C code for Array Multiplication                                      | 68<br>69 |

# Chapter 1

# Introduction

### 1.1 Background

Huge advancements made in general-purpose computing have created several paradigm shifts within the field of computer architecture over the last three decades. The great improvement of the individual components of computing systems, such as memory, processing, and communication, led to a consequential improvement of the systems as a whole. Microprocessor availability pushed the development of personal computers, and the wide acceptance of the latter drove the research to increase performance and productivity. Studies on the importance of instruction sets led to the emergence of architectures tailored toward unit-cycle base instructions (RISC) and multi-cycle complex instructions (CISC). Instruction pipelining increased throughput, while alternative ways to solve data-dependencies and conditional branch instructions were unveiled. Deeper pipelining became a mainstream practice for its consequential advantage of producing higher clock frequencies. To reduce pipeline stalling penalties, out-of-order execution and branch prediction were added to the architectures. The inherent timing differences of heterogeneous instructions were exposed, giving birth to dedicated execution units.

As hardware became faster, smaller, and cheaper, it became an affordable resource. Application-specific hardware became common practice for custom circuitry that demanded dedicated computation. For general-purpose processors, the conservative utilization of hardware was sacrificed to move away from single-instruction, single data

stream (SISD) architectures and exploit instruction, data and thread parallelism. Specialized single-instruction, multiple data stream (SIMD) processors appeared to map onto parallelizable problem domains, such as array and vector processing, and were closely followed by processors whose circuitry allowed for multiple instructions per cycle (VLIW). Returning to its roots, general-purpose computing inherited supercomputer techniques used to exploit instruction-level parallelism in order to become superscalar processors. Tomasulo's algorithm [1] emerged to resolve data dependencies in varying operational latency execution units. Thus, Tomasulo's algorithm gave birth to register renaming, a now common performance-enhancing technique both in commercial and scientific computing.

Throughout this whole era, both application-specific and general-purpose static processors were designed, manufactured, and used, followed by their inevitable fall to disuse and obsolescence, as new product-lines and processors were implemented. At the same time, the evolution of software code by means of high abstraction-level programming showed how important flexibility and reusability is in a market of primarily static processing. The notion of hardware with characteristics similar to its software counterpart suddenly became relevant.

## 1.2 Reconfigurable Computing

Because of the increased programmability of reconfigurable hardware, reconfigurable computing, a common ground for high-performance specialized systems and low-cost general-purpose processors, was created. The emergence of reconfigurable computing provided an alternate computing paradigm for engineers to exploit. This computing paradigm, which allows the use of flexible hardware, was first proposed by Estrin in the late 1950's [2]. Within the last 10 years, the technology base has matured to a point that enables us to use Estrin's original vision, by statically configuring and allocating reconfigurable components.

Reconfigurable computing invited interesting insights into the decades-old struggle between application-specific and general computing. Initially, tightly-coupled reconfigurable co-processing units could be added as extensions to the general-purpose Central Processing Unit (CPU) instruction set. They provided performance boosts by mapping portions of the application onto a faster hardware circuit They also provided compile-time versatility, by allowing different applications to be compiled and synthesized onto

a single board. Current trends continue along this path and move the reconfigurable fabric even closer to the general-purpose CPU. These trends seek to decrease the communication costs of moving data between the CPU and field programmable gate arrays (FPGA) across a general-purpose system bus, allowing data to be shared through the CPU's register set. Research work such as GARP [3] went as far as defining a new CPU architecture that embedded reconfigurable fabric within the CPU. The reconfigurable fabric could then be configured as a specialized execution unit within the CPU. Unfortunately this approach cannot exploit sufficient amounts of parallelism to justify the overhead of moving data and instructions into and out of the reconfigurable fabric.

In contrast to the GARP approach of exploiting fine-grained parallelism through loop unrolling, researchers are now investigating approaches to support coarse-grained parallelism within FPGAs. Current work investigates thread level parallelism, such as research done by Vuletic [4, 5] for static systems, Platzner [6, 7] for dynamic systems, and Hybrid Threads [8, 9, 10] for hybrid systems. These approaches follow modern methods of allowing programmers to express applications as sets of independent threads that can communicate through shared memory or message-passing paradigms.

## 1.3 General-purpose specialized processor

Our approach, named Hephaestus, follows the trend of supporting thread-level parallelism within a computational core, but at the same time allows the exploitation of instruction-level parallelism through modern computer architecture approaches. The processor core can statically reside in the reconfigurable fabric and allow different configurations in terms of instruction issue, execution units, reservation stations, and common data bus width. These configurations can be tailored to try to achieve an optimal design in which an application can achieve maximum number of instructions per cycle.

While multiple processors try to integrate reconfigurable logic into the processor itself [3, 11, 12, 13], Hephaestus takes an orthogonal approach by implementing the processor onto the reconfigurable logic. Other soft-core processors have been mapped onto reconfigurable logic [14, 15, 16, 17, 18], providing scalar single-issue performance. Implementing a superscalar architecture in reconfigurable fabric is much slower than the processor's built-in execution units for standard computations, such as floating point and complex integer arithmetic [3, 11]. However, we can expect this timing cost to be

amortized by flexibility of design, ability to increase the number of instructions issued, and rising clock frequencies and density for reconfigurable logic.

The main motivation for this project was studying the relationship between the increasing density advantage of FPGAs [19] versus the area cost associated with superscalar issue width growth, in which overhead increases quadratically [13]. Another one was examining the number of opportunities for exploiting instruction-level parallelism with different processor configurations.

#### 1.4 Processor characteristics

A key element for the flexibility of the number of Execution Units (EU) and their associated reservation stations is the adaptive Tomasulo's algorithm, which controls instruction issue and completion to/from the EUs. This register-renaming algorithm is implemented in hardware and uses the processor's configuration as parameters. At synthesis time, the system assigns tags to all available EUs for name resolution. Register renaming, with its well-documented advantages, is used when issuing instructions, broadcasting results, and completing instructions. The processor handles the non-trivial tasks of multi-instruction issue, name resolution, and instruction organization, dispatch, execution, broadcast and completion. These were implemented for a variable number of instruction widths, numbers and types of EUs, and sizes and bandwidth of the register file.

To get the comparable speedups of custom-dedicated hardware, Hephaestus allows application-specific user-logic to be implemented in its architecture. A user can reserve one or multiple execution units for such purpose, similar to the way a typical co-processing unit architecture uses a co-processor to enhance performance. A restriction placed on the user-logic is that it must adhere to the EU interface to fit in the system.

#### 1.5 Processor evaluation

The different configurations of the Hephaestus processor provides great system-component versatility, and consequently, vastly different use of reconfigurable fabric resources. We synthesized an array of configurations, varied by discrete differences in the system's independent variables:

- Instruction issue

- Number of execution units

- Common data bus width

- Register file size

- Register file memory organization

- Reservation station organization

- Reorder buffer size

The effect of these variables on the system's architecture is further explained in section 4.1. The dependent variables were then evaluated from the resulting maximum system clock frequency and resource use from synthesizing the permutations of the independent variables.

## 1.6 Toward dynamic run-time reconfiguration

Finally, for the purposes of dynamic reconfiguration, an additional task was to partition the superscalar processor and its execution unit configuration into regularly-sized areas. This allowed for synthesis of individual configurations, given a base system. These pre-synthesized configurations are prime candidates to be replaced using run-time reconfiguration, provided the host reconfigurable platform supports the communication needs between static and dynamic modules of the design.

# 1.7 Dissertation Organization

The rest of this dissertation is organized as follows: The objectives of the project are presented in Chapter 2; related work is presented in Chapter 3, while Chapter 4 describes the implementation methodology. Chapter 5 explains the evaluation of the project and the results are shown on Chapter 6. Finally, Chapter 7 places this work in the current state of the field.

# Chapter 2

# **Objectives**

This dissertation investigated new directions for synthesizing semi-custom circuits for dynamically reconfigurable systems. Our approach was to focus on synthesis techniques for computational-cores that can be confined within regularly sized reconfiguration slots.

This enabled us to pursue the main objectives of the Hephaestus project:

- Create a configurable superscalar processor

- Synthesize the processor onto reconfigurable fabric

- Monitor resource use under different processor configurations

- Evaluate resource use and area expenditure

- Constrain the area for slotted synthesis

# 2.1 Create a configurable superscalar processor

In our approach we examined processor structures that allow a variety of execution Units (EU's) to operate in unison and exploit intrinsic instruction level parallelism (ILP).

For our superscalar processor, we explored classic computer architecture techniques that allow multiple instructions to complete during any given clock cycle. Pipelining, with its associated control logic, was used to allow our techniques to exploit the performance increases from technology advancements. This is an important consideration and

motivation within field programmable gate array (FPGA) reconfigurable devices, which currently follow Moore's law and will benefit from higher clock frequencies over the next decade. The FPGA level of technology is at a level of speed and density comparable to 1980's CMOS fabrication techniques, promising to evolve at the same or faster rate [19].

Hardware description languages (HDL) allow us to define hardware behavior in terms of software code. We employed VHDL to define the model, interface, interconnect and parameters of our processor. With it, we can change the entire processor's configuration by simply altering the system parameters to match our desired setup. This is another motivation of the project, to allow a designer to easily balance the flexibility offered by a general-purpose programmable processor and the benefits of custom circuits.

Our semi-custom approach further enables a system designer to include user-logic into the Hephaestus processor. One (or more) of the generic execution units included with the system can be replaced as needed by a designer, to accomplish specific tasks on the target reconfigurable platform.

### 2.2 Processor's synthesis onto reconfigurable fabric

Reconfigurable computing allowed us to define flexible system specifications for hardware, and in addition, map the configured hardware onto its fabric.

We aimed not only to define the hardware specification but also to make it synthesizable onto modern, commercially-available reconfigurable architectures. Hence, Hephaestus' correct behavior is not only established by simulation, but also by synthesizing onto these architectures.

The HDL source code for the reconfigurable processor was kept as technology-independent as possible. This permitted the whole project to be easily portable between different reconfigurable platforms. Design portability is an important concern in reconfigurable computing, since cross-platform implementation is directly dependent on it. Lack of portability sometimes cripples development time when migration between devices is needed, even within the same device family [20]. HDL coding styles were used to make the design independent of technology or vendor-specific pragmas.

# 2.3 Monitoring resource use under different configurations

The component configuration of our processor can have a startling impact on performance, however, so can the nature of the program running on the provided processor configuration. Performance maximization in a reconfigurable system is analogous to customization. Thus, depending on the program's requirements, our reconfigurable processor can provide an appropriate configuration. This customization can enhance and optimize the worst, average and best case computational scenarios as required, by adjusting structural composition.

The varying types, numbers and complexity of the resources used by these structural composition were collected for the various permutations of processors configurations, to be analyzed into comprehensive relationships between requirements and necessary resources.

### 2.4 Evaluating resource use and area expenditure

The flexibility of most reconfigurable architectures, especially FPGAs, is usually associated and exploited from its homogeneous arrays of logic gates [21, 22]. Nowadays, they tend to be more heterogeneous, often including memory units, specialized processing elements, and even embedded processors cores [14, 23]. Synthesizing tools referee the use of device-specific resources for performance gains, but most of the system logic is mapped onto homogeneous reconfigurable fabric. The evaluation of this area consumption makes a metric suitable for resource use under different structural compositions.

The analysis portion of this work focuses on quantifying this performance versus generalization trade off. Clearly, performance benefits of a semi-custom processor structure may fall short of those gained by a fully-custom implementation. However, the area, reconfiguration overhead and scheduling implementation costs of the fully custom approach outweigh the loss of peak performance gains for semi-custom synthesis. By collecting performance needs, and then correlating them with the associated resource use, we evaluated the performance benefits of using our processor.

#### 2.5 Constraining area for slotted synthesis

We do not claim to achieve dynamic, or even partial, reconfiguration in our project. Dynamic reconfiguration is still evolving, in search of the right problem for its benefits to solve [24]. However, we did show that it can be adapted to different sized slotted areas through (mostly vendor-specific) synthesis techniques. This property, in conformity to reconfiguration techniques, can then support the necessary conditions to allow partial reconfiguration to be used for multiple configurations of our processor(s).

Hence, one could take an array of suitable processor configurations, synthesize them with the same area constraints in different board locations, and download one or more of these onto an FPGA board. In this way, our project is able to meet the current requirements for reconfigurable computing.

#### 2.6 Thesis Statement

Our proposed objectives, mixed with the need to address area issues in reconfigurable computing, thus combine into our thesis statement:

Synthesis techniques can confine soft-core processors to have a regularly sized area while enhancing parallelism. Evaluation of the performance density provides a baseline for area / performance trade-offs for partial reconfiguration and multi-processor systems.

#### 2.7 Contributions

The end goal of Hephaestus is probing for computational performance gains while subsidizing reconfiguration costs through synthesis. Other specific objectives of the project were to attain competitiveness in performance, by using historically-significant advances in processor design, mapping and pipelining heterogeneous instructions to different EUs, increasing instruction throughput, and achieving higher clock frequencies. The methods for achieving applicability, adaptability, optimization and reconfigurability are further described in Chapter 4. The implementation of the reconfigurable superscalar processor architeture contributes to the field by:

- achieving a balance between flexibility offered by a general-purpose programmable processor and the benefits of custom circuits,

- creating a flexible, extensible processor that adapts to an application's computational needs, without the long implementation times needed for fully-custom systems, and

- establishing a hybrid solution that allows custom parallel logic within standard processor architecture framework.

Also notably, this work enhances modern reconfiguration techniques by defining and refining a set of synthesis constraints to facilitate a multi-threaded fusion of general-purpose and specialized computing. Application of specialized and general-purpose processing in the reconfigurable computing research area is detailed in Chapter 3. The data collection and analysis from processor performance and area use for different configurations contributes to the field by:

- evaluating the attainable parallel execution for custom applications in a reconfigurable processor framework,

- quantifying the area requirements for parallel-execution gains, and

- calculating and predicting the performance in a confined area for partially reconfigurable and multiprocessor systems.

# Chapter 3

# Related Work

#### 3.1 Introduction

Increasing performance for a specific application has traditionally been achieved by customizing circuits for it. The gains achieved by customization are far superior to those achieved by modifying commercial off-the-shelf components. With dedicated hardware, the end product is usually an optimized system, meeting or exceeding the application's speed and area requirements.

Another way to enhance performance is by exploiting parallelism. The underlying idea is to think smarter, not harder. With parallelism, performance is gained from the decomposition of the problem into independent computations, and not from faster dedicated hardware. These computations can then be executed simultaneously, at the instruction, data or thread level. Early adopters of this paradigm included the CDC 6600 computer [25], which was the predecessor of pipelined Reduced Instruction Set Computers (RISC), and IBM's System 360/91 [26], which provided out-of-order instruction execution through floating point units executing in parallel with the main processor.

Custom circuitry with parallel computations combines the advantages of both approaches. However, each approach has disadvantages that compound each other. Custom circuits have lengthy development and time-to-market times, are not reusable, and are expensive in terms of non-recurring engineering and low-scale production costs.

Parallel computing consumes an increased area in hardware, has a complex design, and does not scale well. Custom circuitry with parallel computing generally results in a poor implementation for the large array of applications which require high performance, but can't sacrifice adaptability, reusability, programmability, area and cost.

Emerging technologies like reconfigurable computing can address the balance between performance and system cost. The wide variety of existing and proposed reconfigurable systems deal with different aspects of what constitutes performance, and what constitutes system cost. In this chapter we review these options and justify the motivations, objectives and methodology of the Hephaestus project.

### 3.2 ASIC technologies

A well-established method of meeting a program's computational demands is by using an Application-Specific Integrated Circuit (ASIC). ASICs allow the use of custom logic to tackle the demands mentioned before: optimization, area consumption and increased performance. However, the cost, inflexibility, and time-to-ship of ASICs do not make them a satisfactory solution in most of these cases [27, 28]. In fact, development costs for ASICs are approaching \$20 million for a 90-nm ASIC design with an embedded System-on-Chip (SoC), and \$40 million for the 45-nm version [29].

Non-recurring engineering costs comprise most of the ASIC's price tag. While the mass production of a finished ASIC is cheap, the costs associated with the development of the circuit are not. FPGAs solve this problem by allowing implemented circuits to be downloaded onto a single platform multiple times. They are becoming the default platform for reconfigurable computing and even ASIC development, because in sharp contrast to ASIC implementations, FPGAs can provide a SoC for a few hundred dollars (at the time of writing). This is a common reason why hardware designers turn to reconfigurable computing, either to design ASICs, to implement their application in an FPGA, or a hybrid of both [30].

But ASICs are not without merit. When writing about the future of reconfigurable systems, Scott Hauck, points out a law of FPGAs vs. ASICs [31]:

For any FPGA-based application, there is an ASIC implementation of the system that is AT LEAST as fast, dense, power-efficient, and cheap in (very) high volumes as the FPGA-based solution.

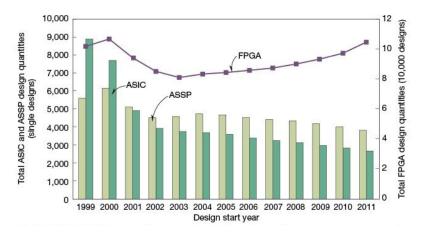

Regardless, because of the inflexible limitations of ASICs, their hold on the hardware-design market is diminishing. Conversely, reconfigurable computing and FPGA's use are flourishing because of their flexibility, as seen in Figure 3.1. Thus, reconfigurable computing is an appropriate approach to deal with the defined problem, without the disadvantages of ASICs.

Figure 3.1: ASIC vs FPGA Market - Market trends show diminished implementation in ASICs and growing demand for FPGA systems [32].

## 3.3 Reconfigurable computing background

Multiple implementation solutions have addressed the performance and cost issue. These solutions provided alternative hardware-based benefits where efficiency, speed, power consumption, system cost, throughput, or other units of interest in particular applications and systems are concerned.

Recent years have seen a rise in Systems-on-Chip (SoC) [33, 34, 35], Hardware/-Software Co-Design [18, 36, 37], Hardware Accelerators [17, 38, 39, 40] and Reconfigurable Computing [41, 42, 43, 44]. Each of these solutions are a response to inadequate hardware mapping for efficiency to available computer infrastructures. This inadequacy generally stems from the not-surprising fact that domain-specific problems that demand high computational power can perform much better on specialized hardware.

As we established, ASICs are not the most appropriate platform for implementation, and alternative solutions to ASICs include the aforementioned ones. Systems-on-Chip have tightly-coupled microcontrollers and memory among other interface components. This design improves the functionality of the chip by adding peripherals. The SoC peripherals act as common extensions to a variety of applications like counters, timers, and digital and analog functions. Hardware/Software Co-Design attempts to capture this added computational flexibility not only in SoC, but also in programmable and configurable processors. If these processors have a configurable fabric like that of a PLD or FPGA attached to them, then it would be a common option to add an application-specific hardware accelerators to boost performance. These hardware accelerators usually provide condensed multi-cycle computations for problems like digital signal processing, matrix operations, and fused multiplication/addition, and are loosely coupled with the processor itself.

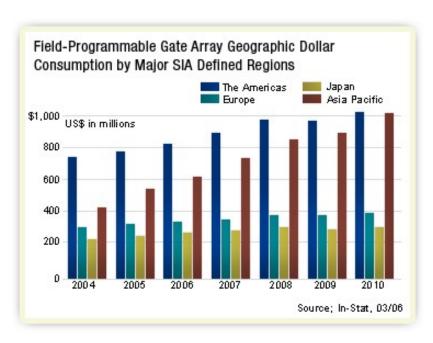

The last alternative is reconfigurable computing. While not new, this technology is still in its adolescent stages, trying to establish an identity which helps define the paradigm shift into programmable hardware. Researchers in both academia and industry have addressed the possibilities and limitations of reconfigurable computing, creating systems which make use of its flexibility, reusability and programmability. These systems can then provide optimizations, speedups, and increased performance by allowing the parallel execution of data in reconfigurable fabric. This increased interest in reconfigurable systems explains the growth that FPGAs have had for the past 10 years. Its importance can also be seen in the growing market for FPGA-based solutions shown in Figure 3.2.

Figure 3.2: FPGA Dollar Consumption - FPGA market history and forecast [45].

The rise of available technologies to support reconfigurable computing enabled researchers to tackle the demands of higher computational power in a variety of methods, which we discuss next.

### 3.4 Types of reconfigurable computing

Reconfigurable computing allows several configurations that adapt to different computational environments. There are two main types of data processing in reconfigurable computing: Reconfigurable architectures and soft-core processors.

#### 3.4.1 Reconfigurable architectures

Several reconfigurable architectures exist, the most prevalent being FPGAs. These architectures vary in their composition, with the three most important characteristics of reconfigurable architectures being granularity, structure, and reconfigurability.

#### 3.4.1.1 Granularity

Granularity, the datapath width of the architecture, determines the number and size of the architecture's Processing Elements (PEs). Low levels of granularity are called fine-grained, while larger are coarse-grained. Granularities for these architectures vary between 1, 4, 8, 16 and 32 bits. Fine-grained architectures are the most flexible, allowing bit-routing capabilities, while coarse-grained ones provide area-efficiency for regular multi-bit datapaths.

#### **3.4.1.2** Structure

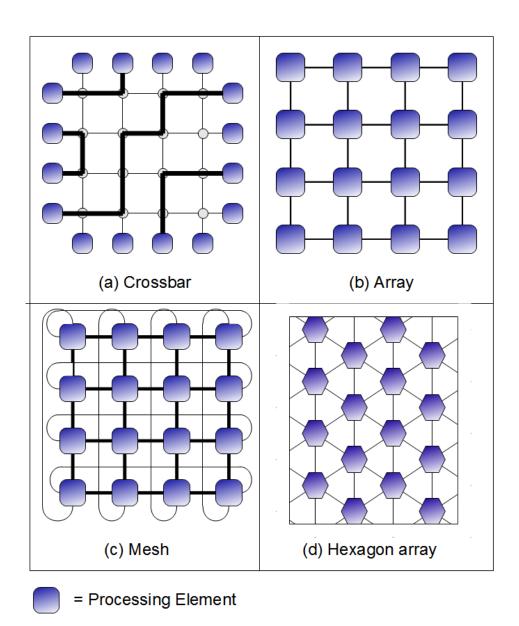

Structure, the positioning and inter-communication of the architecture's PEs, establishes the channels necessary for communication among PEs. A common practice for hardware processing is trading one fast-clocked large CPU, for a number of lower-clocked and more efficient PEs [46]. The multiple PEs are then structured to encourage nearest-neighbor links, increasing their communication bandwidth. Routing resources are implemented in the reconfiguration fabric and used according to these links. Figure 3.3 shows some of the structures that reconfigurable architectures have taken.

## **Reconfigurable Architecture Structures**

**Figure 3.3: Regular Reconfigurable Architectures** - Boxes represent processing elements, links are represented by lines. a) Crossbar allows for dynamic paths between PEs b) Arrays are static links c) Meshes provide circular struture d) Hexagon arrays (like Chess [47]) allow links with 6 neighbors.

Once the structure is selected, the architectures can then reconfigure PEs functionality and the communication links between PEs to achieve a specific task. Depending on the granularity used, they can be labeled in particular ways. To help clarify the loosely used terminology for "reconfigurable architectures" and other terms used in this proposal, we use the nomenclature proposed by morphware.net (Figure 3.4), which disambiguates labels used in our research area.

|                              | T.C                                 | econfigurable Computing                 | ADDITION OF THE PROPERTY OF TH | I comment of the comm |

|------------------------------|-------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Platform                     |                                     |                                         | Program Source<br>running on it                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Machine<br>Paradigm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Hardware                     |                                     |                                         | (not programmable)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| e)                           | Fine-grain                          | rGA (FPGA)                              | Configuero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Morphware                    |                                     | rDPU, rDPA                              | Configware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Anti-machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Worphware                    | Coarse-grain                        | Reconfigurable Data<br>Stream Processor | Flowware and<br>Configware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |