#### System Synthesis from a Monadic Functional Language

By

#### Garrin Kimmell

Submitted to the graduate degree program in Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas School of Engineering in partial fulfillment of the requirements for the degree of

### Doctor of Philosophy

|                   | Perry Alexander, Chairperson |

|-------------------|------------------------------|

|                   | Andy Gill                    |

| Committee members |                              |

| Committee members | William Harrison             |

|                   | Craig Huneke                 |

|                   | Gary Minden                  |

|                   |                              |

| Date defended:    |                              |

| The Dissertation Committee for Garrin Kimmell certifies          |

|------------------------------------------------------------------|

| that this is the approved version of the following dissertation: |

|                                                                  |

| System Synthesis from a Monadic Functional Language |  |

|-----------------------------------------------------|--|

|-----------------------------------------------------|--|

| Committee.     |                              |

|----------------|------------------------------|

|                |                              |

| -              |                              |

|                | Perry Alexander, Chairperson |

|                |                              |

| -              | Andy Gill                    |

|                |                              |

| -              | William Harrison             |

|                |                              |

|                | Craig Huneke                 |

|                |                              |

|                | Gary Minden                  |

|                |                              |

| <b>.</b>       |                              |

| Date approved: |                              |

|                |                              |

#### **Abstract**

## SYSTEM SYNTHESIS FROM A MONADIC **FUNCTIONAL LANGUAGE**

Garrin Kimmell

The University of Kansas.

Advisor: Perry Alexander

December 2008.

Embedded systems typically combine a mixture of heterogeneous components, some that are software executing on general purpose CPUs, some that are off-the-shelf hardware components, and some that are application specific circuitry. A major challenge when designing and implementing such systems is the dissimilar models of computation exhibited by hardware and software targets. To successfully navigate this challenge, components must be implemented in a way that does not unnecessarily bias the implementation towards either computational model, allowing the components to be retargeted as application requirements change.

This dissertation presents an approach to this problem using a functional programming language extended with monadic imperative and concurrency effects. We argue that these language features allow components to be implemented and compiled to either hardware or software targets. To demonstrate this claim, we detail the design of such a language, Oread. Moreover, we describe the compilation of Oread to both hardware, via VHDL, and software, via C. Using these compilation techniques, we describe the development of a digital processing component in Oread and the integration of that component into a larger system.

3

### Acknowledgments

My appreciation goes to my advisor, Dr. Perry Alexander, who has served me well by providing both the guidance to see this dissertation to completion and the freedom to pursue many paths along the way. His commitment to his students, both in the classroom and in the research lab, serve as model which I will use throughout my life.

The members of my committee, Andy Gill, Bill Harrison, Craig Huneke, and Gary Minden, along with Perry Alexander, deserve thanks for their valuable suggestions for this disseration. Many thanks go to Mr. Ed Komp, who is always eager to listen to any ideas I may have, but always questioning those ideas.

The systems level design group have been a pleasure to work with and have continually made going to work every day something to look forward to. The list of members both current and past has grown considerably in the time I have been working in the lab, but all deserve my gratitude: Cindy, Brandon, Murthy, Kalpesh, Justin, Jesse, Mark, Nick, Phil, and Megan. Special thanks go to Nick Frisby, Wesley Peck, and Jason Agron.

My path through graduate school would have been much shorter if I had not been surrounded by people who made the time so enjoyable: Andy, Halle, Rustin, Howard, Emily, Janet and Mirco, Manoj, and the many that I have played kickball and softball with.

I thank the KU EECS department and ITTC for their financial support during the writing of this dissertation. Thanks to Dr. Peter Ashenden and the University of Adelaide, Australia, provided the opportunity to visit and study.

Finally, I wish to thank my family, including my parents, my brother Rustin, and my wife Morgan, who provided love and support without which this dissertation would not be possible.

for mosho

## **Contents**

| Al | bstrac | et en   | 3  |

|----|--------|---------------------------------------------|----|

| A  | cknow  | vledgments                                  | 4  |

| 1  | Intr   | oduction                                    | 13 |

|    | 1.1    | Hardware and Software Computational Models  | 14 |

|    | 1.2    | Design Process Ramifications                | 19 |

|    | 1.3    | Improving the Design Process                | 24 |

|    | 1.4    | Motivation: Software defined radio          | 27 |

|    | 1.5    | Overview of related work                    | 29 |

|    | 1.6    | Dissertation contributions and organization | 32 |

| 2  | Ore    | ad: A language for mixed-target synthesis   | 35 |

|    | 2.1    | Oread Design Motivation                     | 37 |

|    |        | 2.1.1 A Functional Language                 | 37 |

|    |        | 2.1.2 Monadic encapsulation of effects      | 42 |

|    |        | 2.1.3 A monadic concurrency architecture    | 43 |

|    | 2.2    | Oread semantics                             | 48 |

|    |        | 2.2.1 Monads                                | 48 |

|    |        | 2.2.2 Oread Semantics                       | 57 |

|   | 2.3  | Summary                                   | 58  |

|---|------|-------------------------------------------|-----|

| 3 | Con  | npiling Oread to Hardware                 | 63  |

|   | 3.1  | Hardware Control Protocol                 | 64  |

|   | 3.2  | Primitive VHDL components                 | 70  |

|   |      | 3.2.1 Combinational Data Components       | 71  |

|   |      | 3.2.2 Combinational Control Components    | 84  |

|   |      | 3.2.3 Sequential Components               | 87  |

|   | 3.3  | Summary                                   | 100 |

| 4 | Prog | gram Transformation and System Generation | 102 |

|   | 4.1  | Oread program Transformation              | 102 |

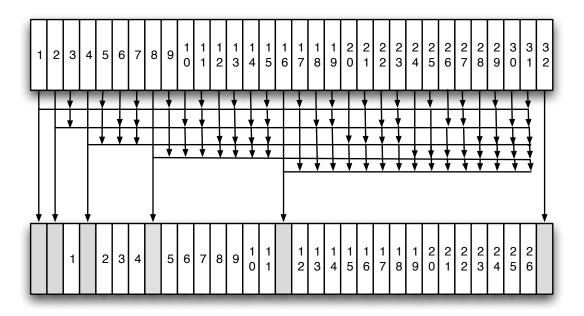

|   |      | 4.1.1 Defunctionalization                 |     |

|   |      | 4.1.2 Static Data Allocation              |     |

|   |      | 4.1.3 Static Monadic Instance Resolution  | 117 |

|   | 4.2  | System Generation                         | 124 |

|   | 4.3  | Summary                                   | 128 |

| 5 | Con  | apiling Oread to Software                 | 129 |

|   | 5.1  | Oread Software Data Model                 | 130 |

|   | 5.2  | Oread Compilation Schemes                 | 132 |

|   |      | 5.2.1 Compiling Algebraic Data Types      | 134 |

|   |      | 5.2.2 Compiling Function Declarations     | 135 |

|   |      | 5.2.3 Compiling Expressions               | 136 |

|   |      | 5.2.4 Compiling Monadic Forms             | 141 |

|   | 5.3  | Oread Concurrency Model Compilation       | 143 |

|   | 5.4  | Summary                                   | 146 |

| 6  | Cas   | e Study: Software Defined Radio | 149 |

|----|-------|---------------------------------|-----|

|    | 6.1   | Hamming Encoding                | 151 |

|    | 6.2   | FIFO-style Message Service      | 157 |

|    | 6.3   | Summary                         | 162 |

| 7  | Con   | clusions and Future Work        | 165 |

|    | 7.1   | Future Work                     | 168 |

| Tł | ie Or | ead external representation     | 175 |

# **List of Figures**

| 2.1  | Example system architecture                | 45 |

|------|--------------------------------------------|----|

| 2.2  | React monad                                | 53 |

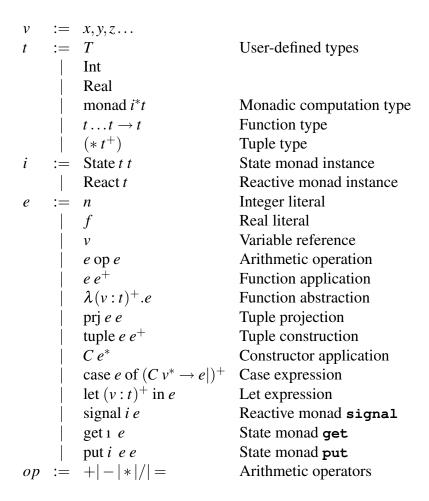

| 2.3  | Oread core syntax                          | 57 |

| 2.4  | Oread static semantics                     | 59 |

| 2.5  | Evaluation semantics of Oread              | 60 |

| 2.6  | Evaluation semantics of monadic constructs | 61 |

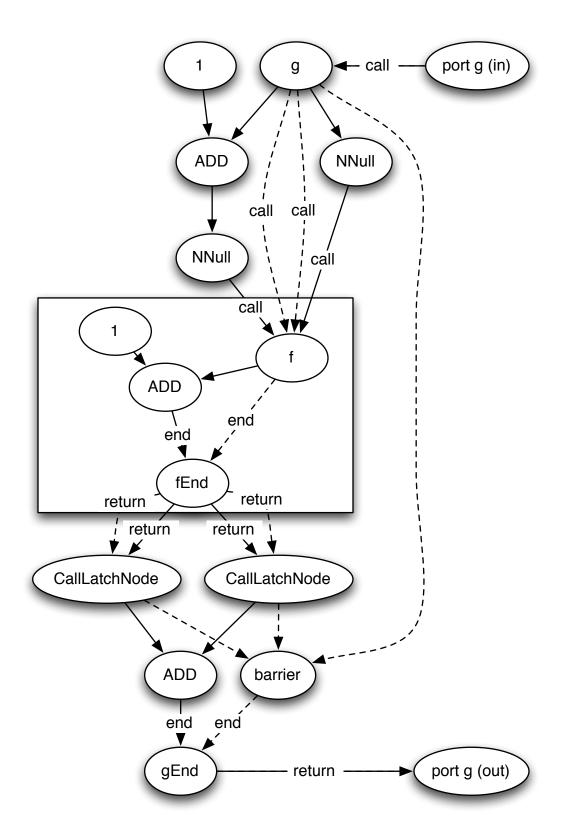

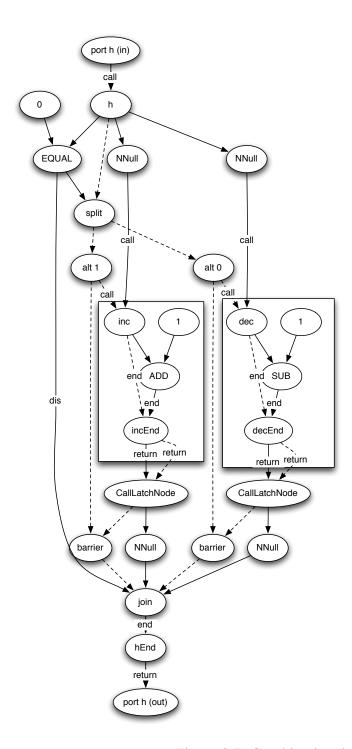

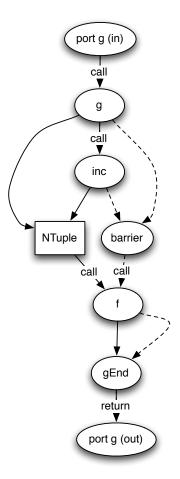

| 3.1  | Control and data flow graph                | 66 |

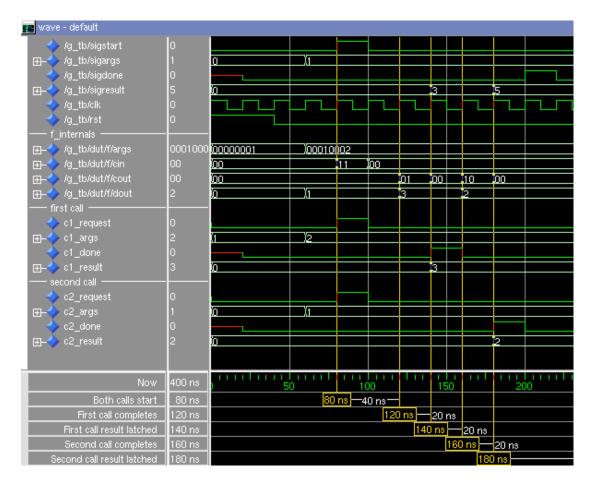

| 3.2  | Ready protocol example                     | 67 |

| 3.3  | Call latching example                      | 68 |

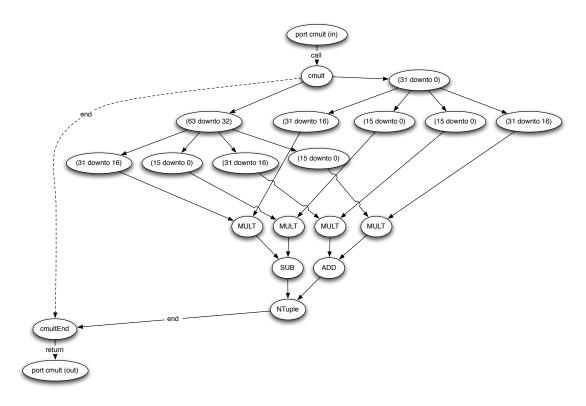

| 3.4  | Complex Multiplication (Simple)            | 76 |

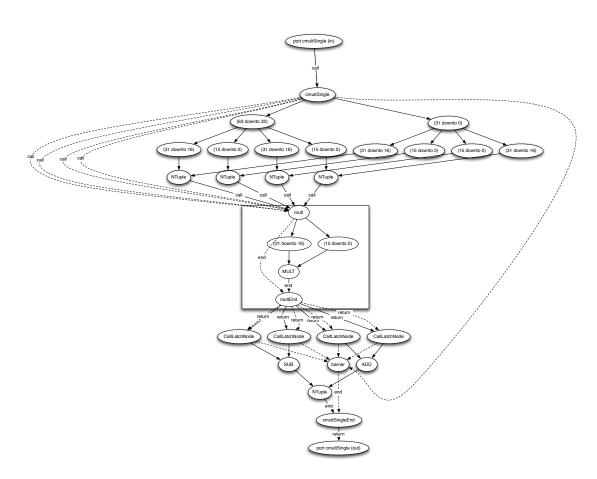

| 3.5  | Complex Multiplication (Collapsed)         | 77 |

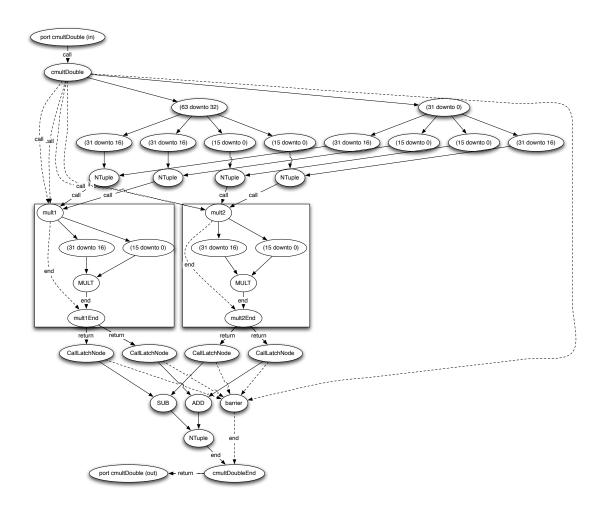

| 3.6  | Complex Multiplication (Balanced)          | 79 |

| 3.7  | Combinational Control                      | 86 |

| 3.8  | Barrier insertion example                  | 88 |

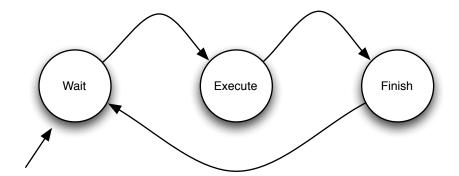

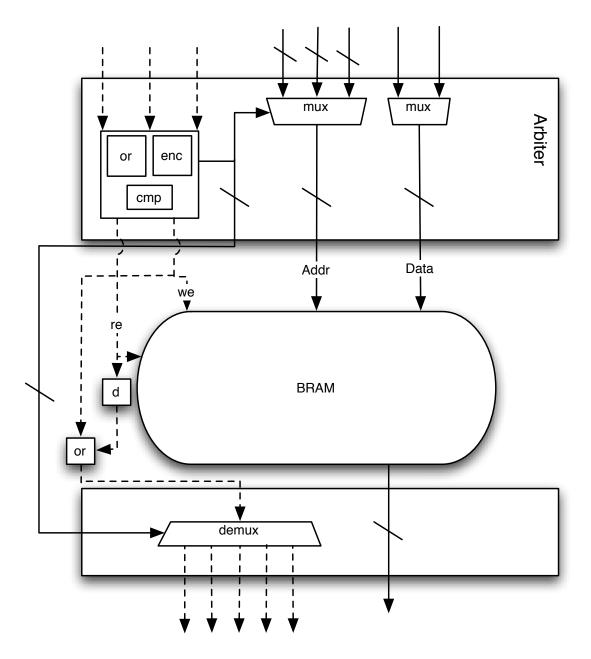

| 3.9  | Shared Block State Machine                 | 90 |

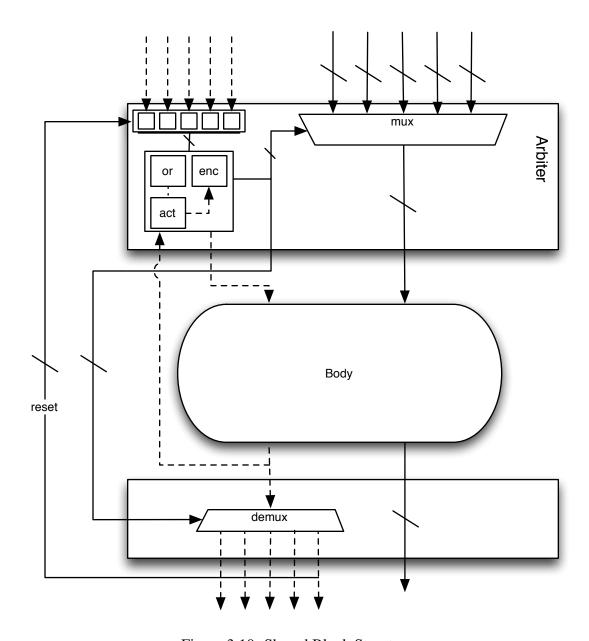

| 3.10 | Shared Block Structure                     | 92 |

| 3.11 | Jump Block Structure                       | 95 |

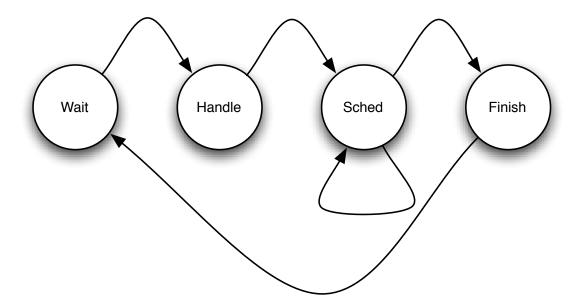

| 3.12 | MemBlock Structure                         | 96 |

| 3.13 | ServiceBlock State Machine                 | 98 |

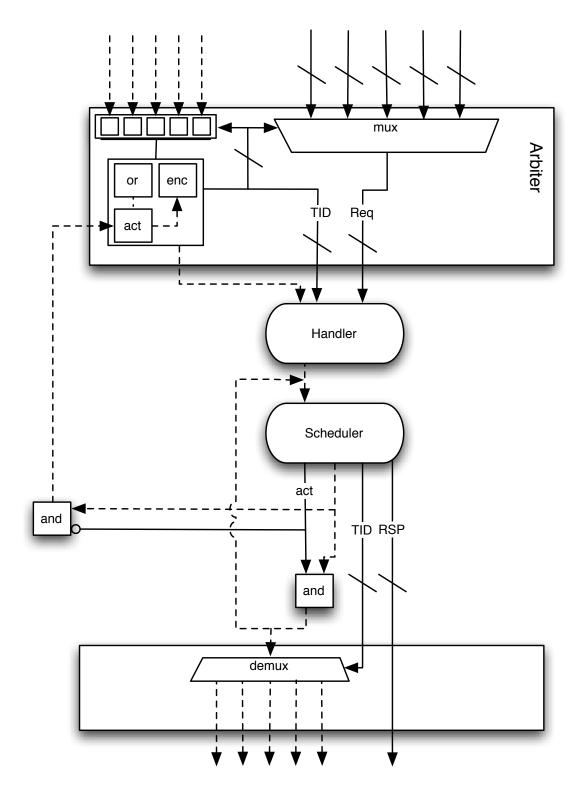

| 3.14 | ServiceBlock Structure                         |

|------|------------------------------------------------|

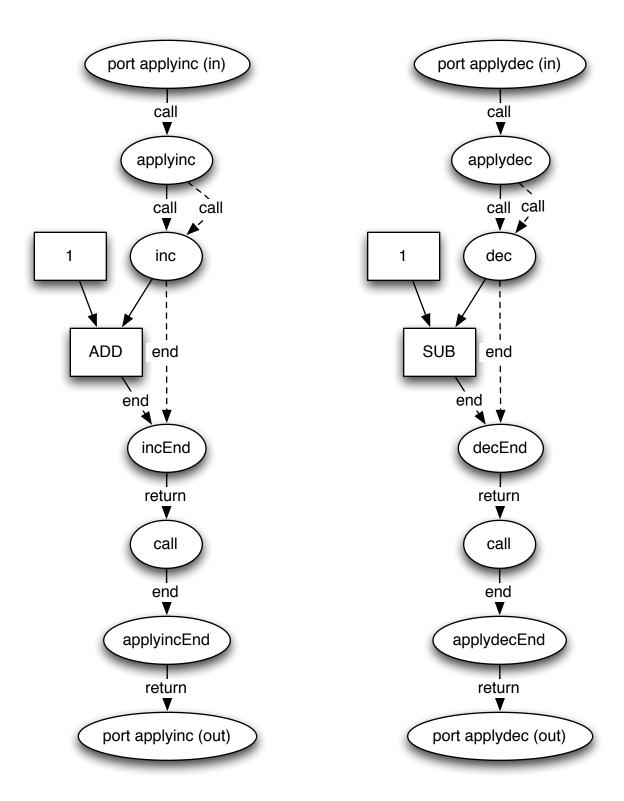

| 4.1  | applyinc and applydec                          |

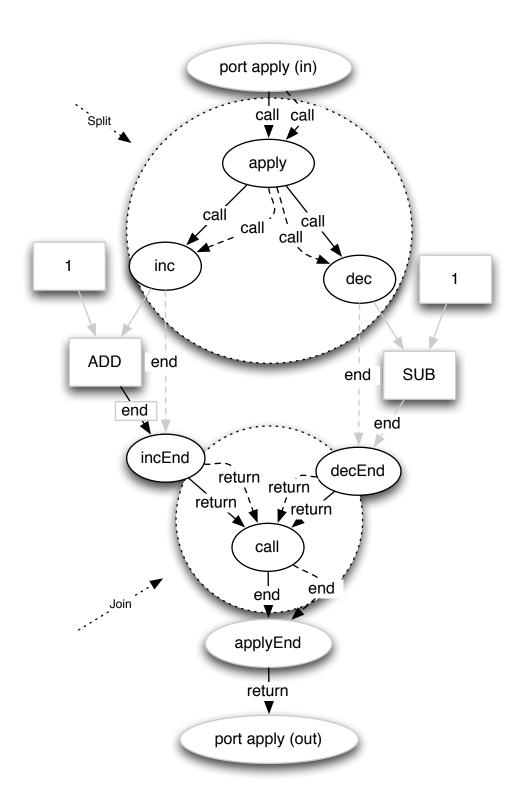

| 4.2  | Hypothetical apply graph                       |

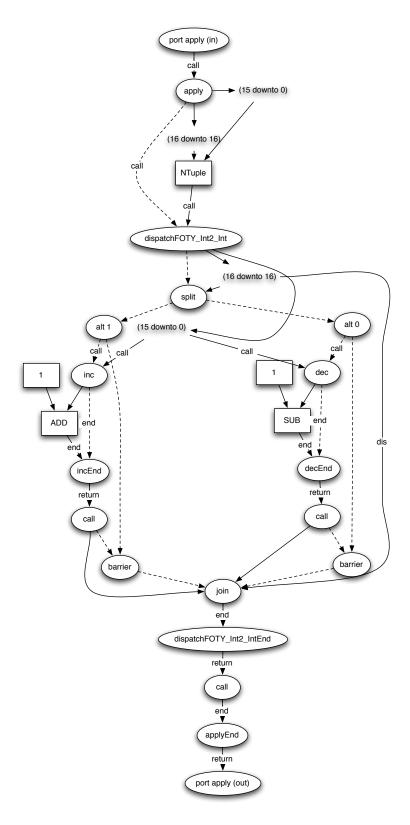

| 4.3  | Defunctionalized apply                         |

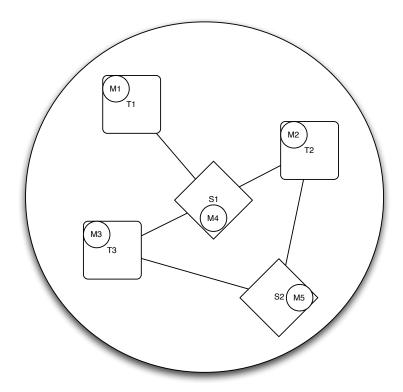

| 4.4  | System Configuration                           |

| 4.5  | System Structure                               |

| 5.1  | Constructor Application Template               |

| 5.2  | Function Declaration Template                  |

| 5.3  | Function Application Template                  |

| 5.4  | Tuple Template                                 |

| 5.5  | Projection Template                            |

| 5.6  | Case Template                                  |

| 5.7  | Service Structure                              |

| 5.8  | Run-time signal function                       |

| 6.1  | SDR configuration                              |

| 6.2  | Hamming encoding scheme                        |

| 6.3  | Residualized Hamming encoder for 16-bit words  |

| 6.4  | 16-bit Hamming encoder C compilation output    |

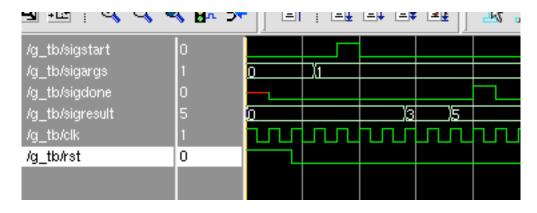

| 6.5  | 16-bit Hamming encoder VHDL compilation output |

| 6.6  | FIFO handler functions                         |

## **List of Tables**

| 3.1 | Oread primitive VHDL components                |

|-----|------------------------------------------------|

| 5.1 | Oread to C data mapping                        |

| 1   | Oread external representation lexical elements |

| 2   | Oread external representation grammar          |

| 3   | Configuration grammar                          |

## Chapter 1

#### Introduction

Embedded systems typically combine a mixture of heterogeneous components, some that are software executing on general-purpose CPUs, some that are off-the-self hardware components, and some that are application-specific circuitry. The decomposition of the system into individual components and the mapping of those components into an implementation target, or fabric, is motivated by a variety of both functional requirements and performance requirements. The challenge of systems engineering is to integrate the multitude of different requirements into a complete system that respects those requirements and to preserve those requirements as they are refined into executable implementations. As with most tasks, the role of abstraction is central to successfully navigating this challenge: choose a requirements model that is too abstract, and the model loses its predictive power; choose a model that is too concrete and lose the ability to adapt the model to changing requirements or new problems.

This dissertation focuses on the aspect of system engineering related to the refinement of high-level functional requirements to executable implementations. This problem goes beyond simply compiling a program to software or alternatively, synthesize to hardware. When considered individually, both software compilation and hardware synthesis represent amazing successes in the computer science research literature. When

taken together – in single-source systems which can be refined to both hardware or software systems – the record is positive, but certainly more mixed. The challenges of mixed-target compilation is rooted in the fundamentally different models of computation exhibited by different targets. Attempts to take an implementation designed with one model in mind and map it into another model tend to introduce inefficiencies and unnecessary implementation rigidity. To be successful, it is crucial to design from the beginning with the intention of targeting differing fabrics.

## 1.1 Hardware and Software Computational Models

The root challenge in designing and integrating heterogeneous – mixed hardware and software – systems is the the fundamental difference in the computational models used to construct those systems. Distilled to its core, this difference is that software systems are implemented as a series of sequential steps over a relatively small fixed set of high-level computational blocks, while hardware systems are implemented by arranging an adaptable set of concurrently-operating, low-level components.

A CPU generally contains a single ALU and control unit.<sup>2</sup> The ALU provides a variety of high-level arithmetic and logic data processing functions, such as adders, multipliers. There may be dedicated units for different data representations, so that integer and floating-point arithmetic operations are handled by different components. Nevertheless, these components operate on fixed-size data representations, usually the native word size of the processor for integral data and the IEEE standard data size for floating point operations. The control unit provides the mechanism for coordinating

<sup>&</sup>lt;sup>1</sup>We use the terms compilation and synthesis interchangeably throughout the thesis. In situations where we wish to distinguish between the two, we will make the distinction explicit.

<sup>&</sup>lt;sup>2</sup>This characterization is less apt for modern super-scalar architectures which may have multiple functional units. These architectures came about as an attempt to avoid some of the limitations inherent in the von Neumann computational model. However, the discussion below remains valid.

the operation of data processing units as a series of state transformations on data stored locally in registers (for fast access) and in global memory (for longer-term storage).

The intent of the von Neumann architecture exhibited by general purpose CPUs is to provide a common abstraction for implementing systems. In many ways, this intent has been realized to great success, as evidenced by the relative ease in which software can be ported between different instruction set architectures which subscribe to this computational model. This is especially true when the software is written in a imperative language such as C that abstracts many details of the processor and obviates the need for the programmer to operate at the level of the ISA.

The architecture of a standard CPU simplifies the construction of software systems and eases the migration of systems between different CPU families, yet this architecture has significant drawbacks in embedded applications. The ISA presents a one-size-fits-all model for constructing systems. Consider an application consisting of a large number of independent addition operations. Because of the limited number of adders in the CPU, these operations must be serialized. Whether the application ever uses (for example) an integer multiplication operation or any floating-point arithmetic is irrelevant; the transistors needed to implement those unused operations in the CPU are dedicated to that task and cannot be re-purposed. If the application manipulates data of a non-standard size, the data must be adapted to the CPU, resulting in inefficiencies both in the computation needed to perform the data transformation as well in the silicon overhead for the component being larger than necessary.

The above inefficiencies are present when performing the same operations on collections of data (SIMD) the limitations of a general-purpose CPU become even more pronounced when performing *different* operations upon data (MIMD). The most common way to implement this sort of computation on a CPU uses threads. Each thread has its own control and data state, and different threads may be executing logically differ-

ent programs. The CPU time-multiplexes the various threads by executing each thread for a small amount of time, then saving the thread's state at a safe point and restore a different thread's saved state.

Communication between the threads is performed via manipulations on a shared global store. Manipulating the global state is tricky, as it requires every externally-visible manipulation to be atomic. Common thread libraries, such as POSIX threads (IEE 2004) offer a variety of concurrency-control primitives for insuring that inter-thread communication is safe. However, proper use of those primitives is notoriously error-prone.

In many ways, the computational model used for constructing hardware implementations of components is the inverse of the software model. Rather than a fixed set of high-level functional components, a hardware fabric provides many orders of magnitude (perhaps millions) more low-level *gates*, each of which are capable of performing a single 2-input boolean operation. Modern technology has eclipsed this characterization to a degree. For example, gates in modern FPGA technology are implemented using look-up tables (LUTs) which generally implement 4- or 6-input boolean circuits. Nevertheless, these advances do not nullify the following analysis of the hardware model of computation.

In the software model, control is expressed either implicitly in the sequencing of instructions, or explicitly as branching and jump instructions that direct the operation of the CPU control unit. In the hardware computational model, the distinction between control is less well separated. Registers are sequential elements of state that store values at regular intervals dictated by a global clock. As with the components of a CPU, the circuitry used to implement operations is present in the fabric whether the instantaneous control requires the output of those operations or not. Control is manipulated by selecting, using a multiplexer circuit, the outputs of various combinational circuits for

input to a sequential register. Modern synthesis tools can minimize the number of idle combinational circuits by automatically introducing additional control logic, allowing the same circuit to be reused for mutually exclusive control paths.

This gate-level computational model precludes several of the drawbacks of the software model. For example, there is no need to artificially sequentialize data-independent operations due to a limited fixed number of computational resources – if an application demands n adders, then the circuit can include exactly n adders. Equally important, the fine control provided by the low-level of abstraction of the hardware model allows unneeded resources to be omitted in the implementation. The circuit implementing an application requiring no floating point operations will include no floating point components.

The gate-level computational model provides maximum design control for implementing components, yet the level of abstraction is so low as that the design task becomes intractable as the application scales in size. For this reason, hardware designers will often use a *register transfer level* (RTL) computational model for constructing components. In RTL, a component is defined as a series of state elements (mapped to registers in the fabric) and a series of combinational transfer equations. A register's value in the next state is defined as the result of a transfer equation applied to the value of the register(s) in the the current state.

The distinction between current and next state is dictated by the register, which is in turn driven by a system clock. The clocked nature of RTL design introduces a complicating factor into the construction of hardware components using this model. For the value at the input for a register to be valid at a clock edge, the transfer equation implemented as a combinational circuit from the register's output, must meet timing

<sup>&</sup>lt;sup>3</sup>This is an idealized view of hardware fabrics. In practice, the actual number of gates is finite, and it may be necessary to limit the number of duplicated resources to fit space constraints by introducing additional control logic.

constraints, in that the propagation delay through the combinational circuit must be less than the clock period. In other words, the propagation delay for the transfer equations dictates the clock period.

The clock period is determined by the *longest* combinational path for a register whose input is dictated by a collection of transfer equations. It makes little sense to optimize the timing for one combinational circuit if there is another circuit with worse timing; consequently, the designer must take into account timing as a *global* performance property. There are local approaches to reducing circuit propagation delay (e.g. splitting a combinational circuit by introducing pipeline registers) but these approaches have global ramifications (e.g. the need to insert additional delay registers in sibling circuits).

The concurrency abstractions of a hardware computational model is nearly the inverse of that in software. Whereas in software, concurrency is achieved by multiplexing several threads of control on a single CPU, in hardware concurrency permeates the model. In software, the main programmer effort is in simulating concurrency on an essentially non-concurrent fabric in hardware concurrency is primitive (all elements in the fabric are always executing concurrently) and the challenge is imposing sequentialization of control.

The standard way to impose sequential control within a hardware circuit is using clocked registers. However, introducing a register to buffer data transfer between concurrently operating circuits has the unfortunate consequence that the timing behavior for each component is externalized, and every component must satisfy the same timing requirements. This is analogous to the "leaking" of timing behavior of individual combinational circuits within a component into the other combinational circuits where the performance of every circuit is bounded by the timing of the *worst* performing circuit.

The culprit for the globalization of timing requirements is the clocked nature of the registers used for inter-component communication. One solution to this problem is to introduce multiple clock *domains*, so that each component is operating at its own clock frequency. While this solution simplifies the implementation of circuits *within* a component, it complicates the interactions *between* components. Instead of a simple global clock, it is necessary to include a more sophisticated control protocol at the junction between clock domains.

## **1.2 Design Process Ramifications**

The differences between hardware and software implementations of components is rooted in the disparity between the abstractions used to implement those components. Software presents an exceptionally regular architecture, with the downside that there are inefficiencies introduced due to the fixed set of computational resources and the impedance mismatch that results from exploiting concurrency on a fundamentally sequential abstraction. On the other hand, while hardware offers much more design flexibility by giving the implementer control over the number and size of computational resources and concurrency "for free", the model of computation is at such a low level that it requires the implementer to repeatedly construct many abstractions offered by the software model of computation. At the same time, the hardware level of abstraction emphasizes non-functional performance requirements, such as timing, which are hidden in the software computational model.

Given these differences it is instructive to examine the consequences of the properties of the different models of computation within the larger scope of the system engineering process. This includes the secondary influences of the abstractions upon the various phases of the engineering life cycle, including design, deployment, and

maintenance. Moreover, while there may be engineering practices that are naturally induced by the model of computation of the underlying target fabric, these practices are often at odds when employed when constructing a heterogeneous system composed of components in mixed target fabrics.

**Design impacts** The system design process begins with the collection of functional and performance requirements. The functional requirements define the correct computational behavior of the system, while the performance requirements define constraints – cost, size, security, etc – that must be satisfied while performing the computation. The functional requirements are fabric-agnostic, while the performance requirements are abstractions of the fabrics the function will be implemented in.

The next task in the system design process is a decomposition of the functional requirements into a architecture that that places various portions of the functionality of the system into different components, maps each of those components into a target fabric, and defines the communication interfaces between the components. The decomposition task is advised by the performance requirements, as the non-functional behavior exhibited by a component mapped to a particular technology must satisfy the constraints not only of that component, but of the system as a whole.

A system architect will use gross estimates and heuristics when performing the decomposition. This is because the actual performance of the system may vary widely depending on the exact implementation of a component, and the number of implementations satisfying a particular set of functional requirements may also vary widely. Consequently, it is the task of the system architect to constantly re-evaluate the suitability of the system decomposition towards the performance requirements as the functional requirements are refined to implementations. If during this refinement it is discovered that the system decomposition will result in a system that violates performance con-

straints, it is necessary to re-architect the system to a different configuration which can satisfy the performance constraints. This process may repeat several times.

Ideally, changing a system decomposition by moving a component from one target fabric to another should be possible without abandoning the implementation effort expended to arrive at the decision to reconfigure the system architecture. Sadly, this is rarely the case, due to the contrasting models of computation used in the refinement of the components. Once a target fabric has be identified for a component, it is likely that the abstraction used in the implementation of that component will make it difficult to transfer that implementation to a different fabric.

This difficulty is especially pronounced in the case of component mapped to hard-ware components. Because of the tight coupling of functional behavior and non-functional behavior (such as timing) it is often difficult to migrate a component from one target fabric to another *even if the computational model is the same*. Consider, for example, the gate-level model of a circuit mapped to FPGA. As FPGA manufacturing technology advances, the basic building blocks of the FPGA fabric continues to support increasingly-complex boolean circuits. A gate-level design mapped to an older technology may not be easily adapted to utilize new FPGA features, simply because the design is too closely coupled to the implementation technology. This yields serious difficulties in the maintenance life-cycle of the system as existing designs are adapted to new technology.

The initial system decomposition is performed with only gross estimates of the performance properties of the functional requirements mapped to an implementation fabrics. These estimates are honed as the functional requirements are refined to implementations. Because engineering effort (or conversely, the cost to correct errors) increases dramatically – often by orders of magnitude – as the system moves from the design to implementation and then to the validation stages, it is important to detect

and correct errors as early as possible in the process. Not only is desirable to be able to re-target implementation artifacts, it is also of major advantage to move validation as early as possible in the engineering process. However, in heterogeneous system design, this is complicated by the often informal nature of the computational models utilized, the informal understanding of the interactions between the different computational models, and the interactions between non-functional performance properties of the computational models.

Deployment and maintenance considerations Software components can be updated "in the field". Replacing a software component with an augmented version may be as simple as restarting a program or rebooting the system. Components implemented in hardware are rarely so easy to update, as the substrate *is* the component. To update such a component may require removing and replacing the physical circuit, an undertaking that will often require removing the component from the deployment environment. Consequently, bug fixes and feature enhancements for software components entail considerable less expense than the same modifications for hardware components.

The ease with which software can be modified at run-time forces the system designer consider the implications of this malleability and adjust the system design accordingly to adapt. For example, because software can be modified at run time, it may be necessary to make additional security assurances. Not only is it sufficient to guarantee that the system that is deployed satisfies security requirements, but it is also necessary to ensure that the system that is executing continues to be the system that was deployed, and not some altered version that may violate those security requirements. This typically requires some degree of run-time monitoring or measurement, adding additional complexity and execution overhead to the system. Moreover, it remains necessary to ensure that the component providing run-time integrity assurance is itself not

compromised. On the other hand, the rigidity of hardware components make them less susceptible to attacks where the deployed component is replaced with a compromised component.

Long after the design and deployment of a system, the relative adaptability of the software vs. hardware models of computation continues to influence the maintenance of the system, even after the components have stabilized and are no longer actively being updated with bug fixes. As the system ages, it becomes necessary to replace components simply because of the physical wear-and-tear on the physical hardware (regardless of whether the hardware is a CPU or custom circuitry).

Historically, technology has increased in speed and storage at an exponential rate. As embedded systems are often deployed in applications where reliability and stability are of high importance, it may be years or decades between the initial deployment of system and the need to replace a physical element of the system. Due to the long delay between the design and servicing, the technology used for the components in the initial design may not be available for purchase, or may be so expensive that it is more economical to redesign the system for new technology. For example, a system which when designed required a number of CPUs (for executing software components) and ASIC (hardware components) may be possible to implement using a single modern CPU with a single hardware interface to legacy elements of the system.

The challenges when attempting to use newer technology to implement legacy components are similar to the challenges used in the initial design process, except that working implementation are already available. Because the existing implementation has been tested and deployed, it is of great benefit to reuse those components. For software components, this involves adapting the existing programs to the ISA of the new technology and executing multiple components on the same CPU. This is more complicated when adapting hardware components. To migrate a hardware implemen-

tation to software requires a change of model of computation. Moreover, the hardware implementation may rely on a variety of non-functional performance properties of the original target fabric to insure correct functional behavior. It is likely that these performance assumptions in the original implementation may not be documented, and even less likely that the new technology will exhibit the same properties. Therefore, it is necessary to perform a great deal of post-implementation validation to insure that the new system design respects the performance constraints of the original design and implementation.

## **1.3** Improving the Design Process

Building hardware and software systems requires modeling, implementing, and integrating components in disparate models of computation. The gap between the hardware and software models of computation makes it difficult to move components between models of computation. Software implementations introduce run-time inefficiencies and constrain concurrency, yet increase the design and maintenance flexibility. Hardware implementations allow a implementer maximum control of computational resources and concurrency, at the cost of increased prominence of non-functional performance properties in the component design and reduced maintenance flexibility.

Improving the process of developing heterogeneous systems requires the identification of a mediating model of computation which satisfies the following desiderata:

- The ability to quickly re-target implementations to fabrics with different models of computation.

- The ability to take advantage of the computational resources of the fabric.

- The ability to define concurrent communication independently of the medium and irrespective of low-level performance considerations.

- The ability to predict performance properties of a computational artifact.

The thesis of this work is that a functional language, extended with monadic effects for imperative and message-passing based concurrency, is a suitable basis for constructing systems that will be synthesized to efficient hardware or software fabrics.

This thesis focuses on the synthesis of mixed-fabric systems in the context of embedded applications. While this is the motivating use case, it should not be seen to be a limited case. Many of the complications that embedded applications emphasize remain relevant in typical desktop applications. This is increasingly so as modern CPUs address the abundance of transistors not by making high-clocked processors, but by adding more CPUs on a single die. This is a response to the decreasing returns, at the CPU design level, yielded by addressing performance with faster and faster processors. This change is fundamental, as it shifts the computational model from the sequential von Neumann architecture with a central store for data and control (as a program) to a concurrent model where data and control are distributed throughout the system. From a historical perspective, this shift was first foretold by Backus over 30 years ago in his lecture about the 'von Neumann' bottleneck. Backus' response to the bottleneck was to use functional programming languages to escape the inherent difficulties in exploiting the new computational model.

The approach outlined in this thesis is tightly related to that advocated by Backus (1978), where a functional programming language was identified as an escape from the "von Neumann bottleneck". However, it goes beyond by highlighting the role of

concurrency in systems. Backus' FP was primarily concerned with the parallelization of common sub-elements in a data processing language – SIMD style processing.

In contrast, constructing MIMD – and concurrent applications in general – the primary challenge is in the coordination of the various processing elements. To address this problem, the thesis once again looks back over 30 years to the foundations of concurrent models of computation, Hoare's CSP (Hoare 1978) and Milner's CCS and  $\pi$ -calculus (Milner 1999). These models of computation for concurrency use message-passing as the primitive notion of concurrent computation. Processes are isolated computational units that operate independently until a interaction with the external world is needed. This interaction is accomplished by either sending or receiving a message along a channel. Because all actors in a concurrent system are modeled as processes, every send must have a matching receive from another process, and vice versa. If a process attempts to send (resp. receive) a message and there is not a matching receive (resp. send), the process will "block" until there is a match. Within this model, communication *is* coordination, with control being converted to data.

Backus' FP forms the "functional" core of the model advanced by the thesis, and Hoare and Milner's models of message-passing concurrency form the foundation of the concurrency model. The final piece of the thesis involves the use of *monads* to encapsulate computational effects, such as imperative (stateful) computation and reactive (message-passing) concurrency. Moggi identified monads (Moggi 1990, 1991) as a useful mathematical principle for structuring computational effects that allowed for higher levels of abstraction than operational models, while offering more composability than traditional denotational models (Stoy 1981). From a mathematical viewpoint, monads are algebraic structures and can be manipulated as such, much as Backus advocated an "algebra of programming" for reasoning about and manipulating functional programs.

In addition to offering formal reasoning capabilities, monadic specifications can be interpreted in a pure functional language, giving rise to executable specifications. Wadler(Wadler 1992, 1993) identified the suitability of monads for structuring programs – not just specifications – an observation that has been leveraged to great success in structuring computational effects in pure functional languages such as Haskell.

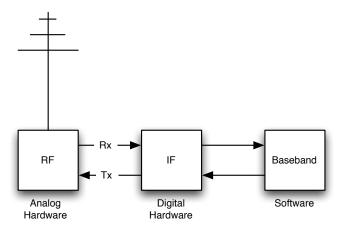

#### 1.4 Motivation: Software defined radio

The motivating application for this work is the software defined radio (SDR) domain. Software defined radios are an approach to constructing radio systems so that they can be reconfigured and adapted, perhaps on-the-fly, for new applications. Despite the name, a software defined radio isn't exclusively constructed of software components: often a SDR is built upon an existing platform that includes dedicated hardware for specific radio tasks, because the performance of a pure-software system cannot meet the processing demands of a radio application.

The design of a radio may vary depending on the characteristics of the deployment environment. For example an individual operating in the field, communicating with a handheld radio to a fixed central tower, will have vastly different performance constraints for power and size than the tower it is communicating with. The mobile device may need to sacrifice cost for power and speed, placing much of the functionality of the radio in custom hardware, while the central tower, with a dedicated power source, can use a software implementation of much of the radio. However, the two radios are using the same functionality to communicate, and it is desirable to be able to develop a single implementation that can be used both in the software and hardware components.

A second intended benefit of software defined radios is that a radio platform can be reconfigured for a variety of different waveforms as the environment demands. In this usage model, the software defined radio platform provides a computational basis for implementing a given waveform, and may include a variety of different computational elements, including general purpose CPUs, DSPs, and FPGAs (Minden et al. 2007). A component may be used in multiple different waveforms. However, the computational demands of the application may vary, and in one configuration a component may need to be implemented in hardware to satisfy performance requirements, while in a second waveform configuration the same component may be implemented in software, freeing hardware resources for a different component.

The SDR domain requires digital components to interface, at some point, with analog RF components. Analog hardware will have fixed performance requirements, such as power consumption and timing. The computational elements must respect those requirements. Moreover, an SDR is a discrete approximation of an analog waveform; the waveform may include continuous elements that are digitized and processed by the SDR components. It is critical that those elements respect the analog model of the waveform as well.

The final property of the SDR domain that exemplifies the challenges of developing heterogeneous systems is that the lifespan of a deployed SDR platform may be measured in decades, making it necessary to be able to adapt portions of the platform to new computational technology. However, this cost of deploying the platform based on new technology can be high, since the correct implementation of a waveform component can rely on low-level performance constraints, which are often not reflected in the implementation. The cost of not deploying new technology, however, may be greater as legacy parts may cost too much or may simply not be available. To successfully manage the lifespan of an SDR platform, it is necessary to model not only the component behavior but also the performance characteristics of the platform elements, easing the transition to new technology.

#### 1.5 Overview of related work

There is a large body of existing literature describing the use of functional programming languages and notations for describing hardware circuitry. Lava (Bjesse et al. 1998) and Hawk (Matthews et al. 1998) are two such examples. While these languages use a functional programming language to construct circuits, they maintain a distinction between the host language (Haskell, in the case of Lava and Hawk) and the object language, implemented as a library of data structures and combinators.

Embedding the hardware description language within a lazy functional language such as Haskell allows the developer of the language to leverage a great deal of the host language capabilities. Lava circuits are Haskell data that can be manipulated with Haskell functions. Moreover, Lava circuits can be given a variety of interpretations. This includes Haskell stream transformation functions, enabling a basic simulation capability. Other representations include a VHDL back-end, which allows Lava circuits to generate structural VHDL netlists, and as boolean forms to be used as input to SAT solvers for verification purposes.

The distinction between Haskell programs generating Lava circuits is similar to the static/dynamic stage distinction found in the partial evaluation (Jones 1996) and multistage programming languagesTaha (1999). However, Lava differs significantly with these systems in that the host language and the object language are different, while most work on multi-stage languages uses the same language for each stage.

A disadvantage of changing from Haskell to Lava between stages is that the Haskell abstractions cannot necessarily be mapped directly onto Lava abstractions. While Haskell is a full-fledged programming language, a Lava circuit is basically a structural representation of a circuit as a graph. Haskell idioms must be replicated as Lava library components, such as a multiplexer instead of a case expression for control flow.

Moreover, Haskell data abstractions are replaced with lower-level data structures, as Lava operates primarily on streams of boolean values representing bits. Composite data structures must be manually constructed as collections of individual bitstreams. Finally, some host-language idioms, such as function abstractions, are simply not present in Lava. As we demonstrate in chapter 3, functions in Oread provide a simply structuring mechanism for controlling resource usage.

VHDL (IEEE) and Verilog (IEE 1995) are the two dominant hardware description languages. Both languages offer similar capabilities for defining hardware, although VHDL traditionally has offered more extensive data abstraction capabilities, as it was originally designed as a specification language, rather than an implementation language. The languages use a discrete-event model of computation, where hardware signals are modeled as a ordered stream of events. Each event contains a specific timestamp, enabling the ordering. The close connection between the discrete event model of computation and the clocked nature of most hardware implementation fabrics has led to an emphasis on strict control of timing within a design. This thesis, in contrast argues that it is necessary to *de-emphasize* the role of timing in the construction of system, relying instead on an asynchronous control protocol for handling circuit coordination. Decoupling a component's functional behavior from its associated non-function properties (such as timing) allows a functional implementation to be more easily adapted to new implementation fabrics as demanded by design requirements.

VHDL and Verilog both support two major forms of system definition: structural and behavioral. A structural description of a system describes the constituent components and the connections between those components. Structural description is roughly analogous to a textual form of the traditional graphical schematic design. Components, selected from a library of predefined parts, are instantiated the ports of components connected via external signals. Circuit descriptions are necessarily low-level, and there

is minimal support for capturing circuit patterns, in the style of Lava, as meta-programs, although VHDL does provide a generate construct for performing some restricted structural meta-programming.

Because a structural system description is defined at a low level, with components drawn from a predetermined library, they are often easy to synthesize to target fabrics. On the other hand, both VHDL and Verilog offer behavioral modeling capabilities that allow a system to be described at a higher-level of abstraction, but with a trade-off that some systems that can be expressed in the behavioral subset of the language cannot be synthesized. Consequently, users of the behavioral subset of the languages, and the vendors of synthesis tools, often resort to idiomatic programming styles that result in synthesizable designs.

Currently the most dominant of these idioms is that of Register-Transfer Level (RTL) modeling, where circuits are expressed as state, implemented as registers, connected by combinational circuitry that defines a transfer equation between the current values of each register to the next value. Control in such systems are implemented as state machines, with the registers determining the state of the system and the transfer equations determining the next state. A significant disadvantage of RTL modeling is that it implicitly includes the notion of a global clock coordinating the register/transfer equations. The global clock becomes burdensome when connecting two independently-developed components, as it necessitates globally satisfying the timing constraints of all components, or else defining custom coordination circuitry between those components to localize timing considerations.

In contrast, the thesis of this dissertation claims that inter-component communication should be structured asynchronously, and the communication protocol divorced from the internal workings of the component. Using a message-passing model of concurrency, we argue that the need for a global coordination signal based on a single clock is obviated. More importantly, the interaction between components can be described as an asynchronous exchange of a sequence of messages according to a specific protocol.

The thesis expressed in this dissertation, and the implementation strategy employed in its execution, is largely based of that of the Statically-Allocated Functional Language (SAFL) (Sharp and Mycroft 2000; Mycroft and Sharp 2000, 2001b,a; Sharp 2004). In this work, a functional language is as the basis for resource-aware hardware system construction. An extension to SAFL, called SAFL+, includes imperative state and first-class channels, much in the same way that we use imperative effects and message-based concurrency.

The fundamental distinction between SAFL and the work described in this thesis is that we have chosen to use monads, and monadic computations, as the basis for our language, while the SAFL work uses an operational model for the semantics of the language. We believe that using monads as a semantic basis provides an advantage when validating program manipulations, as described in chapter 4, as they provide an algebraic basis (Harrison 2006a) for relating the transformation of the programs to the underlying semantics, eliminating the need to jump to an external semantic formalism.

## 1.6 Dissertation contributions and organization

The thesis of this work is that a functional language, extended with monadic effects for imperative and message-passing based concurrency, is a suitable basis for constructing systems that will be synthesized to efficient hardware or software fabrics.

To support this thesis, this dissertation makes the following contributions:

- Oread, a functional language extended with *monadic* imperative and message-based concurrency effects.

- A framework for defining concurrency and communication protocols from within Oread.

- A compilation scheme for a subset of Oread that maps to hardware using an explicit control protocol.

- A series of source-to-source transformations that convert non-synthesizable Oread programs to those that satisfy the synthesizable subset of the language.

- A mapping of Oread to C, an imperative language, and Pthreads, a standard library for preemptive concurrency.

The remainder of this dissertation is organized as follows:

Chapter 2 gives an overview of Oread, with an emphasis on its monadic features. In addition to a description of the core language, we detail a general architecture for the combination of monadic Oread components. Later chapters demonstrate the flexibility of this architecture in two separate realizations, one in hardware and one in software.

Chapter 3 describes the compilation of a subset of Oread to hardware via the hardware description language. The compilation scheme uses a small set of simple VHDL components, described behaviorally, and generates a structural VHDL model of a Oread program as an instantiation of those components. The resulting implementation can be both simulated and synthesized. Chapter 4 describes the use of source-to-source program transformations to map general Oread programs that do not adhere to the hardware synthesis restriction required in chapter 3 into programs which are capable of being synthesized.

Chapter 5 details the compilation from Oread to C. The compilation results utilize none of the more sophisticated features of C, relying on the target language more as a high-level assembly, but with run-time support for dynamic memory allocation. The component combination architecture, described in 2, is implemented using a small collection of POSIX threads primitives.

Chapter 6 presents a case study using Oread in two example problems. The first example details the design of a single component, described in Oread and mapped to both hardware and software implementations according to the compilation schemes in chapters 3 and 5. The second example describes the integration of multiple components, both described in Oread, but targeting different implementation fabrics. This example explores the suitability of Oread for system-level heterogeneous design.

The dissertation concludes in chapter 7, where we revisit the motivation for the thesis and the suitability of the solution presented in the intervening chapters to support the dissertation's thesis. Finally, we identify important directions of future work that extend the development in this dissertation.

## Chapter 2

## Oread: A language for mixed-target synthesis

To exercise the thesis of this dissertation, we have defined a language, Oread, a higher-order functional language reminiscent of ML or Haskell. Oread has a static type system, with polymorphic types and user-defined algebraic data types. This core language is extended with constructs for imperative state and reactive concurrency. Effects in Oread are modeled monadically, allowing a clear delineation between the pure aspects of the language and those aspects that use imperative or concurrency constructs. Oread has been designed as a minimal language, with just the core features needed to demonstrate the thesis.

This chapter introduces Oread. We discuss the motivations that drove the design of the language and analyze how the language features present in Oread relate to the language features highlighted in the thesis. To this end, we provide an overview of the major structuring feature of Oread: the use of monads to encapsulate effects. Monads permeate Oread and the accompanying compilation tool-set, serving both as the computational model for programs written in the language, as well as the structuring mechanism for constructing the tool-set for processing Oread programs, including type-checking, interpretation, and compilation to both an imperative language to target software and VHDL to target hardware fabrics.

In many respects, Oread can be treated as a core intermediate language that is used in the compilation of a more full featured – or programmer-accessible – language. Nevertheless, to simplify the description of the language, we define a concrete syntax that allows programmers to write Oread programs directly. This concrete syntax is necessarily spare, and does not have much of the syntactic sugar that programmers would expect in a typical programming language. The constructs of the concrete syntax are introduced here as they are used, with a complete specification of the grammar in appendix 7.1.

A major contribution of this dissertation is the use of a reactive monadic computation to structure concurrency within a system. Because Oread is designed as a source language for both software and hardware targets, we have defined this concurrency abstraction so that it is not unnecessarily biased towards either target. The following two chapters demonstrate the suitability of this abstraction, as we demonstrate that the same concurrency model can be easily mapped to existing abstractions in both software, using operating system threads, and hardware, using a simple communication protocol.

However, we note that in designing system with concurrent components, it is not feasible to assume that all components will communicate using the same protocol. To this end, we have defined an architecture for defining interaction protocols between components within Oread itself. This architecture allows components to be defined using successively higher-levels of abstraction for constructing the communication and coordination protocols between components. At the simplest level, Oread provides a universal primitive for performing concurrent operations. At a slightly higher level, a programmer can define specific protocols by having components generate encoded messages and by assigning an interpretation to those messages. Finally, at an even higher level, a programmer can define functionality which to adapt protocols, allowing a component which behaves according to one protocol to be adapted for use in a context

requiring a different protocol. The two higher levels of abstraction are facilitated by the ability to define the concurrency protocols within Oread itself, using the concurrency architecture we have developed.

The remainder of this chapter is structured as follows. First, we discuss the motivation for the design of Oread and the relationship between the Oread features and those outlined in the thesis. This includes a description of the Oread concurrency architecture, which details how interaction protocols are defined in the system and the mechanism for assembling Oread components into a complete system. Next, we provide define the static and dynamic semantics of Oread. The language semantics are presented in monadic style. In the interest of making this dissertation self-contained, we provide a brief overview of monads.

# 2.1 Oread Design Motivation

### 2.1.1 A Functional Language

The functional subset of Oread is a strict higher-order functional language extended with algebraic data types, similar to the second-order lambda calculus (Reynolds 1974). Oread resembles modern functional programming languages such as Standard ML (Milner et al. 1997) and Haskell(Peyton Jones 2003). However, unlike Standard ML, Oread is pure, without effectful operations such references and call/cc. Similarly, Oread differs from Haskell in that it has strict evaluation semantics, as opposed to Haskell's normal-order evaluation semantics.

Oread departs from Standard ML by disallowing effectful computation within the functional subset. On the other hand, Oread *does* allow effectful computation, but the extent of the effects are encapsulated as monadic computations. The reliance on

monads resembles Haskell, which has used monads to great success to model effects in a pure language (Wadler 1993; Peyton Jones 2002; Swierstra and Altenkirch 2007).

Haskell has a normal-order evaluation semantics, which arguably leads to a more declarative style of programming (Hughes 1989). The decision to sacrifice more declarative normal-order semantics for strict evaluation semantics is pragmatic. Normal-order evaluation requires the dynamic allocation of space for function arguments that may (or may not) eventually be evaluated. While this strategy works well on a CPU with a significant amount of memory, it is impractical in hardware targets that require precise control over the allocation of resources, including memory allocation, and may (as does the Oread VHDL compilation) disallow dynamic allocation. Strictness analysis (Mycroft 1980) can identify safe transformations of normal-order programs into strict programs, yet it remains possible that some programs may not be transformable, which would retain the need to dynamically allocate space.

This core functional language is *pure*, in that it does not allow side effects within the functional subset of the language. The purity is important because it allows the safe application of fold/unfold transformations. An unfold transformation replaces call to a function with its definition, and conversely a fold transformation abstracts an expression into a new function and then replaces the original occurrence of the expression with a call to the new function.

Unfold transformations allow Oread to take advantage of the inherent parallelism of functional languages. Rather than perform data-independent (SIMD) operations in sequence, as may be the case on a CPU, the common portion of the computation shared among the independent portions of the overall computation can be folded into a top-level function. Applying that operation across a list of elements can be defined using a higher-order function that captures the recursion behavior. Finally, the higher-order function can be unfolded, and then the individual calls to the top-level function.

**Example:** Consider a program that maps defines an inc function across a list of elements. The List data declaration defines a polymorphic List data type, with two constructors, Cons and Null. The map function takes a function, f, and a list, 1, and generates a new list formed by applying f to each element of the input list.

If both the map and the inc functions are unfolded onto a list with elements a, b, c:

```

(map inc (Cons a (Cons b (Cons c Null))))

```

The unfolded operation inlines all of the calls to map and to inc:

```

(Cons (+ a 1) (Cons (+ b 1) (Cons (+ c 1) Null)))

```

This unfolding – when performed on a program targeting hardware – will result in a duplication of circuitry. However, each copy of the circuit can be active concurrently, yielding a net performance gain at the expense of circuit area. If the functions being manipulated using fold/unfold transformations were not pure, then the transforms would not be safe, because they may result in a duplication of, or reduction in, the computational effects of the original program.

Being able to perform program manipulations is critical to target Oread specification to both hardware and software implementations from a single source. In chapter 1 we argued that a major difference between hardware and software design is in the ability for the designer to precisely control the number of computational resources that are

available. In software, the compiler has no choice but to use the resources offered by the CPU, thus it will time-multiplexing data parallelism across those limited resources, generally using a loop. On the other hand, hardware allows the designer to dictate exactly how many of a given computational resource you wish to use, and incorporate that into your circuit.

It is possible to take a pure Oread program and inline it into its primitive components, resulting in a large combinational circuit in hardware or a large program text in software. This is unwise from a design perspective because there is no accounting for space or time limitations in the target model. Consequently, Oread includes two constructs for controlling the time and space behavior exhibited by a pure program: shared function blocks and a parallel let expression.

An Oread program consists of a set of top-level function definitions, along with a "main" expression that can call the defined functions. A top-level function delimits a shared resource. In hardware, the body of the function will be implemented as a single circuit, regardless of the number of calls to the function. If there are, in fact, multiple calls to the function, the function block contains arbitration logic that will process those calls in some undetermined sequential order. This sharing of circuitry is a space vs. time trade-off. The extremes between complete unfolding of all calls to a function (resulting in increased area usage) and multiplexing all calls onto a single shared block (resulting in increased contention) can be explored using fold/unfold program transformations. A designer can take a single shared function block and duplicate it, and distribute the calls to the original function amongst the various duplicated blocks.

**Example:** Returning to the unfolding example from above, rather than unfold the inc function, we can duplicate it to define *two* increment functions, and then map different

calls to the various top-level definitions. The two calls to incl will occur sequentially with each other, but in parallel with the call to incl.

```

(define (incl (x Int) Int) (+ x 1))

(define (inc2 (x Int) Int) (+ x 1))

(Cons (incl a) (Cons (inc2 b) (Cons (incl c) Null)))

```

Second, Oread includes a let construct that introduces sequentiality and sharing into a program. Suppose that a particular Oread expression will, when compiled to a hardware target, result in a very long critical path. Inserting a pipeline register into the circuit, and thus reducing that critical path, is as simple as selecting a sub-expression and adding a named binding via a let expression. Likewise, a common sub-expression can be factored into a single let binding. Rather than a circuit for each instance of the sub-expression, the synthesis scheme will generate a single circuit that can be shared among all references to that sub-expression.

The functional subset of Oread is extended with a small collection of primitive types (integers and floating-point numbers) and operations on those primitives. This collection was selected largely because they are commonly used in implementing standard embedded systems. The range of data types representable in Oread is not limited to this set because the algebraic data type facilities of Oread allow a programmer to define new types of data as well as operations upon that data.

The set of primitive types and operations in Oread can be easily extended, as long as those operations remain pure. The design of the tool-set developed for Oread provides additional support for extending (or contracting) the language with new primitive types and operations by be constructed using modular monadic semantic techniques (Espinosa 1995; Liang et al. 1995; Liang and Hudak 1996). The choice of primitive types is skewed neither towards hardware or software compilation targets. For example, the

language includes support for floating-point arithmetic, an operation that is typically quite space-expensive to implement in hardware. On the other hand, tuple selection and construction operations are trivial to implement in hardware yet are considerably more complex on a CPU with a fixed word size.

## 2.1.2 Monadic encapsulation of effects

The ability to perform program transformations gives justification to the pure functional subset of Oread. However, the pure functional subset of the language is simply too restrictive to be practical for building embedded applications. This is because the pure functional model is heavily skewed towards data-flow computation, which is a poor abstraction when constructing control-intensive or reactive systems, both of which are common traits of embedded systems.

We take the viewpoint that control implies a notion of state. This, taken with the interaction with external entities implied by reactive components, forces Oread to include a way to perform both stateful and reactive effects. However, we wish to add constructs for building these sorts of computations without breaking the purity that we rely on to justify transformations that allow us to target both hardware and software. Therefore, we use monads to structure effectful computations.

By structuring computational effects using monads, we get a *static* delineation between pure operations and effectful computations that is expressed at the type level. An effectful computation can include pure computations, but the converse is not true. This means that the extent that transformations are valid are clearly delimited by the monadic encapsulation of effects. The synthesis tool-set is free to transform programs within a monadic computation, but the transformations may never escape those monad boundaries.

Data transformation components, such as those typically found in the example soft-ware defined radio domain, have a standard structure. A component is a loop that receives data from some external entity via the reactive concurrency construct, performs some processing on that data, sends the data onto another component via the reactive concurrency construct, and repeats. The component may perform several loop iterations between receives/sends. Also, the component may carry some state across iterations. The primary purpose of this state is to simplify the specification of control logic.

The Oread monadic constructs are segmented into two categories. The first category contains two constructs for performing imperative effects, and the second category has one construct for reactive concurrency. The imperative, or state, constructs include a **get** function for accessing state, and a **put** function for mutating the state. Both of these functions use addressable state.

**Example** The stateFun function below reads a value from address 0 and uses that value as an address to which the input parameter val is written.

### 2.1.3 A monadic concurrency architecture

Oread includes a **signal** construct for performing reactive concurrency. This construct takes a message and routes that message to an external entity. From the viewpoint of a component, the outside world is accessible only via the signal construct, and can only be affected by signaling a request. Once a computation signals a request, the

computation will block until a response is returned from an external entity. Signaling a request and then interpreting the response is the only way to observe the outside world from a reactive computation, and so comprises the complete Oread concurrency semantics within the language. These semantics leave much undefined: the content of the request/response messages, how are the messages are interpreted, and how are they routed between components.

Oread does not include special semantics for different types of reactive communication simply because the possible range of different inter-component communication is boundless. As examples, the inspiration for this work used the reactive monad construct to model an operating systems kernel (Harrison 2006b), while in contrast we have defined a series of point-to-point communication behaviors that include a mail-box, bounded FIFO, and unbounded FIFO. The basic concurrency constructs allow us to model each of these, but the specific behavior for each communication is defined within Oread as a collection of functions, rather than as special language constructs. These functions are arranged according to a regular pattern, thus we have developed a nomenclature to refer to the various elements.

First, a **thread** is a processing component. A thread may consist of a combination of pure functional, imperative, and reactive expressions. The single point of interaction with outside entities for a thread is via the reactive constructs. However, a thread may interact with several different external entities, with each interaction accomplished with a different **protocol**. A named interaction point for a **thread** is called a **port**. Finally, each ports is connected to a **service**, which is a collection of Oread functions that implements the protocol the connected threads use.

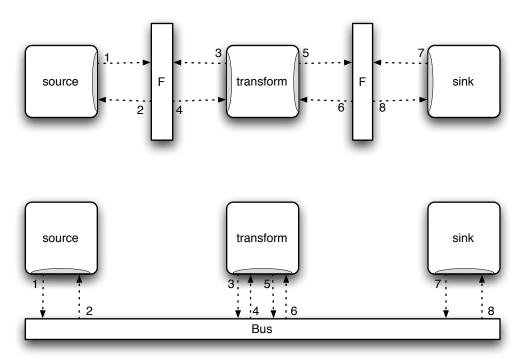

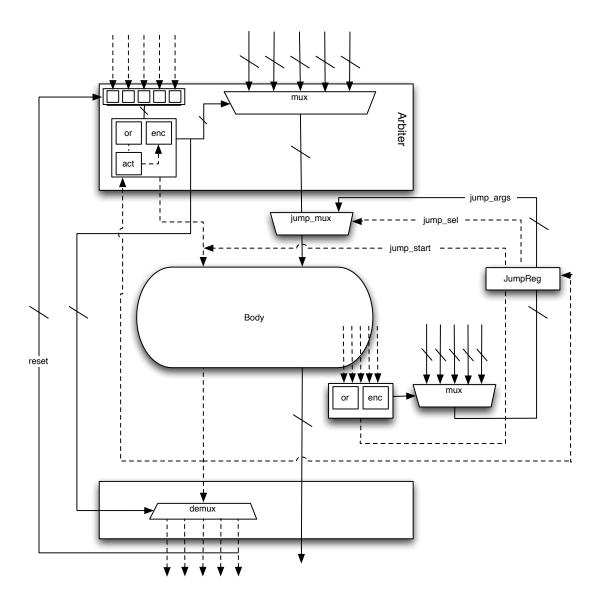

For example, consider a component that operates in a stream processing manner: consuming data from an input source, manipulating the data, than sending the data on to an output sink. Figure 2.1 has two examples of this architecture. The boxes labeled

source, transform, and sink are Oread threads. Each thread has ports, indicated by the grayed semicircles where arrows enter and exit the thread. The rectangles labeled F in the top figure and Bus in the bottom are services. In the top figure, the transform component has two ports, each of which is connected to a separate service. In the bottom figure, the transform component has a single port, connected to the Bus service.

Figure 2.1: Example system architecture

The transmission of messages between threads and services is indicated in the figure by the dotted arrows. The arrows are numbered to indicate the ordering of messages. For example, in the top figure, the source will (1) issue a Send request to the F service that includes the data it wishes to send to the transform thread. The thread then blocks until the service (2) responds with an Ack response. The transform component (3) issues a Receive request to the service F, and then block until F (4)

sends a response that includes the data originally transmitted by source. The series of messages 5,6,7,8 uses the same protocol to transfer data from transform to sink.

It is critical to note that the ordering of messages is only for expository purposes. Because the threads source, transform, and sink are operating concurrently, each may issue request at any time, subject the protocol restriction. Temporally, there will be an ordering between request/response pairs: 1 comes before 2, 3 before 4, and so on. In the Oread concurrency architecture, a request/response message pair is called a **service transaction**. The logic of a thread will also dictate the ordering of service transactions – for example, the transaction (3,4) necessarily comes before (5,6), since it is necessary for the transform service to receive data to process before processing it and sending it on to the sink thread.

The lower figure has all three threads connected via a single Bus service. Consequently, the transform thread has a single port for communicating with the Bus service, in contrast to the two ports in the point-to-point model with FIFO services. Moreover, the reorganization of the system architecture requires each thread to add additional information to the requests issued to the Bus service indicating the intended destination for the message. In contrast, the architecture in the top diagram allows communication addressing to be implied by the port.

The F and Bus services in the diagrams implement a given protocol. This is accomplished with a pair of Oread functions: a **handler** function that takes a request issued by a thread and generates the appropriate response, and a **scheduler** function that determines when a response generated by the handler can be returned to the appropriate blocked thread. These functions can include imperative effects, which allow the service to implement the control portion of its protocol. This can be illustrated using the top example architecture from above. The service that handles communication between the source and transform thread will initially be in a state waiting for a request from

either thread. Upon receiving a request, the service invokes the handler function on the request. If the request is from source and is a Send request, the service will store the value included in the request and generate an Ack response. The scheduler function will then be invoked, which will return that Ack response to the source thread. Alternatively, if the request is a Receive request from the transform thread, the handler will note that a receive is pending, but cannot generate a response immediately, because there is no previous send request from the source thread. In this case, the scheduler function will indicate that there are no pending responses to transmit to threads, and the scheduler will wait for the next request, which can only come from the source thread, as the transform thread will remain blocked until the service returns a response to its receive request.

Hence, the service implements a very simple mailbox protocol: a receive request will cause the issuing thread to block until there has been a matching send request. Moreover, if a thread issues two consecutive send requests, and the service does not receive an intervening receive request, the sending thread will block on the second send until a receive is issued. This is a degenerate case of a bounded FIFO, which would allow an arbitrary (but fixed for a particular instance) number of sends without an intervening receive, simply by using a larger imperative state for buffering sent data. The bounded FIFO is, in turn, a specialization of an unbounded FIFO. However, the unbounded FIFO requires that the service be able to dynamically allocate storage, which is typically not possible in a direct hardware implementation. This suggests a Oread design process: first, a system is modeled as a collection of threads communicating with each other via a given protocol. The system developer generates a service definition which provides the loosest bounds on implementation, such as the unbounded FIFO implementation of point-to-point communication, and uses that model for simulation and early design testing. Then, as threads are mapped to various implementation

targets, technology specific knowledge is used to drive the transformations of Oread thread definitions to get implementations which can match the capabilities of the target platform.

### 2.2 Oread semantics

Oread is a statically typed functional language, extended with monadic features for imperative and concurrent effects. We define the semantics of Oread below, giving both the static semantics and the dynamic semantics for the language. These semantics are written in monadic style, with the resulting semantics, when realized in a pure functional host language such as Haskell, being both definitional and executable specifications.

#### **2.2.1** Monads

Monads are used extensively in Oread, both in the programming model as well as in the implementation of the tools used to process Oread programs. Viewed in another way, Oread is simply a thin veneer used to construct monadic computations. The tool-set we have defined then is just an interpretation of these monadic computations in either hardware or software.

A monad is a mathematical structure which encapsulates effects. When modeled in a functional language, a monad is a type constructor, T, paired with two *monad morphisms*, unit ::  $A \to T$  a and bind :: T  $A \to T$  b)  $A \to T$  b. A monadic computation M :: A a will yield a value of type A.