# Controlling Interface for Metal-Insulator-Metal Architectures with Ultrathin Dielectric Fabricated Using Atomic Layer Deposition and Sputtering

By © 2019

#### Jagaran Acharya

Department of Physics and Astronomy

The University of Kansas, Lawrence, KS

Submitted to the graduate degree program in Physics and Astronomy, the College of Liberal Arts and Science in partial fulfilment of the requirements for the degree of

### **Doctor of Philosophy**

| Chair: Judy Wu, PhD, University<br>Distinguished Professor |       |

|------------------------------------------------------------|-------|

| Siyuan Han, PhD, Professor                                 |       |

| Michael J. Murray, PhD, Professor                          |       |

| Wai-Lun Chan, PhD, Associate Profe                         | essor |

| Cindy L. Berrie, PhD, Professor                            |       |

Date defended: November 25, 2019

The dissertation committee for **Jagaran Acharya** certifies that this is the approved version of the following dissertation:

# Controlling Interface for Metal-Insulator-Metal Architectures with Ultrathin Dielectric Fabricated Using Atomic Layer Deposition and Sputtering

\_\_\_\_\_

Judy Wu, PhD, University Distinguished Professor Chair of Committee

Date Approved: December 13, 2019

### **Abstract**

The miniaturization of future microelectronics demands the development of high quality ultrathin (few to sub-nm) dielectric films for application in metal-insulator-metal (MIM) architectures. Among all other approach employed for ultrathin dielectric film fabrication, atomic layer deposition (ALD) provides a unique approach for the fabrication of ultrathin TBs with several advantages including an atomic-scale control on the TB thickness, conformal coating, and low defects density. Despite extensive efforts in ALD devices, the figure-of-merit dielectric constant  $(\varepsilon_r)$  exhibits a significant monotonic decrease with the film thickness as compared to bulk single crystal value. Primarily, the control over metal-insulator (M-I) interface, specifically in ultrathin thickness range, remains a challenge due to the formation of defective oxides and interfacial layer (IL). This work demonstrates the development of high quality Al/ALD Al<sub>2</sub>O<sub>3</sub>/Al MIM trilayers using a unique in-house integrated in situ deposition (sputtering/ALD) method. These trilayers devices were characterization to understand and control the IL formation with atomic precision. To the best of our knowledge, high  $\varepsilon_r \sim 8.9$  that is within 3% of the bulk value  $\sim 9.2$  has been achieved for the first time on the ALD Al<sub>2</sub>O<sub>3</sub> films in thickness range ~3.3-4.4 nm. This corresponds to an effective oxide thickness ~1.4-1.9 nm comparable to High-K HfO<sub>2</sub> of 3-4 nm. The low leakage current density (J)  $\sim 10^{-9} A/cm^2$  is an order of magnitude lower than the best previously reported values. These results suggest that the optimal ultrathin high quality ALD Al<sub>2</sub>O<sub>3</sub> provides a much lower-cost alternative for gate dielectric. Also, ALD Al<sub>2</sub>O<sub>3</sub> seed layer (SL) approach was used to illustrate the critical importance of control over M-I interface to obtain dense hydroxylation and reduce incubation period, improving the dielectric properties of ultrathin ALD

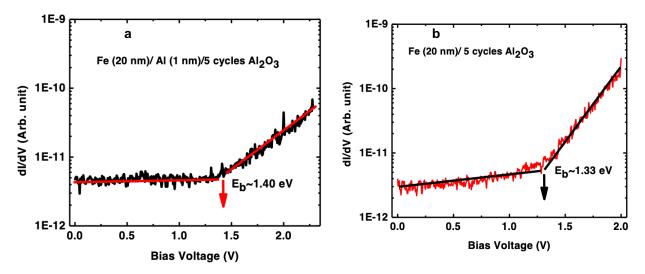

MgO films. ALD MgO with SL demonstrated  $\varepsilon_r \sim 8.8-9.4$  in thickness range  $\sim 3.8-4.9$  nm comparable to bulk MgO  $\sim$ 9.4. In contrast, low  $\varepsilon_r \sim$ 3.6-4.7 was observed for ALD MgO without Al<sub>2</sub>O<sub>3</sub> SL in a similar thickness range. Both the scanning tunnelling spectroscopy and ab-initio molecular dynamics studies point out that SL allows the initial dense nucleation and perfect interface resulting in a high quality dielectric with tunnel barrier height  $(E_b)$ ~1.5 eV compared to 0.8 eV for MgO without SL. This result provides an approach to engineering incompatible M-I interface using a SL for obtaining high quality dielectric as required for applications in MIM tunnel junctions and CMOS. In addition, tuning thickness of Al wetting layer  $(t_{Al})$  in capacitors consisting of Nb (25 nm)/Fe (20 nm)/ALD Al<sub>2</sub>O<sub>3</sub> (2.2 nm)/ t<sub>Al</sub>/Fe (20 nm)/Nb (50 nm) shows switching between pure dielectric behavior for  $t_{Al} > 1$  nm and ferroelectric/dielectric (FE/DE) bilayer at  $t_{Al} \le$ 1 nm. These FE/DE bilayer gate with ultrathin DE are promising for low power microelectronic devices. This helps to realize FE/DE bilayer capacitors with a total FE/DE total thickness < 3-4 nm that show a dynamic switching on/off of the negative capacitance under the application of an external force. This result not only provides a viable approach for generating ultrathin FE/DE bilayer capacitors but also offers a promising solution to low-power consumption microelectronics and piezoelectric sensors applications. Pinhole-free and defect-free ultrathin dielectric tunnel barriers (TBs) is a key to obtaining high tunnelling magnetoresistance (TMR) and efficient switching in magnetic tunnel junctions (MTJs). Motivated by this, this work explores fabrication and characterization of spin-valve Fe/ALD-Al<sub>2</sub>O<sub>3</sub>/Fe MTJs with ALD Al<sub>2</sub>O<sub>3</sub> TB thickness of 0.55 nm using in situ ALD. Remarkably, high TMR values of  $\sim$ 77% and  $\sim$  90% have been obtained respectively at room temperature and at 100 K, which are comparable to the best reported on MTJs

having thermal AlO<sub>x</sub> TBs with optimized device structures. *In situ* scanning tunnelling spectroscopy characterization of the ALD Al<sub>2</sub>O<sub>3</sub> TBs has revealed a higher tunnel barrier height  $E_b$  of 1.33 eV, in contrast to  $E_b\sim0.3$ -0.6 eV for their AlO<sub>x</sub> TB counterparts, indicative of significantly lower defect concentration in the former. This first success of the MTJs with sub-*nm* thick ALD Al<sub>2</sub>O<sub>3</sub> TBs demonstrates the feasibility of *in situ* ALD for fabrication of pinhole-free and low-defect ultrathin TBs for practical applications and the performance could be further improved through device optimization.

## This work is dedicated to my respected parents

## Mr. Bala Krishna Acharya and Mrs. Kamala Acharya

#### and

### to my beloved wife

Mrs. Samita Sapkota Acharya and son Ivaan Acharya, welcome baby!

### **Declaration**

I hereby declare that except where otherwise stated, the contents in this dissertation is the result of my own work and includes a part of results which is the outcomes of work done in collaboration. The results have not been submitted in whole or in part for consideration for any other degree or qualification in the University of Kansas, or any other University. This dissertation contains around 37500 words including bibliography, footnotes, figures, tables, and equations, and has less than 60 figures.

Jagaran Acharya

November 25, 2019

## **Acknowledgements**

My PhD journey would be incomplete without thanking many people for their tremendous help and support, without them I would not have made this far. First and foremost, I would like to express my sincere thanks to my advisor, Dr. Judy Z. Wu, who has always been the constant source of inspiration and encouragement during the PhD journey. I feel privileged to work under her supervision. She taught me about scientific research, troubleshooting and new direction in experimental physics, and was always there to help me whenever I needed the most. Dr. Wu never gave up pushing me to grow as a professional and I will miss your supervision. I would also like to express my sincere thanks to all committee members for their valuable time, support, and dedication: Dr. Siyuan Han, Dr. Wai-Lun Chan, Dr. Michael J. Murray, and Dr. Cindy L. Berrie. Specially thanks to Dr. Siyuan Han who helped me with his valuable expertise in tunnel junctions during different steps of the experiment.

I would like to thank my colleagues and collaborators, especially those who helped me directly with this dissertation: Dr. Jamie Wilt, Dr. Ridwan Sakidia, Ryan Goul, and Melisa Xin. I would like to thank Department of Physics and Astronomy for their support during my graduate studies and continuous encouragement in this journey.

I am deeply indebted to all my family members, friends and relatives for their kind encouragement and support during my studies. The constant encouragement and love from my father Bala Krishna Acharya, mother Kamala Acharya and my sister Jagarita Acharya helped me to complete my educational journey so far.

Finally, I would like to thank my spouse Samita Sapkota Acharya for her love and support during my studies at University of Kansas. Thank you for being there with me at the hardest moments of my life and constant encouragement to pursue towards my goal. You are awesome, I love you.

## **Table of Contents**

| Table of  | Contentsx                                         |    |

|-----------|---------------------------------------------------|----|

| List of F | gures xiii                                        |    |

| List of T | ablesxix                                          |    |

| List of S | ymbolsxx                                          |    |

| Chapter   | I Introduction                                    |    |

| 1.1       | Metal-Insulator-Metal Architecture                | 1  |

| 1.2       | Gate Dielectric for CMOS                          | 5  |

| 1.3       | Magnetic Tunnel Junction                          | 8  |

| 1.4       | Physics of Spin Tunnelling                        | 10 |

| 1.5       | Tunnelling Magnetoresistance                      | 13 |

| 1.6       | Application of MTJs                               | 16 |

| 1.7       | Recent Progress in MTJs                           | 18 |

| 1.8       | Challenges and Alternative Approaches             | 22 |

| 1.8.      | 1 Issues in Synthesis of Ultrathin Dielectric     | 22 |

| 1.8.      | 2 Atomic Layer Deposition of Ultrathin Dielectric | 24 |

| 1.9       | Critical Issues to Be Addressed                   | 30 |

| Chapter   | 2 Experimental                                    |    |

| 2.1       | Fabrication of MIM Architecture                   | 32 |

| 2.2       | Fabrication of Devices                            | 34 |

| 2.2.      | 1 Capacitors                                      | 34 |

| 2.2.      | 2 Magnetic Tunnel Junctions                       | 36 |

| 2.3       | Characterization                                  | 43 |

| 2.3.      | 1 Vibrating Sample Magnetometer                   | 43 |

| 2.3.      | 2 Atomic Force Microscopy                         | 44 |

| 2.3.      | 3 Ex-situ C-V Measurement                         | 45 |

| 2.3.      | Four Probe I-V Measurement                        | 47 |

| 2.3.      | 5 TMR Measurement in PPMS System                  | 47 |

| 2.3.      | 6 In situ STS Characterization                    | 49 |

| Chapter                                     | 3 Probing Effect of Interface on Dielectric Properties of Ultrathin Al/Al <sub>2</sub> 50                                    | O <sub>3</sub> /Al Trilayers |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 3.1                                         | Controlling Metal-Insulator Interface                                                                                        | 52                           |

| 3.2                                         | Properties of Optimal ALD Al <sub>2</sub> O <sub>3</sub> Ultrathin Dielectric Films                                          | 57                           |

| 3.3                                         | Estimates of Thickness of Interfacial Layer                                                                                  | 61                           |

| 3.4                                         | AC Impedance Measurement                                                                                                     | 63                           |

| 3.5                                         | Leakage Current and Breakdown Characteristic of Dielectric                                                                   | 65                           |

| 3.6                                         | In situ STS Characterization of ALD Al <sub>2</sub> O <sub>3</sub> Films                                                     | 69                           |

| 3.7                                         | Chapter 3 Conclusion                                                                                                         | 72                           |

| Chapter<br>Situ Ato                         | 4 Effect of Al <sub>2</sub> O <sub>3</sub> Seed-Layer on Properties of Ultrathin MgO Films Fab mic Layer Deposition          | _                            |

| 4.1                                         | Controlling Interfacial Layer Formation for ALD MgO                                                                          | 76                           |

| 4.2                                         | Ab initio Molecular Dynamics Simulations                                                                                     | 78                           |

| 4.3                                         | Optimization of Thickness of ALD Al <sub>2</sub> O <sub>3</sub> Seed Layer                                                   | 80                           |

| 4.4                                         | Dielectric Properties of MgO With and Without Seed Layer                                                                     | 82                           |

| 4.5                                         | Effect of Interface on Leakage Current                                                                                       | 88                           |

| 4.6                                         | Chapter 4 Conclusion                                                                                                         | 89                           |

| Chapter<br>Capacite                         |                                                                                                                              | ectric/Dielectric            |

| 5.1                                         | Device Structure and Growth Mechanism                                                                                        | 93                           |

| 5.2                                         | Dielectric Properties by Tuning Al Wetting Layer Thickness                                                                   | 95                           |

| 5.3                                         | Mechanism for Observation of Negative Capacitance                                                                            | 97                           |

| 5.4                                         | Dynamic Response Under External Force                                                                                        | 99                           |

| 5.5                                         | Properties of FE/DE Stack                                                                                                    | 101                          |

| 5.6                                         | Chapter 5 Conclusions                                                                                                        | 103                          |

| Chapter<br>Al <sub>2</sub> O <sub>3</sub> T | 6 High Tunnelling Magnetoresistance in Magnetic Tunnel Junctions wit unnel Barriers Fabricated Using Atomic Layer Deposition |                              |

| 6.1                                         | Optimization of Multilayer Thin Films Structure                                                                              | 108                          |

| 6.2                                         | MTJs Device Structures                                                                                                       | 110                          |

| 6.3                                         | Characterization of MTJ Devices                                                                                              | 111                          |

| 6.4                                         | Improving MTJs Performances                                                                                                  | 117                          |

| 6.5                                         | Chapter 6 Conclusion                                                                                                         | 120                          |

| Chapter 7   | Conclusion and Future Perspective | .122 |

|-------------|-----------------------------------|------|

| References: | 125                               |      |

## **List of Figures**

| Figure 1.1 Schematic of metal-insulator-metal architecture a) conformal ultrathin ALD sidewall spacer gate dielectric in field effect transistors (FinFETs) or Tri-Gate for complementary metal-oxide-semiconductor (CMOS) technology b) Josephson Junction with ultrathin dielectric sandwich between two superconducting electrode with Copper pair tunnelling and c) Magnetic Tunnel Junctions with ultrathin dielectric sandwich between two ferromagnetic electrode with spin polarized electron tunnelling                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

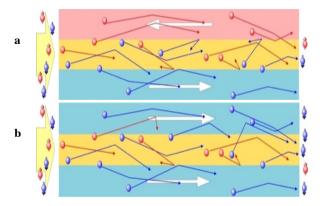

| Figure 1.2 Schematic of giant magnetoresistance device structure with two FM electrodes in a) anti-parallel orientation ( <i>i.e.</i> red and blue) layers separated by non-magnetic electrode ( <i>i.e.</i> yellow) resulting low spin polarized current (or high resistance state) and b) parallel orientation ( <i>i.e.</i> blue and blue) separated by non-magnetic electrode ( <i>i.e.</i> yellow) resulting high spin polarized current (or low resistance state)                                                                                                                            |

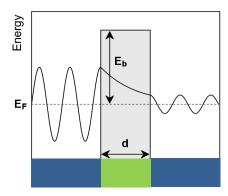

| Figure 1.3 Schematic of the metal-insulator-metal structure with ultrathin 1D potential barrier with barrier height $(Eb)$ and thickness $(d)$ showing the basics of quantum tunnelling in which the electron wave function decays exponentially across barrier for electrons with the Fermi energy $(E_f)$                                                                                                                                                                                                                                                                                        |

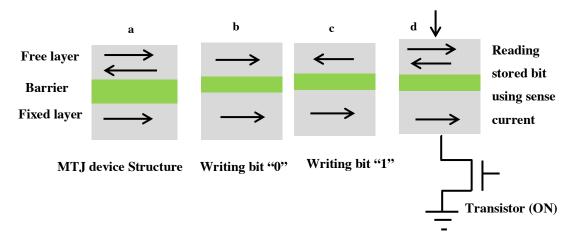

| Figure 1.4 Schematic of a) MTJ structure with free layer (top), fixed layer (bottom) and tunnel barrier (middle) b) writing bit "0" (with parallel resistance <i>RP</i> configuration) c) writing bit "1" (with anti-parallel resistance <i>RAP</i> configuration) and d) reading the stored bit using sense current and compare the output with transistor                                                                                                                                                                                                                                        |

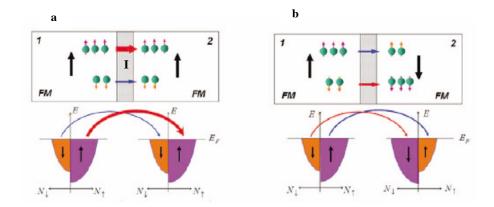

| Figure 1.5 Schematic of tunnelling magnetoresistance (TMR) in MTJ structure showing spin tunnelling with a) parallel configuration with spin up as majority carriers in both FM electrodes (Bottom left figure shows density of states of corresponding to the FM electrodes in parallel configurations); and (b) anti-parallel configurations with spin up as majority carriers in FM1 and spin down as majority carriers in FM2 (Bottom right figure shows density of states of corresponding to the FM electrodes in anti-parallel configurations). This figure is adapted from reference [31]. |

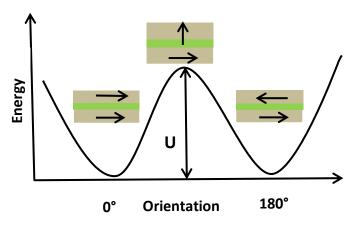

| Figure 1.6 Schematic of switching energy of MRAM device structure where randomization of spin is prevented with energy barrier ( $U$ ) required to overcome to switch from easy axis magnetization direction ( $i.e.$ 0° to 180°) to perpendicular to the plane configuration (90°) for non-volatile memory applications                                                                                                                                                                                                                                                                           |

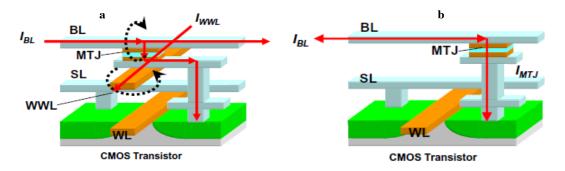

| Figure 1.7 Schematic of (a) conventional MRAM device using magnetic field induced writing by the current passing through bit line (BL) and write world line (WWL) and (b) STT-MRAM device with spin transfer torque magnetization switching with write operation performed by passing the current directly through MTJs. This figure is adapted from reference [43,44] 18                                                                                                                                                                                                                          |

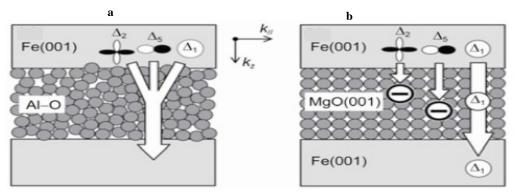

| Figure 1.8 Schematic of different electronic states tunnelling through (a) amorphous AlO <sub>x</sub> with variety of Bloch waves with different symmetries couple with evanescent states in barrier resulting non-coherent tunnelling and (b) crystalline MgO barrier that can preserve the symmetry of different electronic states tunnelling in FM electrodes resulting coherent tunnelling. This figure is adapted from reference [31]                                                                                                                                                    |

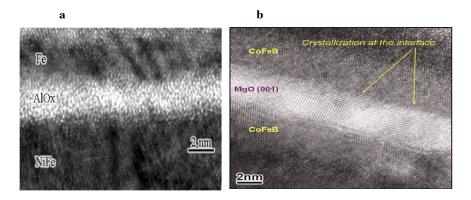

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.9 Transmission Electron Microscope (TEM) image of a) Fe/AlO <sub>x</sub> /NiFe showing non-uniform amorphous AlO <sub>x</sub> . This figure is adapted from reference [31] and b) CoFeB/MgO/CoFeB showing crystalline MgO barrier after post annealing at 500 °C. This figure is adapted from reference [48]                                                                                                                                                                                                                                                                         |

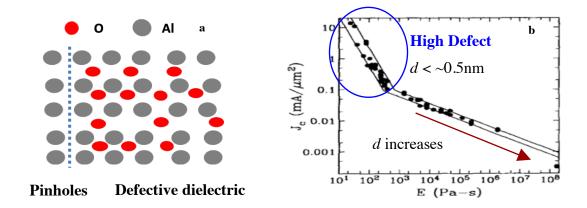

| Figure 1.10 a) Schematic of growth mechanism for thermal $AlO_x$ TB with high defects and pinholes resulting defective dielectric and b) $J_c$ vs exposure (pressure* time) for JJs show less stepper slope for thickness > 0.5 nm and steeper slope at thickness < 0.5 nm indicative defective dielectric with low $Eb$ . This figure is adapted from reference [5]                                                                                                                                                                                                                          |

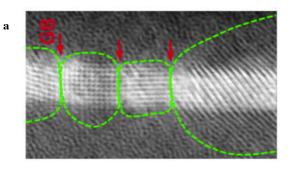

| Figure 1.11 a) Formation of grain boundaries in epitaxial CoFeB/Mgo/COFeB as indicated by dashed lines where MgO grains are indicated by arrows. This figure is adapted from reference [61] and b) defects and pinholes as observed in MgO barrier due to high temperature post annealing. This figure is adapted from reference [62]                                                                                                                                                                                                                                                         |

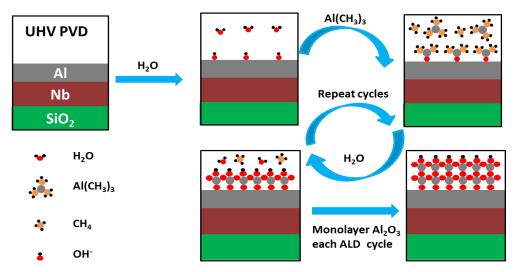

| Figure 1.12 Step by step growth mechanism for ALD Al <sub>2</sub> O <sub>3</sub> with optimal ALD parameters without an interfacial layer formation a) fabrication of thin film using ultra-high vacuum (UHV) using physical vapor deposition (PVD) b) exposure of H <sub>2</sub> O c) exposure of tri-methyl aluminium (TMA) d) exposure of H <sub>2</sub> O to complete one ALD-cycles producing monolayer of Al <sub>2</sub> O <sub>3</sub> and e) each layer control by deposition of sequential exposure of chemical producing conformal, stoichiometric and low defects ALD dielectric. |

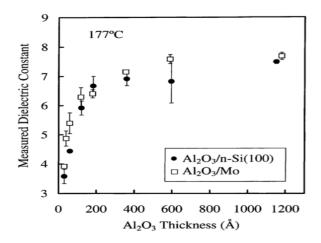

| Figure 1.13 Measured dielectric constant for $Al_2O_3$ ALD films of different thicknesses grown at 177 °C on n-Si(1 0 0) and Mo-coated Si(1 0 0). This figure is adapted from reference [71] 30                                                                                                                                                                                                                                                                                                                                                                                               |

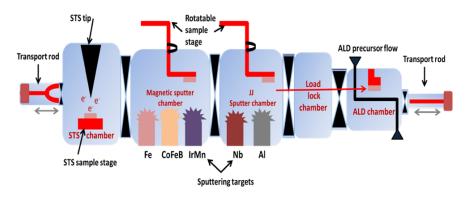

| Figure 2.1 Schematic of all <i>in situ</i> in-house integrated ALD-PVD-STS UHV system with load lock, ALD chamber, Josephson junction sputter chamber, Magnetic sputter chamber and STS characterization chamber.                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 2.2 Photograph of all in situ in-house integrated ALD-PVD-STS along with each chamber label as indicated for fabrication and characterization of multi-layered MIM and TJs devices 33                                                                                                                                                                                                                                                                                                                                                                                                  |

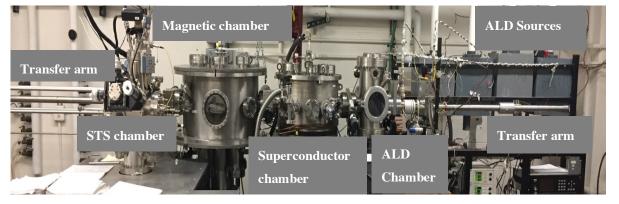

| Figure 2.3 (Left) Schematic diagram (viewed from above) of the bottom electrode (yellow) with a shadow mask used to define the 400, 300 and 200 $\mu$ m wide bridges and the top electrode (brown) with a 200 $\mu$ m wide bridge to define the corresponding MIM capacitors                                                                                                                                                                                                                                                                                                                  |

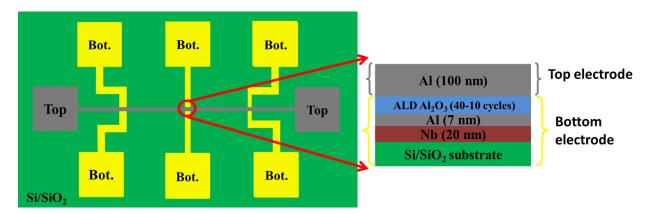

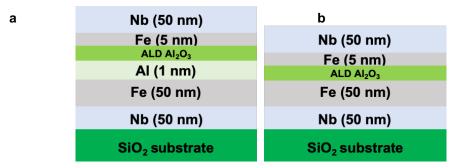

| Figure 2.4 Schematic for magnetic tunnel junction device structure a) Nb (50 nm)/Fe (50 nm)/Al (1 nm)/ALD Al <sub>2</sub> O <sub>3</sub> / Fe (5 nm)/Nb (50 nm) with Al wetting layer and b) Nb (50 nm)/Fe (50 nm)/ALD Al <sub>2</sub> O <sub>3</sub> / Fe (5 nm)/Nb (50 nm) without Al wetting layer                                                                                                                                                                                                                                                                                         |

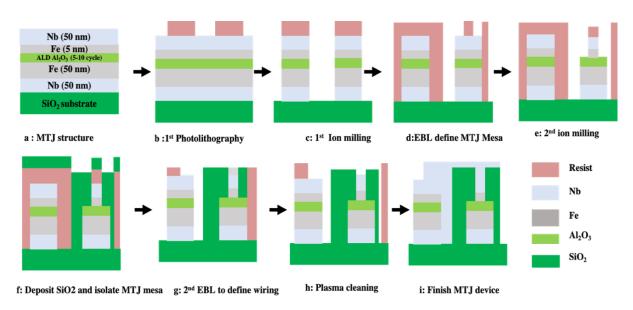

| Figure 2.5 Schematic flow chart of Magnetic tunnel junction fabrication with different steps of fabrication process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

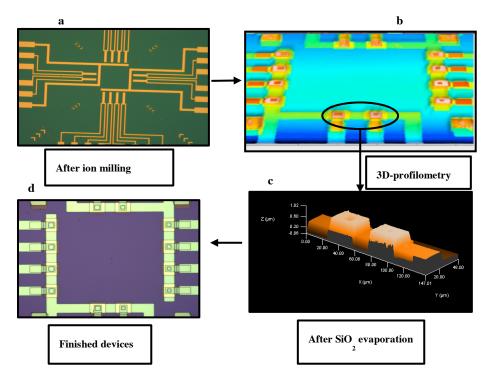

| Figure 2.6 Real micrograph of devices after different steps of fabrication process a) micrograph of main wiring after 1 <sup>st</sup> ion milling b) 3D-profilometry after sio2 evaporation c) Step height measurement with Sio2 evaporation and d) Micrograph of finished devices                                                                                                                                                                                                                                                                                                                                                                                 |

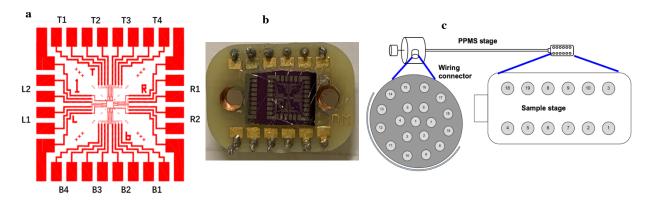

| Figure 2.7 a) Schematic of photomask used to define MTJ circuit with each MTJ has pair of electrode and ground electrode shared among 6 MTJs for four probe measurement b) photograph of MTJ chip wire bonded to sample stage and c) Schematic showing PPMS stage, sample stage and wiring connector for TMR measurement                                                                                                                                                                                                                                                                                                                                           |

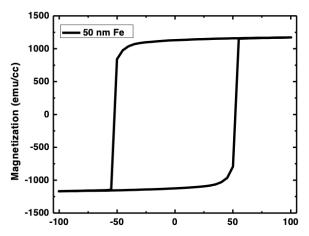

| Figure 2.8 Magnetization (in emu/cc) vs magnetic field (in Oe) (M-H) hysteresis loop for Fe (50 nm) characterized using vibrating sample magnetometer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

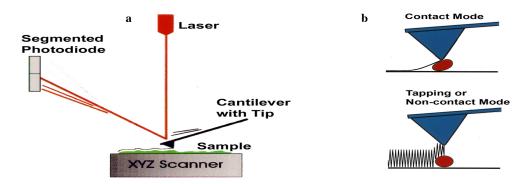

| Figure 2.9 a) Schematic of atomic force microscopy (AFM) for surface morphology study b) contact and tapping or non-contact AFM modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

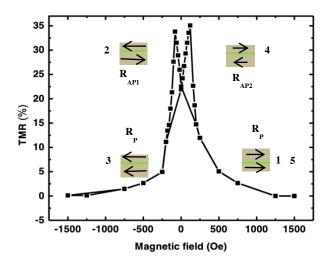

| Figure 2.10 TMR measurement procedure for magnetic tunnel junctions using physical property measurement system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

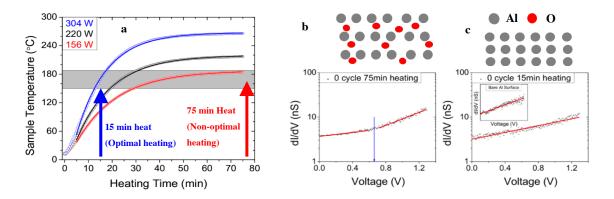

| Figure 3.1 a) Measured sample temperature as a function of exposure time in an ALD reaction chamber which has been preheated at the given wattages. The solid lines are fits to the data STS b) $dI/dV$ spectra are plotted for an Al sample after 75 min heating in the ALD chamber and (c) after 15 min of heating. The arrows (blue) depict the TB height, calculated as the intersection of the fit lines (red). Diagrams (top) illustrate the expected surface as seen by the STM tip. The insert in (c) is the $dI/dV$ spectrum of a sample that was directly transferred to the STM chamber after Al sputtering. This figure is adapted from reference [89] |

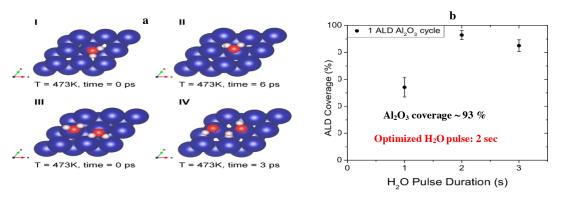

| Figure 3.2 (a) AIMD simulations are shown for H <sub>2</sub> O adsorption onto an Al (111) surface. When only one is present on the Al surface, dissociation is thermodynamically unfavorable (I, II). However, when are in close proximity, dissociation into -OH and is nearly instantaneous (III, IV). (b) The percentage of the Al surface which had a barrier height consistent with ALD Al <sub>2</sub> O <sub>3</sub> after one ALD Al <sub>2</sub> O <sub>3</sub> cycle is shown verses a variable initial H <sub>2</sub> O pulse duration from. This figure is adapted from reference [89]                                                                |

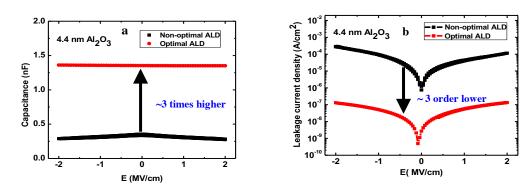

| Figure 3.3 Comparison of a) capacitance and b) leakage current for 4.4 nm Al/Al <sub>2</sub> O <sub>3</sub> /Al MIM device fabricated with optimal (red) and non-optimal (black) condition with maximum applied electric field 2 MV/cm                                                                                                                                                                                                                                                                                                                                                                                                                             |

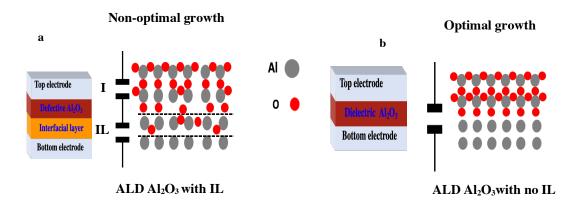

| Figure 3.4 Schematic showing the comparison non-optimal with the formation of interfacial layer in series with defective dielectric and optimal growth of ALD Al <sub>2</sub> O <sub>3</sub> on metal surface resulting high quality dielectric.                                                                                                                                                                                                                                                                                                                                                                                                                   |

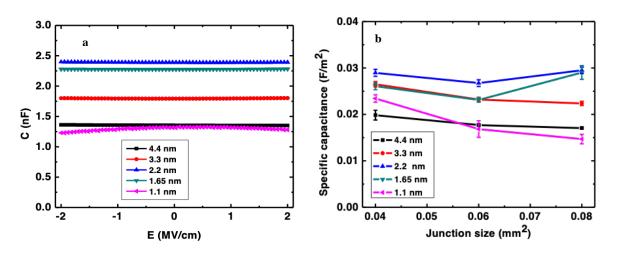

| Figure 3.5 Variation of a) capacitance and b) specific capacitance with junctions areas for MIM Al/ALD Al <sub>2</sub> O <sub>3</sub> (4.4-1.1 nm)/Al MIM capacitors fabricated using optimal ALD conditions 58                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

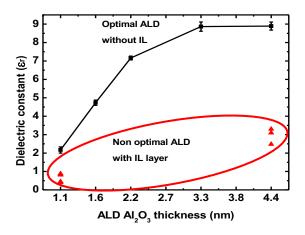

| Figure 3.6 Variation dielectric constant with thickness of ALD Al <sub>2</sub> O <sub>3</sub> (1.1-4.4 nm) capacitors fabricated using optimal (black) indicating close to bulk $\varepsilon_r \sim 8.9$ at 3.3-4.4 nm and non-optimal (red) indicating ) $\varepsilon_r \sim 2.5$ -3.3 at 4.4 nm ALD parameters                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

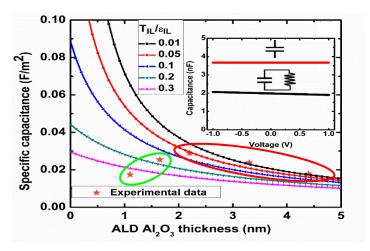

| Figure 3.7 Comparison experimentally obtained specific capacitance data for ALD Al2O3 dielectric with the modelling based in the assumption that interfacial layer capacitance capacitor is connected in series with an ideal capacitor for ALD Al2O3 films. The inset shows an experimental verification of modelling showing the decrease in the measured capacitance for a standard 3.7 nF capacitor when connected in parallel with a 30 $\Omega$ resistor                   |

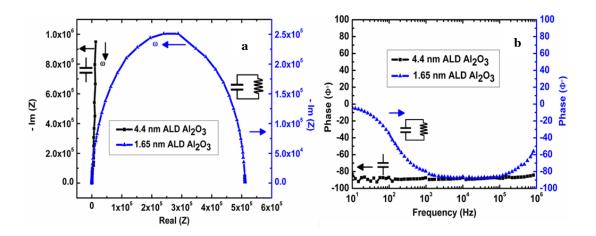

| Figure 3.8 AC impedance measurement a) A Nyquist plot and b) a phase variation with frequency measured on 40 cycle (4.4nm, black)) and 15 cycle (1.65 nm, blue) ALD Al2O3 MIM capacitors                                                                                                                                                                                                                                                                                         |

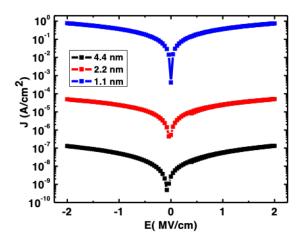

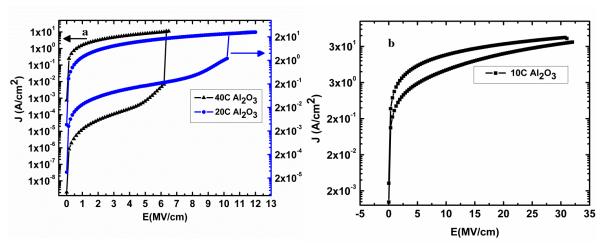

| Figure 3.9 Leakage current density vs. electric field ( <i>J-E</i> ) for MIM capacitors fabricated using optimal ALD condition for 4.4, 2.2 and 1.1 nm ALD Al <sub>2</sub> O <sub>3</sub> dielectric film                                                                                                                                                                                                                                                                        |

| Figure 3.10 Leakage current density vs. electric field for 4.4 nm Al <sub>2</sub> O <sub>3</sub> before (black) and after (blue) soft dielectric breakdown where dielectric can recover its original I-V after removal of external field.                                                                                                                                                                                                                                        |

| Figure 3.11 Leakage current density vs. electric field after hard dielectric breakdown for (a) 4.4 (black) and 2.2(blue) nm ALD Al <sub>2</sub> O <sub>3</sub> and (b) 1.1nm ALD Al <sub>2</sub> O <sub>3</sub> cycles                                                                                                                                                                                                                                                           |

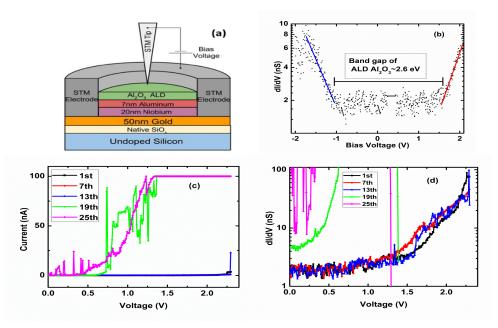

| Figure 3.12 In Situ Scanning tunnelling spectroscopy for the ALD $Al_2O_3$ tunnel barrier (a) A schematic for the sample mounting scheme (b) A representative of $dI/dV$ spectra with blue and red lines are bisquare method linear fits to the valence band and the conduction band respectively (c) The breakdown characteristics with $I-V$ and (d) corresponding $dI/dV$ spectra where the bias voltage was sequentially ramped up and down with a fixed tip-sample distance |

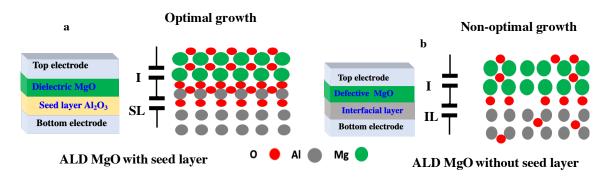

| Figure 4.1 Growth mechanism for a) ALD MgO with ALD Al <sub>2</sub> O <sub>3</sub> (dielectric with dense -OH nucleation) with seed layer Al <sub>2</sub> O <sub>3</sub> showing perfect dielectric growth b) ALD MgO without seed layer (dielectric with less -OH nucleation and possibility of pinholes for ALD MgO without Al <sub>2</sub> O <sub>3</sub> seed layer forming interfacial layer resulting defective dielectric showing perfect dielectric growth.              |

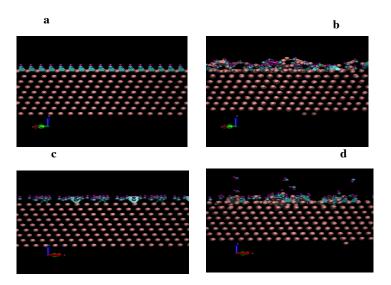

| Figure 4.2 a) and b) Side view of the atomic trajectories for the case of 'orderly placed' (representing -OH on the Al(111) surface after 0 and 25,000 fs respectively; c) and d) Side view of the atomic trajectories for the case of 'disorderly placed' (representing -OH on the Al(111) wetting layer after 0 and 25,000 fs respectively                                                                                                                                     |

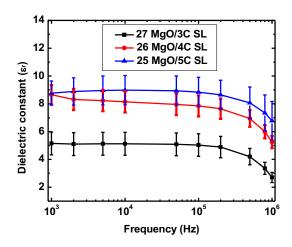

| Figure 4.3 Dielectric constant variation with frequency for total thickness of 3.3 nm MgO/SL with variation of seed layer thickness 0.33-0.55 nm (or 3-5 ALD cycles)                                                                                                                                                                                                                                                                                                             |

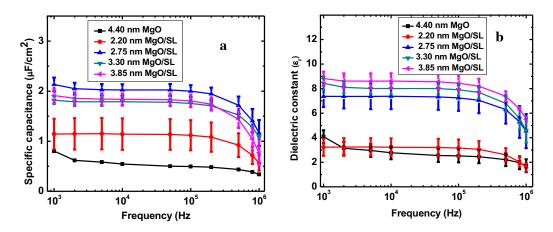

| Figure 4.4 Variation of a) Specific capacitance and b) dielectric constant with frequency for Al/MgO(2.20-3.85 nm)/SL (0.55 nm)/Al and Al/MgO (4.40) nm /Al MIM capacitor using previous shadow mask method.                                                                                                                                                                                                                                                                     |

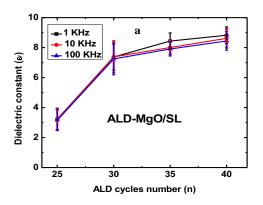

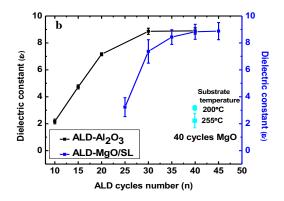

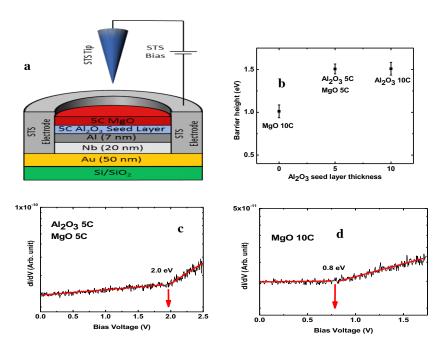

| barrier heights for TBs of total thickness 10 C using different amounts of Al <sub>2</sub> O <sub>3</sub> in their compositions. c) representative <i>dl/dV</i> spectrum taken on a 5 C Al <sub>2</sub> O <sub>3</sub> /5 C MgO TB and d) a representative <i>dl/dV</i> spectrum taken on a 10 C MgO TB                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 4.5 Variation of a) dielectric constant for ALD MgO/SL with ALD cycles number at different frequencies (1, 10 and 100 KHz) and b) Comparison of ALD Al2O3 dielectric (black) reported in a previous paper1 with ALD MgO with SL (ALD MgO/SL) (blue) and ALD MgO wo-SL) (cyan) deposited at substrate temperature 200 and 255 °C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

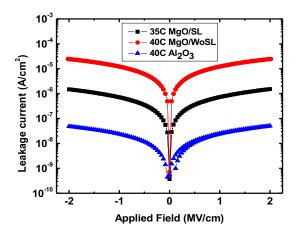

| Figure 4.7 Comparison of leakage current for total 4.40 nm ultrathin ALD dielectric film with ALD Al <sub>2</sub> O <sub>3</sub> , ALD MgO/SL and ALD MgO/WoSL for MIM capacitor using log plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 4.6 a) Diagram of <i>in situ</i> deposited seed layer and TB for STS analysis b) Comparison of barrier heights for TBs of total thickness 10 C using different amounts of $Al_2O_3$ in their compositions. c) representative $dI/dV$ spectrum taken on a 5 C $Al_2O_3/5$ C MgO TB and d) a representative $dI/dV$ spectrum taken on a 10 C MgO TB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

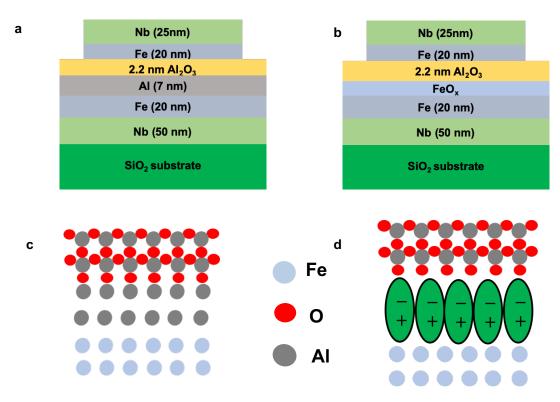

| wetting layer. The schematic description of the M-I interface for: c) ALD Al <sub>2</sub> O <sub>3</sub> /Al (7nm) with pure dielectric ALD Al <sub>2</sub> O <sub>3</sub> and d) Al <sub>2</sub> O <sub>3</sub> /Fe with a ferroelectric FeOx interface in series with ALD Al <sub>2</sub> O <sub>3</sub> dielectric layer                                                                                                                                                                                                                                                                                                                                                                                         | Figure 4.7 Comparison of leakage current for total 4.40 nm ultrathin ALD dielectric film with ALD Al <sub>2</sub> O <sub>3</sub> , ALD MgO/SL and ALD MgO/WoSL for MIM capacitor using log plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

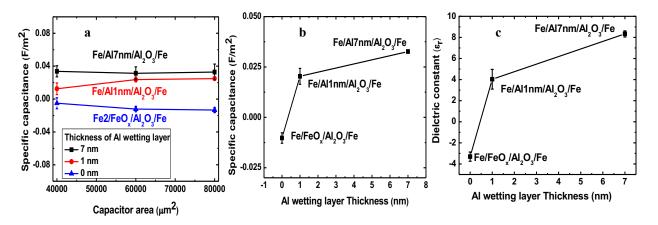

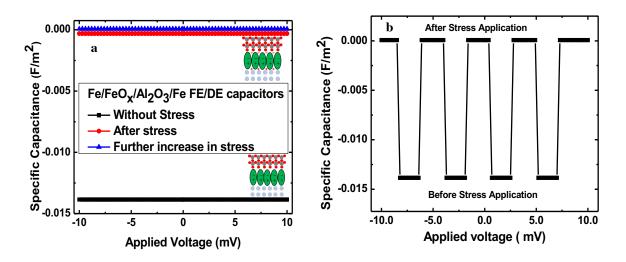

| 200x300 and 200x400 μm2 b) specific capacitance with thick 7 nm Al wetting layer, thin 1 nm Al wetting layer and without Al wetting layer and c) dielectric constant ( $\epsilon_r$ ) for MIM capacitor for 20 cycles Al <sub>2</sub> O <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figure 5.1 Schematic of the MIM capacitors with: a) a thick 7 nm Al wetting layer; and b) no Al wetting layer. The schematic description of the M-I interface for: c) ALD $Al_2O_3/Al$ (7nm) with pure dielectric ALD $Al_2O_3$ and d) $Al_2O_3/Fe$ with a ferroelectric FeOx interface in series with ALD $Al_2O_3$ dielectric layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

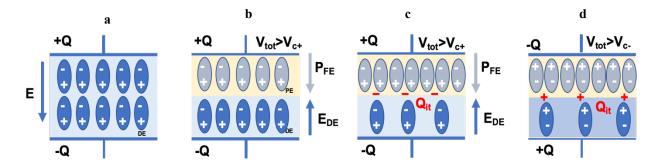

| application of external electric field i.e. blue ovals represent electrical dipoles aligned under E field b) Fe/Al/FeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /Fe Ferroelectric/dielectric (FE/DE) bilayer capacitor with blue and light blue ovals represent electrical dipoles and polarization in aligned under E field at $V_{tot} > V_{c+}$ before switching; c) Increase in FE capacitance due to external E field or via external deformation leading to increase in interfacial charges at FE/DE interface at $V_{tot} > V_{c+}$ after switching d) Leakage current assisted polarization switching with change in interfacial charges in FE/DE bilayer capacitors $V_{tot} > V_{c-}$ after switching | Figure 5.2 Variation of a) specific capacitance with three different junction areas 200x200, 200x300 and 200x400 $\mu$ m2 b) specific capacitance with thick 7 nm Al wetting layer, thin 1 nm Al wetting layer and without Al wetting layer and c) dielectric constant ( $\epsilon_r$ ) for MIM capacitor for 20 cycles Al <sub>2</sub> O <sub>3</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| and under the application of external force showing change in capacitance and b) dynamic response curve for MIM capacitor before and after application of external force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Figure 5.3 Working principle of a) Fe/Al/FeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /Fe dielectric (DE) capacitor under application of external electric field i.e. blue ovals represent electrical dipoles aligned under E field b) Fe/Al/FeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /Fe Ferroelectric/dielectric (FE/DE) bilayer capacitor with blue and light blue ovals represent electrical dipoles and polarization in aligned under E field at $V_{tot} > V_{c+}$ before switching; c) Increase in FE capacitance due to external E field or via external deformation leading to increase in interfacial charges at FE/DE interface at $V_{tot} > V_{c+}$ after switching d) Leakage current assisted polarization switching with change in interfacial charges in FE/DE bilayer capacitors $V_{tot} > V_{c-}$ after switching |

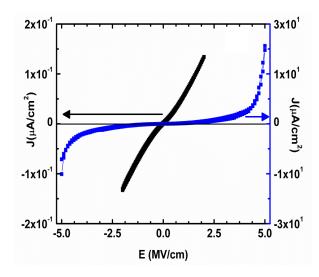

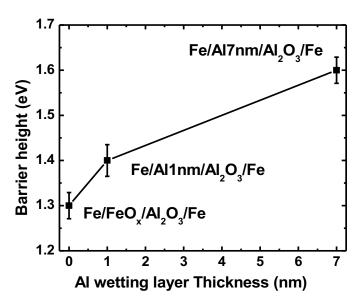

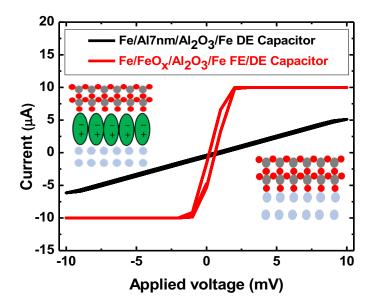

| with different thickness of Al wetting layer made using scanning tunnelling spectroscopy 102 Figure 5.6 Comparison of I-V curve between MIM with 7 nm Al Fe/Al/Al <sub>2</sub> O <sub>3</sub> /Fe DE and without Al wetting layer Fe/FeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /Fe FE/DE                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 5.4 a) Comparison of C-V curve for MIM capacitor without Al wetting layer as measured and under the application of external force showing change in capacitance and b) dynamic response curve for MIM capacitor before and after application of external force                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Al wetting layer Fe/FeO <sub>x</sub> /Al <sub>2</sub> O <sub>3</sub> /Fe FE/DE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 5.5 Barrier height comparison for MIM half-cell made for three different configurations with different thickness of Al wetting layer made using scanning tunnelling spectroscopy 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

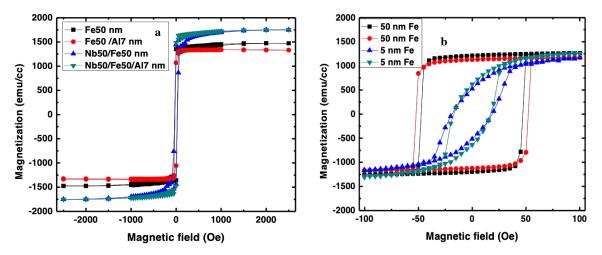

| nm), Fe (50 nm)/Al (7 nm), Nb (50 nm)/Fe (50 nm) and Nb (50 nm) /Fe (50 nm)/Al (7 nm) b) M-H loop for Fe (50 nm) and Fe (5 nm) showing the coercive field dependent on the Fe film                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 5.6 Comparison of I-V curve between MIM with 7 nm Al Fe/Al/Al $_2$ O $_3$ /Fe DE and without Al wetting layer Fe/FeO $_x$ /Al $_2$ O $_3$ /Fe FE/DE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Figure 6.1 Magnetization vs magnetic field (M-H) loop for multi-layered structure with a) Fe (50 nm), Fe (50 nm)/Al (7 nm), Nb (50 nm)/Fe (50 nm) and Nb (50 nm)/Fe (50 nm)/Al (7 nm) b) M-H loop for Fe (50 nm) and Fe (5 nm) showing the coercive field dependent on the Fe film thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

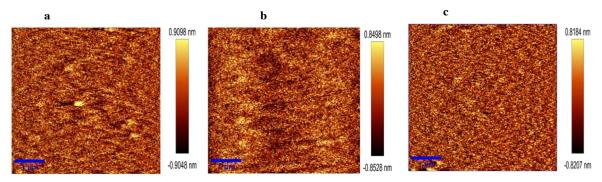

| Figure 6.2 AFM images of a) Fe (50 nm), b) Nb (50 nm)/Fe (50 nm), and c) Nb (50 nm)/Fe (50 nm)/Al (7 nm) thin films deposited on SiO2. The scale bar is $1.0 \mu\text{m}$                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

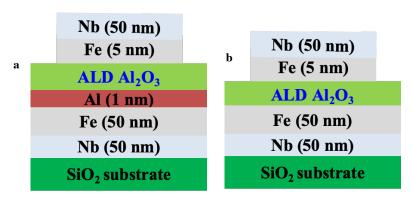

| Figure 6.3 Schematic for the device structure for MTJs fabrication a) with 1 nm Al wetting layer and b) without Al wetting layer                                                                                                                                                                                                                                                          |

| Figure 6.4 Scanning tunnelling spectroscopy to study <i>dI/dV</i> spectra for 5C-ALD Al <sub>2</sub> O <sub>3</sub> a) with 1 nm Al wetting layer and b) without Al wetting layer                                                                                                                                                                                                         |

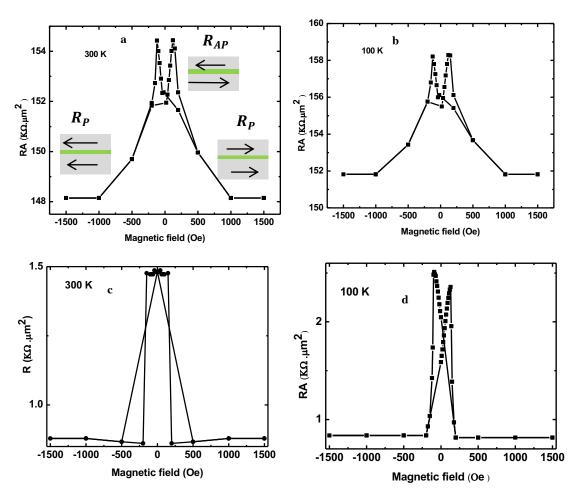

| Figure 6.5 Temperature dependence hysteresis loops of RA vs magnetic field for Nb (50 nm)/Fe (50 nm)/Al (1 nm)/ ALD $Al_2O_3$ / Fe (5 nm)/Nb (50 nm) MTJs structure with Al wetting layer at (a) at 300 K and (b) 100 K respectively and Nb (50 nm)/Fe (50 nm)/ALD $Al_2O_3$ /Fe (5 nm)/Nb (50 nm) MTJs structure at (c) at 300 K and (d) 100 K without Al wetting layer respectively 115 |

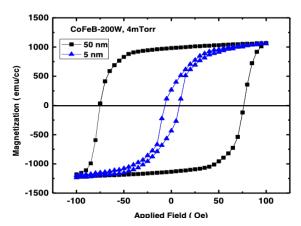

| Figure 6.6 Hysteresis loop for CoFeB ferromagnetic material with 50 and 5 nm thickness characterized using vibrating sample magnetometer showing feasibility for fabrication of spin valve MTJs structure                                                                                                                                                                                 |

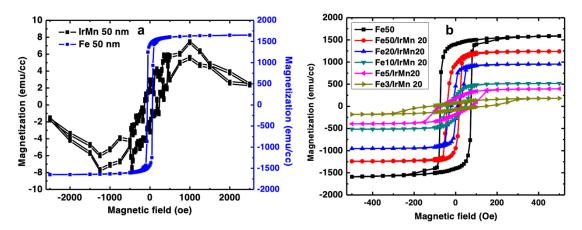

| Figure 6.7 Hysteresis loop comparison for a) Fe (50 nm) and IrMn (50 nm) layers; b) Fe(50-3 nm)-IrMn (20 nm) bilayer structure with different thickness of FM material for fabrication of exchanged bias MTJs respectively                                                                                                                                                                |

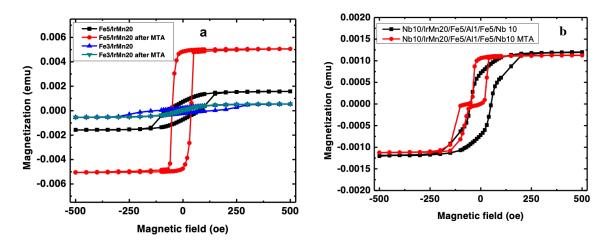

| Figure 6.8 Hysteresis loop comparison for a) Fe(5nm) /IrMn (20 nm) and Fe (3 nm)/IrMn (20 nm) for bilayer structure before and after magnetic thermal annealing; and b) Nb(10 nm)/IrMn (20 nm)/Fe(5 nm) /Al (1 nm)/Fe (5 nm)/ Nb (10 nm) before and after magnetic thermal                                                                                                                |

| annealing for fabrication of exchanged bias MTJs respectively                                                                                                                                                                                                                                                                                                                             |

## **List of Tables**

| Table 1.1 Progress made in MBE fabricated MTJ.                                                                     | 21  |

|--------------------------------------------------------------------------------------------------------------------|-----|

| Table 1.2 Recent progress in dielectric property of ALD Al <sub>2</sub> O <sub>3</sub> dielectric MIM capacitors w | ith |

| thickness of dielectric in range from few tens of <i>nm</i> to few hundreds of <i>nm</i> with their                |     |

| corresponding parameters.                                                                                          | 29  |

## **List of Symbols**

TB Tunnel barrier

TJ Tunnel junction

MIM Metal-insulator-metal

NVM Non-volatile memory

M-I Metal insulator

FinFET Fin field effect transistor

JJ Josephson junction

MTJ Magnetic tunnel junction

CMOS Complementary metal-oxide-semiconductor

GMR Giant magnetoresistance

TMR Tunnelling magnetoresistance

FM Ferromagnetic materials

GGA Gate all around

$J_c/J$  Critical current density/ Leakage current density

DOS Density of states

$E_f / E_b$  Fermi energy/ Barrier height

ALD Atomic layer deposition

IL /SL Interfacial layer/Seed layer

MRAM Magnetoresistive Random-Access Memory

FE/DE Ferroelectric/Dielectric

## **Chapter 1** Introduction

Since the early 1970's, Moore's law is the driving principle behind the advancement in the semiconductor industry that predicted the density of transistors in an integrated circuit double approximately every two years [1]. Following this law, the size of transistors decreased from 10  $\mu m$  to 10 nm over the past few decades, with 7 and 5 nm technology are predicted to be prominent in future electronic devices [2]. Consequently, SiO<sub>2</sub> gate dielectric has decreased its thickness from hundreds of nm to few nm [3]. The further miniaturization of microelectronics towards the reduced dimensions demands ultrathin dielectric (few nm to sub-nm thickness) in range of 1-2 nm or below [4-13]. The applications requiring such ultrathin high quality dielectrics include metal/insulator/metal (MIM) architectures [10, 12, 13] and tunnel junctions (TJs) [9, 14-18]. As technology approaches the end of Moore's law and beyond the control over metal-insulator (M-I) interface with atomic precision, low defect density, and uniformity have become critically important for future microelectronics device applications [19].

### 1.1 Metal-Insulator-Metal Architecture

MIM architecture is the simplest trilayer structure with insulating barriers (like Al<sub>2</sub>O<sub>3</sub>, MgO, HfO<sub>2</sub>, etc.) in the few nanometers thicknesses range sandwiched between two metal electrodes. These architectures are the building blocks for many microelectronic circuits like gate dielectrics in complementary metal-oxide-semiconductor (CMOS) technology [10, 12, 13]. CMOS technologies have been the driving principle for the innovation and advancement in logic-based devices over

the past decade due to a significant reduction in the dimension of gate dielectric. Along with the reduction in the gate dimension, SiO<sub>2</sub> dielectric is approaching its physical limitations below 1.3 nm thickness due to considerably increased leakage current density (J) of 1-10 A/cm² that occurs primarily due to the difficulties in controlling the defects in ultrathin SiO<sub>2</sub> [3]. This not only prevents achievement of the required gate voltages for device operation, but also exceeds the required threshold of ~10<sup>-3</sup> A/cm² for high-performance, low-power consumption microprocessors by several orders of magnitude [3, 20-23]. The difficulties in down-scaling the SiO<sub>2</sub> dielectric gates have motivated an intensive research on high-K dielectric materials [24, 25]. Considering the higher dielectric constants ( $\varepsilon_{Hik}$ ) than that of SiO<sub>2</sub> ( $\varepsilon_r \sim 3.9$ ), the high-K dielectric can achieve an effective oxide thickness (EOT= $t_{HiK} \cdot 3.9/\varepsilon_{Hik}$ ) in the range ~1-2 nm, with a larger thickness  $t_{HiK}$  that reduces J [26-28]. For example, in order to achieve an equivalent SiO<sub>2</sub> dielectric of thickness  $t_{SiO2} \sim 1.5$  nm with the specific capacitance given as ( $Co = C/A = \varepsilon_o 3.9/t_{SiO2}$ ), the corresponding thickness of high-K material HfO<sub>2</sub> with  $\varepsilon_{Hik} \sim 20$  is ~ 7.7 nm for same value of Co, which results in the lower  $J \sim 10^{-5}$  A/cm² [22].

Using high-K dielectric material new architectures designs like fin field-effect transistors (FinFETs) have been developed that uses a conformal spacer gate as shown in Figure 1.1(a) to decrease power consumption and efficiently control switching on/off operation [26-28]. Compared to a standard planar transistor, this allows for better performance and voltage scaling as the process node decreased, by minimizing the transistor limitations like high leakage and high-power consumption [26-28]. Despite the progress made in ultrathin high-K gate dielectric of a few *nm* in

thickness, further reduction of their thickness remains challenging due to the difficulties in controlling defects, which is similar to the SiO<sub>2</sub> dielectric case [26, 28]. Recently, vertically aligned nanowires have been used in the development of three-dimensional (3D) gate architectures to keep up requirement of low power and high performance devices with scalability [29].

Applications requiring ultrathin high quality dielectric include the Josephson junctions (JJs) for quantum computing. When two superconducting layers are brought together within a few nanometers range, the superconductor wave functions couple together, allowing Cooper pairs, which are paired electrons to tunnel through the ultrathin barrier as in Figure 1.1(b). For quantum computing, the superposition of quantum states must have long coherence times. If the qubits couple too strongly with defects, then the entangled state will be lost, and the computation cannot be performed. While JJ qubits are entangled, their short coherence times have been problematic due to two-level fluctuations (TLFs). Most studies shows that defects in the dielectric materials particularly oxygen vacancies and interstitials in the tunnel barrier (TB), are the primary source of TLFs [30]. This decoherence in JJs is a major challenge, that results in the collapse of qubits wave function before computation completes [30]. This requires better control over the fabrication process with stoichiometric and defect free ultrathin high quality dielectric critical for improving the performance of JJs, which is challenging using current state of the art processes [31].

Another TJs application includes magnetic tunnel junctions (MTJs), which uses an ultrathin insulator sandwiched between two ferromagnetic (FM) materials that allow spin polarized electrons to tunnel through the barrier as shown in Figure 1.1(c). The most important property of

MTJs is that the spin dependent current depends on the relative orientation of the magnetization in ferromagnetic magnetic (FM) layers [31, 32]. In MTJs, defective oxides lead to the scattering and spin flip of spin polarized electrons passing through the FM layer. The oxygen vacancies and defects are unavoidable in the ultrathin dielectric films fabricated using the thermal oxidation process [31]. These vacancies and defects can effect the conductance by non-resonant scattering of electrons causing a substantial reduction of magnetoresistance (TMR). The fabrication of high quality TB with reduced oxygen vacancies and defects concentration results in the less scattering and coherent spin tunnelling resulting better TMR. The current approaches in achieving the logic functionality with MTJs include designing an integrated CMOS and MTJ circuit, where CMOS devices are used for implementing the required intermediate read and write circuitry. MTJ based logic has great potential because of the non-volatility, practically unlimited endurance, CMOS compatibility, and fast switching speed. By direct communication between spin-transfer torque (STT) in MTJs, several realizations of intrinsic logic-in-memory circuits have been demonstrated for which the MTJ devices are used simultaneously as fast access nonvolatile magnetic memory and computing elements [33-35].

#### FinFETs/ Tri-Gate Magnetic tunnel Junction (MTJ) Josephson Junction (JJ) ALD Gate Ferromagnet (A) Superconductor (A)(\*) Spin Copper Insulator polarized e Insulato pair tunneling tunneling Superconductor (\*) Ferromagnet (A) (A)

Figure 1.1 Schematic of metal-insulator-metal architecture a) conformal ultrathin ALD sidewall spacer gate dielectric in field effect transistors (FinFETs) or Tri-Gate for complementary metal-oxide-semiconductor (CMOS) technology b) Josephson Junction with ultrathin dielectric sandwich between two superconducting electrode with Copper pair tunnelling and c) Magnetic Tunnel Junctions with ultrathin dielectric sandwich between two ferromagnetic electrode with spin polarized electron tunnelling.

Navigating these trends of continuing miniaturization of devices, there is an increasing demand for the fabrication of ultrathin TB with low J, low defect concentration and uniform over the large wafer to increase device' performances as demanded by today's technological advancement. One critical issue with current state of the art thermal oxidation processes is the presence of defects and pinholes at ultrathin thickness, which is unavoidable [31]. Another challenge is precise control over dielectric thickness, its quality and interfaces with metals. However, the precision thickness control in sub nanometres range without pinholes and defects free uniform TB is demanded for future applications. Thus, the M-I interface needs to be controlled well to obtain high quality ultrathin dielectric for potential application in future microelectronics.

### 1.2 Gate Dielectric for CMOS

There are several device architectures developed to address the critical issue with the increase in leakage current with a corresponding reduction in the dimension of gate dielectric approaching its physical limitations [20, 21]. Among these, FinFETs architecture with uniform ultrathin spacer gate dielectric has been developed to increase the contact area between the channel of the transistor and the gate. By scaling in a vertical direction, this allows faster switching times and higher *J*. However, like planar transistors, FinFETs transistors will eventually reach a point where they cannot scale further as process technology nodes shrink. To scale, the contact area between the channel and the gate needs to increase. The way to implement this is to use a gate-all-around (GAA) architecture. The GAA design allows transistors to stack vertically, rather than laterally. Three-dimensional (3D) tri-gate fin transistors have been used for 14 *nm* technology node that deliver incredible performance, power, density, and better cost per transistor. This provides manufacturing of a wide range of high performance to low power devices. This advancement in 3D architecture will continue with future complex device architecture demanding the fabrication of uniform, conformal, pinhole and defect-free ultrathin gate dielectrics to meet the requirement of low *J*.

Following the exponential dependence in technology node as predicted by Moore's Law, the cost of a single transistor on silicon chip during the last few decades has decreased more than a million-fold, as the number of devices on a single chip have also increased more than a million-fold. As the further advancement in microelectronics continues devices require a reduction in their dimensions. In CMOS technology, there is a continuing drive to shrink silicon devices that requires gate oxide layers with thickness ~1 nm or below [20, 21]. Future scaling has been the next important question in today's semiconductor industry, especially because numerous challenges arise from both the device physics and manufacturing capabilities perspective. The traditional

scaling based on the reduction in the physical dimensions of CMOS transistors, with simultaneous reduction of supply voltages and dissipated power, is reaching its limits. Intel introduced its advanced manufacturing process technology to help deliver the expected benefits of Moore's Law popularly known as the "Tick" cycle [36]. However, electron at this thickness produces high leakage current and device instability [20, 21]. The deposition of ultrathin uniform SiO<sub>2</sub> films and maintaining the insulating properties has also become increasingly difficult. High-K dielectric materials are currently being investigated to achieve higher capacitances with thicker films to obtain low leakage current, a high dielectric constant ( $\varepsilon_r$ ), and high breakdown strength to achieve high capacitance densities [26, 27]. The continuous application in today's process technologies includes the next big innovation in processor microarchitecture known as the "Tock" cycle. This "Tick-Tock" model still allows to follow with the empirical Moore's Law [36]. However, this decreasing size comes at an increasing cost, so most recent technology generations do not offer much advantage in terms of cost per transistor, or cost per function, when compared to the previous nodes. Intel recently announced its focus is now shifted on "Process-Architecture-Optimization". This includes the introduction of new materials and innovative techniques for the optimization of device performance. The efficient control in the gate dielectric is the main reason for the success of CMOS technology that allows the integration of more than a billion transistors on a chip to make portable computers and smartphones viable. However, the increase in dissipation power density, especially standby power, has resulted in a trade-off between performance/speed and lowpower requirements.

As Moore's law is approaching its physical limitations due to its increased energy consumption and complexity in design, the reduction in the size of transistors cannot keep up as demanded by today's technological advancement. The International Technology Roadmap for Semiconductors predicts that the semiconductor technology will reach its last generation by the year 2025 [37]. In order to address these problems, the new paradigm called "More than Moore" is commonly used in today's technology [38]. Ultimately, the devices that use charge as the fundamental element to store information will soon reach its power and capacity limitations. The new architecture and functionality with reduced device dimension demand high quality ultrathin dielectric. These results in an increase in coherent tunnelling improving the device performances as demanded by current technological advancement.

## 1.3 Magnetic Tunnel Junction

Spintronics is a relatively new concept that utilizes the spin degree of freedom of electrons to control the flow of electrical current expanding the power and capability of electronic devices. Spin-polarized current can be generated by exploiting the influence of spins on the transport properties of electrons in FM, which has an imbalance in density of states (DOS) for majority and minority carriers due to spin-orbit interaction [39]. With the advancement in thin film deposition techniques, such as sputtering and molecular beam epitaxy (MBE), the fabrication of multilayered structures composed of thin individual layers in the order of nanometres became feasible. These layers have thickness smaller than the mean free path of electrons that helped to realize new quantum mechanical phenomenon. Fert *et. al.* [40] and Grunberg *et. al.* [41] in 1988, first

discovered that the resistance of Fe/Cr/Fe multilayer structure changed based on the relative orientation of the two layers leading to the discovery of giant magnetoresistance (GMR). The orientation of FM layers depends on the direction of local spin polarized electrons with the majority carriers in the FM layers. Figure 1.2(a) shows anti-parallel orientation of two FM layers with majority spin carriers (i.e. red in top layer and blue in bottom layer) separated with non-magnetic layer (yellow). The majority carriers in both layers suffer large scattering from either of these layers. This results in a low spin polarized current or high resistance through the multilayer structure. However, when orientation of these layers is parallel (i.e. blue electrons) as in Figure 1.2(b), only minority carrier (i.e. red electrons) suffer scattering from both layers resulting in high majority blue spin polarized current or low resistance through the multilayer structure. This relative change in the resistance between parallel and anti-parallel orientation is known as GMR. The orientation of these layers can be changed by the application of the external magnetic field. These GMR structures were later commercialized to make magnetic sensors with an increase in the areal density of information stored on the hard disk drives.